基于以太网控制器NC28J60和HR901170A实现以太网通信

描述

作者:周晓阳,程红,张晓媛

NC28J60是Microchip Technology(美国微芯科技公司)近期推出的28引脚独立以太网控制器。

在此之前,嵌入式系统开发可选的独市以太网控制器都是为个人计算机系统设计的,如RTL8019、AX88796L、DM9008、CS8900A、LAN91C11l等。这些器件不仅结构复杂,体积庞大,且比较昂贵,目前市场上大部分以太网控制器的封装均超过80引脚,而符合IEEE 802.3协议的ENC28J60只有28引脚,既能提供相应的功能,又可以大大简化相关设计,减小空间。

1 结构和功能

采用业界标准串行外设接口(SPI)的以太网控制器ENC28J60具有以下主要特征:

◆符合IEEE 802.3协议。内置lOMbps以太网物理层器件(PHY)及媒体访问控制器(MAC),可按业界标准的以太网协议可靠地收发信息包数据。

◆具有可编程过滤功能。特殊的过滤器,包括Microchip的可编程模式匹配过滤器,可自动评价、接收或拒收Magic Packet,单播(Unicast)、多播(Multicast)或广播(Broadcast)信息包,以减轻主控单片机的处理负荷。

◆lOMbps SPI接口。业界标准的串行通信端口,使得低至18引脚的8位单片机也具有网络连接功能。

◆可编程8KB双端口SRAM缓冲器。以高效的方式进行信息包的存储、检索和修改,以减轻主控单片机的内存负荷。该缓冲存储器提供了灵活可靠的数据管理机制。

2 硬件设计

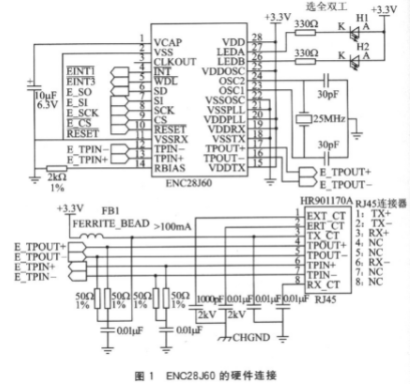

ENC28J60的硬件设计需要注意复位电路,时钟振荡器,振荡器启动定时器,时钟输出引脚,变压器、终端和其他外部器件,输入/输出电平等几个方面。(图l可供参考)2.1 复位电路ENC28J60有上电复位(Power-on Reset)功能,RESET引脚上的低电平使ENC28J60进入复位模式;RKSlET引脚内部有弱上拉电阻。ENC28J60的硬件连接如图l所示。

2.2 时钟振荡器

ENC28J60需要一个25MHz的晶振,接在OSCl和OSC2脚上;也可由外部时钟信号来驱动。此时3.3V的外部时钟接在OSCl脚上,OSC2断开或者通过一个电阻接地来降低系统噪声。

2.3 振荡器启动定时器

ENC28J60内部有一个振荡器启动时钟OST(Oscillator Start-upTimer),上电7500个时钟周期(300μs)。OST期满后内部的PHY方能正常工作。这时不能发送或者接收报文。上位机可通过检测ENC28J60内部ESTAT寄存器中的CLKRDY位的状态来决定是否可设置发送或接收报文。

需要注意的是,当ENC28J60上电复位或者从Power-Down模式下唤醒时,必须检测ESTAT寄存器中的CLKRDY是否置位。只有CLKRDY置位后才能发送、接收报文,访问相关寄存器。

2.4 时钟输出引脚

CLKOUT引脚可为系统巾的其他设备提供时钟源。上电后CLKOUT引脚保持低电平,复位结束后OST计数。OST期满后,CLKOUT输出频率为6.25MHz的时钟。

时钟输出功能通过ECOCON寄存器禁止、调整和使能。时钟输出可设置为1、2、3、4、8分频,上电后默认为4分频。ECOCON寄存器配置改变以后,CLKOUT引脚有80~320ns的延迟(保持低电平),然后按照设定输出固定频率的时钟信号。

软什或者RESET引脚上的复位信号不会影响ECOCON寄存器的状态。Power-Down模式也不会影响时钟的输出。当禁止时钟输出时,CLKOUT引脚保持低电平。

2.5 变压器、终端和其他外部器件

为了实现以太网接口ENC28J60,需要几个标准的外部器件:脉冲变压器、偏置电阻、储能电容和去耦电容。

差分输入引脚(TPIN+/TPTN-),需要一个1:1变比的脉冲变压器来实现10BASE-T。差分输出引脚(TPOUT+/TP0UT-),需要一个变比为1:1、带中心抽头的脉冲变压器。变压器需要有2kV或更高的隔离能力,防静电。对变压器的详细要求请参考芯片手册第16章“电气特性”。每个部分都需要通过2个50Ω、精度为1%的电阻和1个0.01μF的电容串联后接地。

笔者采用的是中山汉仁公司的集成以太网隔离变压器RJ45插座HR901170A。

ENC28J60内部的模拟电路需要在RBIAS引脚和地之间跨接1个2kΩ、l%的偏置电阻。部分数字电路工作在2.5V,以降低功耗;ENC28J60内部集成1个2.5V的调节器来产生所需的电压,需在VCAP引脚和地之间接1个10μF的电容保证供电的稳定性(该2.5V调节器不是为外部负载设汁的)。

所有的供电引脚(VDD、VDDOSC、VDDPLL、VDDRX、VDDTX)必须接在外部的同一个3.3V电源上;同理,所有的地(VSS、VSSOSC、VSSPLL、VSSTX)必须接在同一个外部地上。每个供电引脚和地之问应当接1个O.1μF的陶瓷电容去耦(电容要尽可能接近供电引脚)。

驱动双绞线接口需要较大的电流,所以电源线应尽可能宽,与引脚的连接尽可能短,以降低电源线内阻的消耗。

2.6 输入输出电平

ENC28J60是一个3.3 V的CMOs器件,但它设计得非常容易统一到5 V系统中去:SPI、CS、SCK,SI输入和RESET引脚一样,都可承受5V电压。当SPI和中断输入与3.3V驱动的CM0S输出不兼容时,可能需要一个单向的电平转换器。74HCT08(四与门),74ACTl25(四三态缓冲器)和许多具有TTL电平输入的5VCMOS缓冲器芯片都可以提供所需的电平转换。

2.7 LED配置

LEDA和LEDB引脚在复位时支持极性自动检测。既可直接驱动LED,又可灌电流驱动。复位时ENC28J60检测LED的连接,并按照PHLCON寄存器的默认设置来驱动。运行过程中的LED极性转换直到下一次系统复位后才能被榆测到。LEDB的连接比较特殊,在复位过程中检测它的连接,决定如何初始化PHCONl寄存器的PDPXMD位。如果LEDB直接驱动LED,则PHCON1.PDPXMD位被清零,PHY工作在半双工模式;如果LEDB吸收反向电流点亮LED,则PHCON1.PDPXMD被置位,PHY工作在全双工模式;如果LEDB没有连接,则PHCONl.PDPXME)复位后的值不确定。这时主控制器必须适当设置该位,以使PHY工作在所需的状态(半双工或全双工)。

3 软件接口

3.1 SPI接口

SPI接口(Serial Penpheral Interface)是一种同步、全双工串行接口,基于主从配置,是一个4线接口 ——主出/从人(MOSI).主人/从出(MISO),串行时钟(SCK),从机选择(SSEL)。

在同一总线上可以有多个主机或者从机,但同一时刻只能有一个主机和一个从机能够进行通信。在一次数据传输过程中,数据是同步进行发送和接收的:主机向从机发送1字节数据,从机也向主机返1字节数据。数据传输原则上是全双工的;但实际上,大多数情况下只有一个方向上的数据流包含有意义的数据。

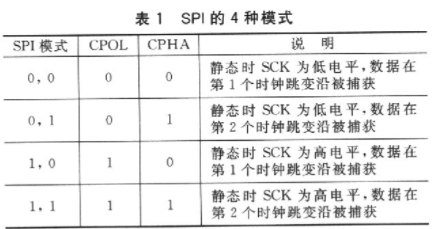

SPI格式的主要特性是SCK信号的无效状态和相位,数据传输的时钟由主机提供。常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CP0L定义SPI串行时钟的活动状态,而CPHA定义相对于从机输出数据位的时钟相位。CPOL和CPHA的设置决定了数据取样的时钟沿。

取决于CPOL和CPHA的设置不同,SPI共有4种模式,如表1所列。

3.2 ENC28J60与单片机的连接

ENC28J60与微控制器MCU的连接是通过SPI实现的,支持10 Mbps。对干没有SPI接口的芯片可通过用I/0口模拟SPI接口的方式实现。ENC28J60仅支持SPI模式O,O。

微控制器可通过SPI接口发送命令,访问ENC28J60的寄存器或读写接收/发送缓冲区,完成相关操作。复位也可通过SPI接口由软件实现,软件复位不影响RESET引脚的状态。

ENC28J60有两个中断输出,分别用于事件中断触发和网络唤醒主机。

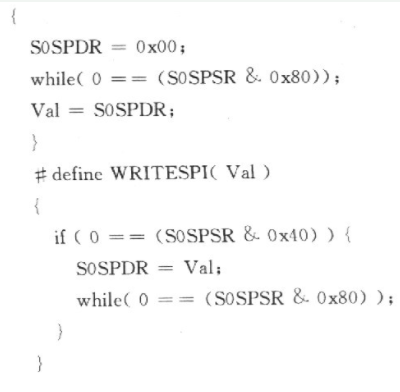

CPU采用LPC2138用宏定义实现SPI口读写操作。SOSPDR为SPI数据寄存器,该双向寄存器为SPI提供发送和接收的数据,发送数据通过写该寄存器提供,SPI接收的数据可从该寄存器读出。SOSPSR为SPI状态寄存器。在对SPI接口进行操作之前需对其初始化。下面给出读/写SPI接口的源代码。

亦可用LPC2138的SSP来连接ENC28J60,需将其设置为SPI模式。应当注意到SSP有8帧的收/发FIFO,如果处理不当将造成读/写错误。因为缓冲区的存在可能破坏读/写ENC28J60的时序。

对于没有SPI接口的单片机可采用普通I/O口模拟的方法实现SPI主机。此时须注意静态时时钟的无效状态和相位,以及输出数据位出现的时间;对ENC28J60操作期间片选必须保持有效(低电平),操作结束后返回低电平。根据ENC28J60的读/写波形很容易写出模拟SPI主机的程序。笔者曾在AT89S5l上实现了模拟SPI主机读/写MCP2515的操作。

4 结论

在LPC2138+ENC28J60+HR901170A平台上实现了以太网通信。相对于其他方案,该系统极为精简。对于没有开放总线的单片机,虽然有可能采用模拟并行总线的方式连接其他以太网控制器,但不管从效率还是性能上,都不如用SPI接口或采用通用I/O口模拟SPI接口连接ENC28J160的方案。

可以看出,ENC28J60是极具特色的独立以太网控制器:SPI接口使得小型单片机也能具有网络连接功能;集成MAC和PHY无需其他外设;具有可编程过滤功能,可自动评价、接收或拒收多种信息包,减轻了主控单片机的处理负荷;内部继承可编程的8KB双端口SRAM缓冲器,操作灵活方便。不足之处为仅支持10BASE-T。

责任编辑:gt

-

深度剖析ENC28J60:独立以太网控制器的设计与应用指南2026-01-05 983

-

实现以太网通信硬件电路方法2023-10-20 1585

-

arduino loar_ENC28J60以太网模块与Arduino的连接方案介绍2021-12-16 1132

-

ENC28J60以太网控制器的电路原理图免费下载2020-12-03 2273

-

ENC28J60以太网模块与Arduino的连接方案介绍2020-11-01 9523

-

stm32有自带的以太网模块与ENC28J60控制器有什么区别?2019-09-04 2621

-

控制器ENC28J60及其接口技术实现以太网通信2019-05-07 3235

-

基于ATMEGA16单片机和ENC28J60以太网控制的外部时钟系统2017-11-08 1534

-

ENC28J60 spi 接口 以太网 网络模块 提供 代码2016-05-17 2175

-

基于ENC28J60以太网控制器及其应用2016-03-01 1318

-

ENC28J60以太网模块【教程】2016-01-12 1355

-

单片机实现以太网通讯硬件设计2011-08-29 1250

-

用51单片机控制RTL8029实现以太网通信2010-09-19 721

-

新型以太网控制器ENC28J60及其接口技术2010-01-19 933

全部0条评论

快来发表一下你的评论吧 !