基于MC12040 ECL鉴相器实现载波跟踪环解调器的应用方案

描述

引言

测控通信系统中经常会使用调相机制,即在发射载波相位中携带信息并传送出去,同时在接收系统接收的载波相位中解调出信息,以达到测控通信的目的。

载波无论是无线电中的哪一个频段,目前总是把高频信号变频到一个低频信号进行解调。通常解调频率都在几兆赫兹至几百兆赫兹的范围内。笔者在进行某工程设计时,需要在70 MHz调相载频上解调出2~100 kHz的BPSK、ASK或FSK信号,以用于比对原始码,其调制度为0.2~1.5。设计时虽然也曾用鉴频器加积分的解调方式实现了信号的解调,但由于调制指数小,调制频率低,使得调制频偏小,鉴频灵敏度有限,而且由于视放增益很高,因而其噪声很大,比对效果不好。因此,研究载波跟踪环解调器就具有一定的实际意义。

1 载波跟踪环解调器原理

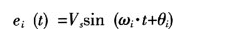

图1是一个基本锁相环路的方框图。该环路包含一个鉴相器,一个低通滤波器和一个压控振荡器。实际上,可以把鉴相器看成一个具有两个输入信号e1(t)和e2(t)的理想乘法器,其输出量为Kme1e2,其中Km是一个常数。假设输入信号是:

如果把环路带宽ωL取得很窄,即ωL《《Ωmin。Ωmin是调制信号的最低角频率。则调制分量被抑制。此时VCO的输出信号为:

比较式(2)与式(1),可以看出,调相后的环路鉴相器输出Vd比未调制时多出了一项,而Kd△φcosΩt正是要解调出的调制信号。

实际上,上述分析结果都是在鉴相器两信号相位差很小时得出的,所以,这种调相解调环适用于1弧度以下的调制,调制度大于1弧度后。其鉴相器输出的解调信号将会产生一些失真。

载波跟踪环解调器的主要特点是解调门限低,但制作复杂,可靠性稍低。

2 载波跟踪环解调器的设计

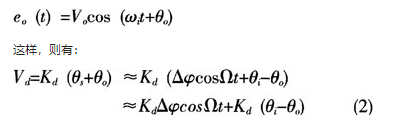

图2是载波跟踪环解调器框图。该环路鉴相器采用了MC12040高速ECL数字鉴相器,所以,两输入正弦信号须转换为ECL电平。此环实际上是二阶锁相环。

2.1 主要参数的确定

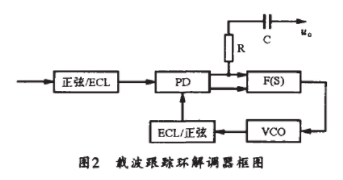

由于最低调制频率是2 kHz,所以,环路带宽BL《2 kHz。一般取ωL≤400 Hz,不宜取得太窄,否则锁定速度将变得很慢。

对于VCXO参数,由于本锁相环所跟踪的频率非常稳定,其准确度稳定度都在10-8以下。所以,其开环频差主要取决于VCXO的温漂和老化。一般在采用泛音晶振温补后,在0~40℃范围内可达到1×10-6,年老化率一般为2×10-6(玻璃壳)。按10年不调整计算,VCXO的漂移为:

f=70×106×10-6+70×106×5×10-6×10=4kHz,因此,VCXO的压控范围为±2kHz,控制电压范围为4~8 V,VCXO的斜率为1 000 Hz/V。

2.2 鉴相器的设计

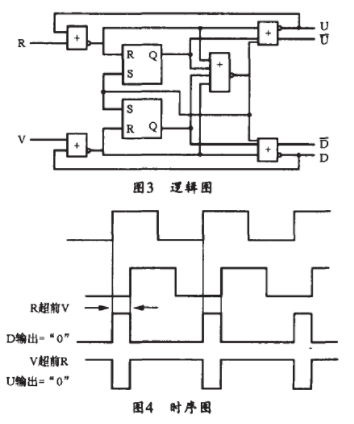

本设计中的鉴相器选用MC12040 ECL高速数字器件,其最高工作频率为80 MHz。器件逻辑如图3所示。MC12040是专为相位比较器而设计的逻辑电路。它能够比较两组数字信号之间的相位“超前”和“滞后”的关系。输出为两波形上升沿之间的时间差的正负脉冲。因为每个周期只有一个上升沿,所以,该鉴相器有±2π弧度的范围。图4是其时序图。

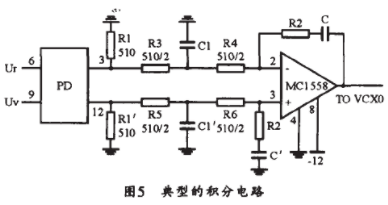

两输入信号(R,V)的相位差大小与输出波形的占空比成一定比例。如将输出波形进行积分,即可获得控制VCXO的模拟量。一般可采用如图5所示的积分电路。

由于鉴相器送出的是窄脉冲,为便于积分,本设计又增加了一节R1/2C1的无源积分器。此种结构的鉴相器增益为0.16 V/rad。

2.3 接口电路

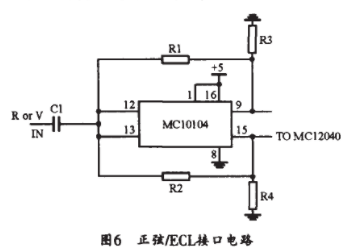

由于MC12040鉴相器是ECL器件,其输人与ECL电平兼容。而环路的两输入信号均为正弦信号,因此必须将它转移成ECL电平。对于使用+5 V电源来说,低电平为+3.1 V,高电平为+4 V。设计时选用MC10104或门电路集成块就可以完成此功能。其实际电路如图6所示。

图中R3、R4是ECL器件的负载电阻(即内部射随器发射极的到地电阻。如果使用的是-5 V电源,此电阻应接到负电源上),一般为510Ω。R1和R2是直流反馈电阻,作用是将输入端的直流电平调整到ECL电平的中心值。+5 V工作时,其中心值在3.6 V左右。设计时可选择R1=R2=R3=R4。

3 调整与测试

该系统的调整和检查主要有静电检查、开环检查和闭环检查。静电检查主要检查正弦/ECL转换电路和鉴相器,开环检查主要是对R端加信号、V端加信号和鉴相器输出端(MC12040的3脚)不等宽度的方波信号进行检查,闭环测试即环路锁定情况下的测试,包括环路带宽、捕捉带、信号中断/接通状态下的捕获概率和信号调制突发状态下的捕获时间等。

4 结束语

目前,这种70 MHz载波跟踪解调环还比较少见,一般都在10.7 MHz或更低频率上使用这种解调环。研究这种载波跟踪解调环的目的使其能够在70 MHz调制中频上进行解调,同时降低解调噪声,扩宽解调环的工作频率范围,为工程设计提供有价值参考方案。

责任编辑:gt

-

卫星定位接收机载波跟踪的设计与实现2009-09-19 4092

-

倍频采样相敏解调器及其应用2010-05-13 1883

-

mc1496用于锁相环的鉴相器2011-04-05 3648

-

调制器/解调器简介2011-11-18 4760

-

解调器2014-04-30 2997

-

相敏解调器2016-03-16 7008

-

DVB_S2标准的解调器设计2017-03-09 5989

-

调制器和解调器2017-12-07 4315

-

如何利用FPGA技术实现数字式频分多路副载波解调器的设计?2021-04-08 1395

-

全数字QAM解调器方案采用了载波相位和符号定时的联合估计环——基于FPGA的同步电路设计与实现研究 精选资料分享2021-07-27 1226

-

载波跟踪环解调器的设计应用2009-03-07 578

-

相敏放大解调器2010-09-17 2720

-

码环与载波环路鉴相、鉴频原理2017-10-31 2959

-

MC1496和MC1496B平衡式调制解调器的详细中文资料概述2018-06-14 3546

全部0条评论

快来发表一下你的评论吧 !