赛灵思Versal自适应计算加速平台助于高效实现设计目标

描述

随着AI、大数据、云计算等技术在各行各业广泛应用,相应的设计结构和设计内容也变得日益复杂。目前的应用开发速度已无法满足企业的需求,如何简化设计进程,提高应用开发效率成为当下亟需解决的问题?赛灵思 Versal 自适应计算加速平台的设计方法论是帮助精简 Versal 器件设计进程的一整套最佳实践,遵循这些步骤和最佳实践进行操作,将有助于以最快且最高效的方式实现期望的设计目标。

Versal ACAP 属于异构计算平台,具有多个计算引擎。在 Versal ACAP 上可映射各种应用,包括对无线系统、机器学习推断和视频处理算法进行信号处理。除了多个计算引擎外,Versal ACAP 还可使用高速串行 I/O、片上网络 (NoC)、 DDR4/LPDDR4 存储器控制器和多重速率以太网介质访问控制器 (MRMAC) 来提供超高系统带宽。Versal 器件分类为 Versal Prime 系列、Premium 系列和 AI Core 系列。

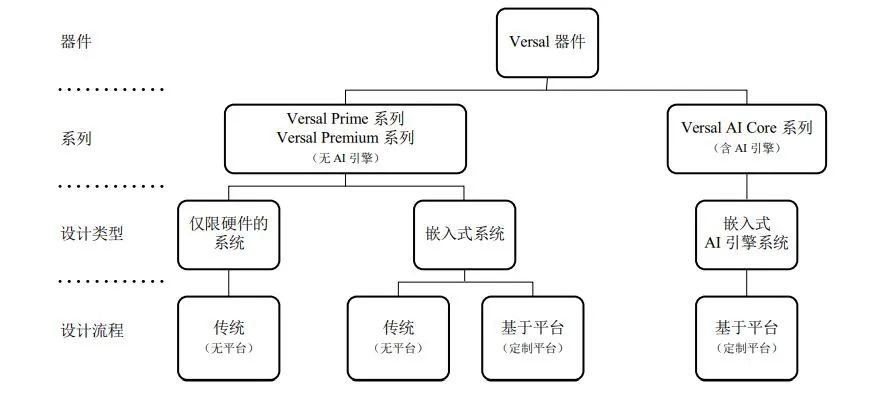

下图显示了每种 Versal 器件系列所支持的不同系统设计类型和设计流程。

图:系统设计类型

适用所有系统的设计流程

系统设计方法论要求基于目标应用明确所有系统要求。其中包括识别具有正确特性(例如,DDRMC IP 数量、AI 引擎 等)的相应 Versal 器件。您还必须考量功耗和发热要求。选择相应的器件后,下一步即可着手系统设计,包括在器件上进行目标应用的软硬件协同设计、系统验证以及初始化和调试。

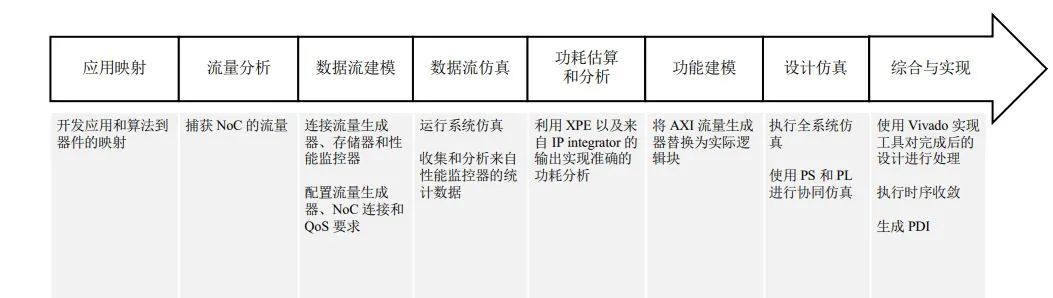

为确保充分利用 Versal ACAP 中可用的多种多样的计算元件,并使用最高效的实现流程,赛灵思建议采用下图所示的系统设计方法论流程,此流程适用于所有系统设计类型。

图:系统设计方法流程

系统设计时的考虑因素

合理可行的设计流程解决方案需要将各种关键变量考虑在内,在仅限硬件的系统设计中,关键注意事项之一设计中的数据流。通常这些设计都具有下列组件:

• 多个高速 I/O 接口

• 内部数据缓冲和存储,具有由片上 RAM 和外部 DDR 存储器组成的存储器层级

• 内部数据处理逻辑

对于能够处理外部和内部流量带宽和时延要求的设计,为其创建 DDRMC-NoC 配置至关重要。赛灵思建议先执行流量分析以评估并最终明确流量,然后再继续执行设计的整体集成和实现阶段。除此以外,报告中还涵盖了嵌入式系统设计值得考量的特殊注意事项,根据随附的是嵌入式系统还是服务器系统,每个步骤所面临的难题也不尽相同。

原文标题:用户指南 | Versal ACAP:精简设计进程的最佳实践

文章出处:【微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之准备工作(1)2024-03-07 2065

-

Versal:首款自适应计算加速平台(ACAP)2023-09-18 721

-

赛灵思2021自适应计算挑战赛技术讲解分享会2021-10-27 4929

-

赛灵思Versal自适应计算加速平台指南2021-10-11 5471

-

赛灵思首届自适应计算挑战赛初创企业竞赛单元前三甲揭晓2021-05-17 2491

-

赛灵思Versal ACAP如何为算力“跨界赋能”?2021-01-15 3201

-

揭秘赛灵思计算平台ACAP技术细节2021-01-04 4597

-

详解基于赛灵思的Versal™ ACAP设计创建步骤2020-09-28 7400

-

Xilinx联手全球顶尖高校构建自适应计算研究集群2020-05-08 3817

-

赛灵思正式推出Versal Premium 可提供比当前FPGA高达三倍的吞吐量2020-03-12 5298

-

引领迈入自适应计算时代,Xilinx Versal ACAP荣膺2019“世界互联网领先科技成果”2019-10-21 1366

-

自适应计算加速平台 功能超CPU和FPGA2019-06-23 2052

-

赛灵思发布自适应计算加速平台芯片系列Versal2018-10-22 6658

-

Xilinx推出Versal:业界首款自适应计算加速平台,支持快速创新2018-10-18 2252

全部0条评论

快来发表一下你的评论吧 !