2020DAC- SDC冠军作品分享,充分结合FPGA数据流架构的优势

描述

如果说上期SkrSkr队伍的设计像是德智体美劳全面发展的“五好学生”,那么冠军队伍的设计则更像是“不偏科的特长生”。

作品跳出前两届Top3队伍的设计思路,充分结合FPGA数据流架构的优势,逐步优化设计,最终在帧率上达到212fps,首次参赛一举夺魁。

作品全HLS设计,采用PYNQ框架,其提高帧率的优化流程在其他HLS设计中亦值得借鉴。

01

DAC-SDC赛事回顾

从2018年设立DAC-SDC开始,每年都会吸引全球百支知名研究团队参与角逐,与计算机视觉类的国际知名目标检测比赛不同,DAC-SDC对高精度、高效率的追求不仅仅停留在算法层面,其更注重考察基于软硬件协同的系统构建能力,即参赛设计不仅要提高复杂场景中小物体精准检测的能力,还需要考虑整个硬件系统在图像处理速度和功耗方面的要求。而且随着技术迭代速度的加快,该赛项的平台和要求也在不断改进。2018、2019年该赛项由Nvidia、Xilinx 和 DJI 大疆创新赞助,赛项分为GPU和FPGA两个方向。2020年只保留了FPGA方向。从选用平台的角度来对比,2018年以Zynq7020作为目标平台;2019年选用逻辑资源较多的ZU3作为目标平台,逻辑资源的增加提升了大赛的可发挥空间。2020年仍延用19年的目标平台Ultra96。关于赛事详情请参考 快讯|中国团队包揽顶会DAC-SDC竞赛冠亚军

2018年比赛情况

TX2 GPU和Zynq7020 的对比结果显示,在同等精度条件下FPGA的处理速度较低,但FPGA平台所需的功耗仅为GPU平台的不到1/4。在2018年的设计中,Top3均采用了“自顶向下”的DNN设计思路(沿用目标检测常规算法),而后再考虑算法在硬件层面的优化。其中FPGA组的冠军来自清华大学汪玉教授团队,其采用了深鉴科技的硬件加速器架构 DPU、全栈式工具链 DNNDK 和深度压缩技术的基础上,从算法、软件和硬件对整个目标检测系统进行了全栈式的协同优化。通过采用硬件友好的 SSD 网络和多线程优化技术,结合深度压缩和定点训练,在保证识别精度的前提下,满足了低功耗和实时性的要求。

2019年比赛情况

FPGA组升级到逻辑资源较多的ZU3(Ultra96)平台。与2018年相比,在精度和速度方面的表现均有一定的提升。特别值得一提的是,2019年 GPU和FPGA的冠军来自同一团队,其由UIUC Deming Chen教授课题组联合了 IBM、Inspirit IoT和新加坡 ADSC 的研究人员组成。该网络架构采用“自底向上”的DNN设计思路,以硬件资源限制为约束进行网络结构搜索得到架构的优化设计,而后将其部署在目标平台上。因此,冠军团队的工作实质上是同一网络架构(SkyNet)在不同平台的优化设计实现。

纵观前两年的工作,2018年解决的问题主要集中在限定资源条件下如何部署DNN模型;2019年冠军组的工作则体现了限定资源条件下如何搜索最优模型架构。上述工作更多考虑的是算法的本身和资源的约束,而没有充分发挥FPGA平台自身优势。

02

我们的工作

基本设计思路

我们团队主要从FPGA的架构特点入手对任务处理进行优化设计。FPGA的优势在于其灵活、高效地并行化设计架构,适于处理流式、计算密集型任务,适于不同字节宽度的调节等。针对本赛项待处理的目标检测任务特点,我们选用了卷积神经网络算法,其中包含多层结构,需要依次计算各层,且计算密集。结合待处理任务的特点,为了充分发挥FPGA的优势,我们提出了以下设计思路:

l 算法设计优化:压缩神经网络的参数量,且采用低bit量化技术,使得参数量较少且每个参数所需要的储存空间减少,从而使所有的参数能够置于FPGA片内BRAM中,减少加速过程中参数频繁调入/出带来的开销。

l 硬件设计优化:基于FPGA资源构建高效流水结构,将卷积神经网络中的所有层都置于片上,使得所有层能够以流水线的形式并行进行计算;设计高效的低bit的矩阵计算单元,在有限资源的约束下最大化并行度。

基于上述设计构想,数据输入加速器能直接输出计算结果,中间结果不必搬运到外部RAM,减少了不必要的时延和能耗。低bit计算减少了单个计算单元的资源开销,从而提高了整体并行度,进而提高了整个神经网络计算的速率。

设计方案

1、目标检测算法的设计

基于上述基本设计思想,我们自行构建了适于Ultra96平台资源限定条件的网络模型。其中主干网络选用类VGG架构,为了降低所需的参数量和计算量,我们严格控制了各层滤波器的数量,后端采用类yolo 架构设计,整个网络模型如下图2所示。与2019年的第一名相比,我们的算法虽然精度略低,但计算量和参数量都有大幅度地降低。

2、网络量化设计

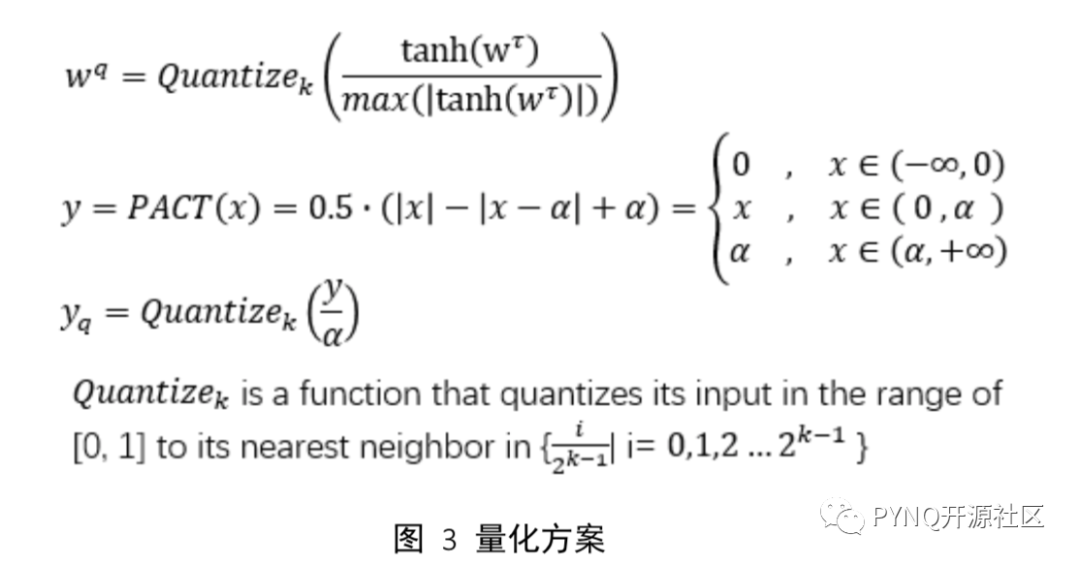

量化技术是整个解决方案中重要的一个环节。我们量化了整个神经网络,包括权值量化,激活量化等。量化方法如下:

我们对所有的权值(W)和激活后的数据进行了归一化处理,使得所有的数据在尺度上是统一的。而后将权值和特征图数据都量化到了4bit,虽然算法精度上有所降低,平均IoU从0.701降低了到0.649,但所需参数的储存空间降为原来的八分之一。我们只需要花费0.105 MB片上空间就能将所有参数置于片上,而Ultra 96 v2板上FPGA芯片中共有0.95 MB BRAM空间。

3、 自定义数据流的AI加速器设计

根据待处理任务特点,我们基于目标平台(Ultra96)资源特点,设计和实现一套“硬件函数库”,将pytorch中的CNN算法映射到FPGA中(如下图5)。其中,我们将pytorch中的卷积计算(Conv2d_Q)拆分成两个部分——滑动窗口单元(SWU)和矩阵向量乘单元(MVU),SWU负责将卷积计算展开为矩阵向量计算,MVU则负责接收SWU输出的数据流并计算。为减少片上存储空间(缓存)使用量,我们将原CNN算法中的批正则化层(BatchNorm2d)与激活量化层(ReLu_Q)合为一个模块Bn_Relu进行处理。为了便于构建流水处理架构,原pytorch中采用的四个层(卷积层、批正则化层、激活量化层和池化层)就变为我们定义的新四层(SWU层、MVU层、Bn_Relu层和MaxPool层),且每层中的Bn_Relu和MaxPool是可选的(图中用虚线框标出),每层都有独立缓存空间存储对应层参数。同时,为了提高效率,每层内部也最大程度展开为流水形式。

我们将所有层都置于片上,当上一层有计算输出时,下一层立即开始计算,各层同时运行。通过计算量分配各层所需要的逻辑资源,使得每层的时延趋向一致,使加速器运行效率最大化。

系统框架及优化设计

基于上述设计思想,最终实现的系统框图如下。其中,我们采用DMA搬运数据,CPU负责任务调度工作。为了实现加速器IP与CPU之间的并行,我们在外部RAM中开辟了两块缓冲区轮流为加速器提供图片数据。

由于计时规则在五月份做出了调整,将读入图片的时间和功耗也计入在内,而我们在五月版提交代码的速度瓶颈主要卡在读图(Load image)时延。针对这个问题,我们对于系统待处理的任务重新进行了更为细致的优化部署。由于待处理任务分为四个部分:Load image、Resize image(简写为Resize)、Compute CNN(简写为CNN)、Calculate bounding box(简写为Calc bbox)。我们分别在PS端进行多核并行优化处理,在PS-PL端进行了负载均衡处理,从而优化了任务在PS和PL端的部署,该过程对最终成绩中FPS提升贡献很大。

我们的成绩

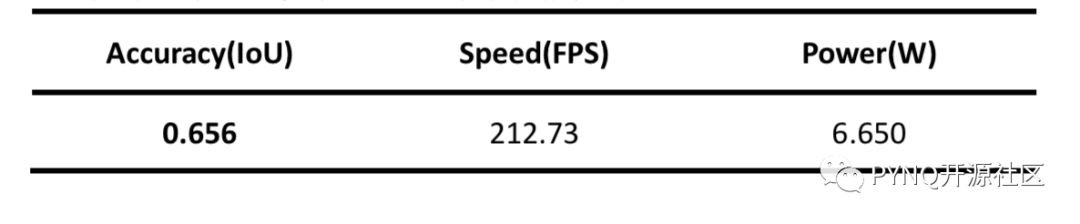

基于上述设计,最终的实现的加速方案性能如下:

。

跟前两年的结果相比,虽然我们的精度(IoU)略有损失,但在速度方面我们有了大幅度地提升。

03

总结

上述是我们在2020DAC-SDC中所做的一些努力。这是我们团队第一次参加DAC-SDC国际大赛,从关注该赛项到今天,我们一边摸索一边前进,很感谢组委会提供了这样的平台给我们实践锻炼和摸索提升的机会。身处计算机体系结构发展的黄金时代是我们这代人的幸运,相信未来系统设计必然将向着更精准、更高效、更低耗的方向迈进,我们也希望能够通过努力与各位同仁共同见证这个时代的辉煌。同时,我们的设计也已经开源在:https://github.com/heheda365/ultra_net

04

团队介绍

2020DAC-SDC Top-3的BJUT_Runner团队来自北京工业大学信息学部张文博老师和包振山老师带领的异构计算研究小组。参加本次比赛的团队成员包括:詹康(图中右下)、郭俊南和宋秉彦(图中左下)。受2020年新型冠状病毒疫情(COVID-19)影响,在整个参赛环节,团队成员一直采用在线研讨方式进行沟通(下图为本组指导教师和所有成员在线合影)。

原文标题:打破常规,深度结合FPGA架构优势|2020DAC- SDC冠军作品开源与技术分享

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

控制流和数据流的区别2023-09-13 8151

-

【工程源码】基于FPGA的OV5640数据流接收和应用基本逻辑设计2020-02-18 1560

-

Labview数据流编程的简单介绍2019-08-05 5258

-

数据流是什么2019-02-27 8164

-

数据流的网络实时入侵检测2018-01-17 1227

-

数据流编程模型优化2017-11-23 925

-

基于FPGA芯片的数据流结构分析2017-11-18 3047

-

基于数据流特征的电子文件访问方法2017-11-15 724

-

研究labview的数据流2013-12-31 3212

-

大众防盗数据流2013-08-31 7150

-

如何把软件的数据流设计好2013-07-23 3836

-

网络数据流存储算法分析与实现2011-05-26 627

-

基于数据流的Java字节码分析2009-12-25 1135

-

大众数据流分析2008-06-15 10834

全部0条评论

快来发表一下你的评论吧 !