深度解读硬件加法器、触发器、锁存器

电子说

描述

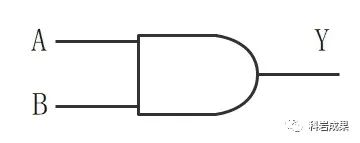

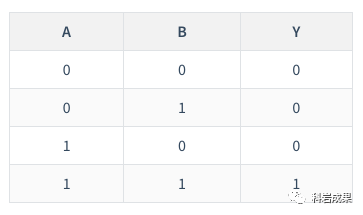

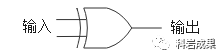

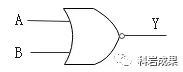

我们都知道,「通电」代表「真」,用逻辑1表示;「不通电」代表「假」,用逻辑0表示。「与门」电路是用晶体管搭建的,符号长这样:

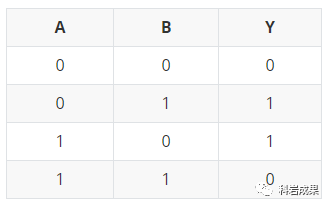

A与B的通断,可以决定Y点是否通电。

我们还为A、B与Y之间的关系画了一张表(真值表):

接着我们设计出了简单的「或门」「非门」,用它们可以搭建各式各样其他的门电路。

这篇文章讲一下,怎么利用基础门电路进行加法计算。

二进制加法

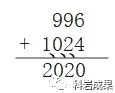

我已经忘了是什么时候学的加法了,应该是小学吧,先学10以内的,再学100以内的,然后不管多大的数都可以随便加了,算式很简单,就是逢10进1。

下面这个式子是一个万以内的加法:

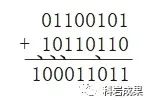

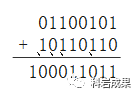

相应的,二进制就是逢2进1,下面这个式子是2个8位二进制数的加法计算:

半加器

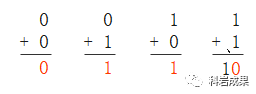

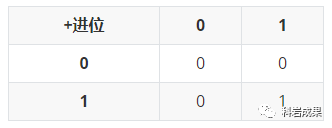

8位二进制数还太复杂,我们先来看看1位二进制数怎么计算的,一共有以下4种情况:

观察一下就能发现2个规律。

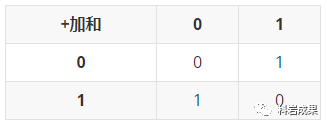

第一个规律,只考虑加法,不考虑进位时,加数与和之间的关系如下:

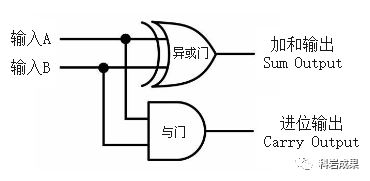

相同为0,不同为1。这个关系和「异或门」是相同的:

异或门我们之前没有聊到过,电路图长这样:

第二个规律是,如果只考虑进位,不考虑加法,加数与进位之间的关系如下:

只有全1时,才为1。发现了吗,这和本文开头与门的真值表是一样的。

2个一位二进制数相加将产生一个加法位和一个进位位,加法位输入与输出的关系跟与门是一样的,进位位跟异或门相同。

所以,可以像这样把两个门电路连起来,计算2个二进制数(A和B)的和:

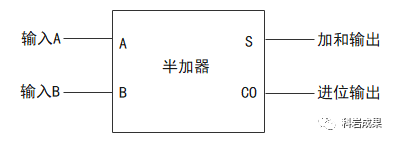

我们称这个电路为「半加器」,因为它只能计算2个一位二进制数的加法,没有办法将前面加法可能产生的进位纳入下一次计算中,如果有进位则实际上是需要3个加数参与计算。

用门电路画太复杂,可以封装起来这样表示半加器:

全加器

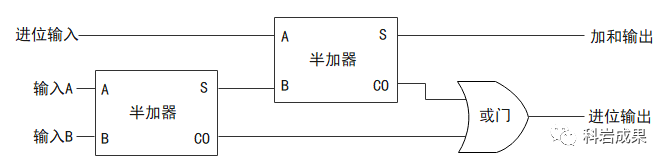

怎样计算3个加数的二进制加法呢?需要将2个半加器和一个或门如图连接起来:

左边能看到它有3个输入,右边依旧是1位加和输出,1位进位输出。

2个数的加和与上一次的进位相加,得出的加和作为3个数最终的加和;2个数相加或3个数相加的进位作为3个数加和最终的进位位。

用文字描述有点不好理解,把这个电路图全部输入和输出情况都展示出来,画一个表就明白了:

很明显,这个表就是2个一位二进制数带进位的全部状态。

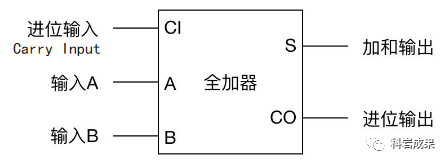

每次做加法时画2个半加器和一个或门很麻烦,我们用下面这个图示把它们封装起来,这个能计算3位二进制数加法的电路就称为「全加器」。

加法器

现在回到开头那个二进制加法:

它有8个二进制位,到目前为止我们还只能计算2个一位二进制数,最多再增加一个进位的加法,我们最终的目标当然是2个8位、16位乃至32位数的加法。

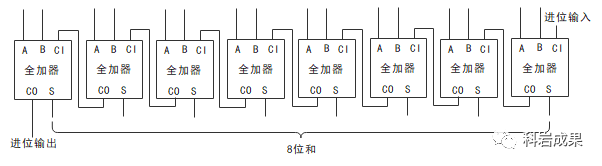

其实,非常简单,用8个全加器一块算!

把8个全加器每个进位输出作为下一个的进位输入,首尾相连就可以啦!

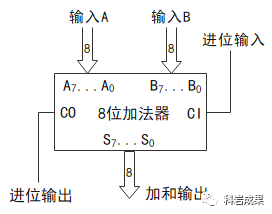

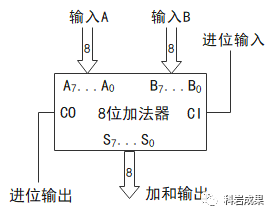

每次这样画太麻烦,可以封装成一个框图:

大箭头代表8个输入/输出端,有8个独立的信号。

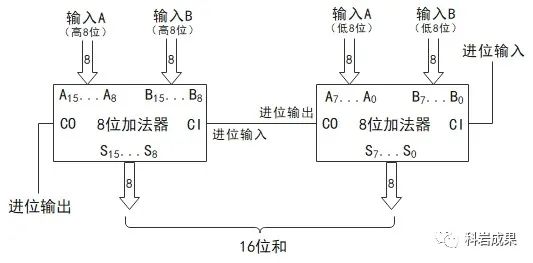

一旦我们拥有了8位二进制加法器,把它们级联起来,很容易就能得到一个16位或32位的加法器啦。

加法计算是计算机的基本运算,其实,计算机唯一的工作就是做加法计算。不论是减法、乘法、除法、在线支付、火箭升空还是AI下棋,都是利用加法实现的。

把加减乘除和逻辑运算等运算单元集成起来,就组成了CPU中的基本计算单元:ALU(算术逻辑单元Arithmetic and Logic Unit)。

用加法器计算2个数的加法其实就是用硬件方式实现了一个加法计算器,输入A和输入B的高低电平决定了输出S和CO的高低电平。

这样的电路同一时刻只能表示一种状态,只要改变了A、B中任意一位,输出就会有所变化。

现在我们想计算更多二进制数的加法,比如5个数A、B、C、D、E的加法(先不考虑进位)。

步骤应该是这样:首先把A、B作为输入,得出一个输出S1,我们要记下来S1的值,然后把S1和C作为输入,得出S2.。。。以此类推,要记下很多个数,然后再用加法器计算。

5个数都已经很麻烦了,如果要计算更多个数该怎么办?能不能把每次计算完的结果存起来,下次继续使用呢?

我们的需求

这个加法器有个特点,就是两个加数A和B的值决定着加和S的值。

这个值是实时决定的,也就是说,A、B中只要有一个数据位发生了改变(0变1或1变0),加和就一定、立即发生改变。

我们如果想用这个加法器算「累加和」将会很麻烦,比如5个数A、B、C、D、E的加法。

首先把A、B作为输入,得出一个输出S1,我们要记下来S1的值,然后把S1和C作为输入,得出S2.。。。以此类推,要记下很多个数,然后再用加法器计算。

工程师怎么会做这种无脑循环的工作呢,得想办法交给计算机寄几做。

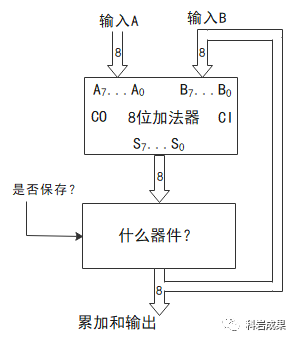

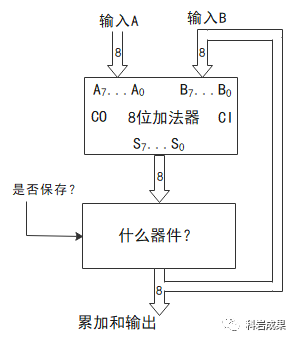

好像只要做一个什么器件连在这个加法器的输出上,这个新器件能够保存加法器输出的和,并将算好的和再作为一个参数输入,传递给加法器就可以了。

注意这个新器件,首先它支持输入和输出;其次它能「保存」当前的值;最后,有一个类似「开关」的引脚决定它是否保持当前的值。

「保存」是什么意思?其实很好理解,就是不论输入的数据位怎么变化,输出都不变。

不考虑8个数据位,先只搭建一个这样具有「保存」功能的门电路,能保存一个bit就ok。

或非门点灯

科岩已经点灯无数,这次依然从点灯开始,用或非门试一下。

「或非门」的真值关系如下表,记住输入只要有1,输出一定为0就可以了。

或非门的符号:

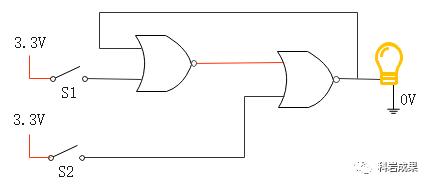

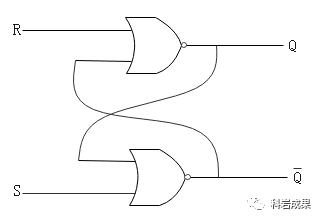

按照下面这个电路把两个或非门与一个小灯泡连起来,如图:

仔细观察,能发现我把右边或非门的输出直接作为输入连接到左边或非门上,这会产生什么神奇的现象呢?

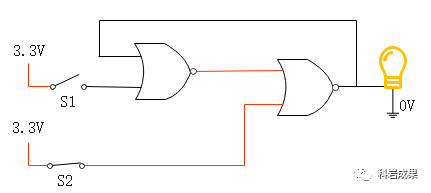

如上图,最开始,左边或非门的输入都是0,输出为1;右边或非门输入一个是0,一个是1,输出0,灯泡是不亮的。

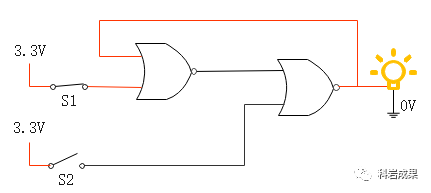

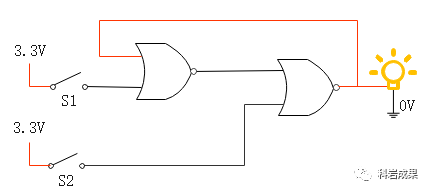

现在把开关S1连通,连通瞬间,左边或非门输出0,右边或非门输出1,灯泡被点亮,然后右边或非门输出的1给到左边或非门,2个输入都是1,它的输出为0保持不变,灯泡点亮不变。

接着我们把开关S1断开,如下图神奇的事情发生了,灯泡依然保持点亮状态!因为左边或非门仍有一个输入是1。

如果把S2闭合会怎样呢?灯泡马上熄灭了。

这时再打开S2,电路回到最初的状态,灯泡还是熄灭状态。

可以总结规律了:

•导通S1,灯泡点亮,不论我们怎么控制S1,灯泡都是亮的

•导通S2,灯泡熄灭,不论我们怎么控制S2,灯泡都是亮的

这不就达到我们想要的「保存」功能了嘛,不论输入的数据位怎么变化,输出都不变。

触发器(Flip-Flop)

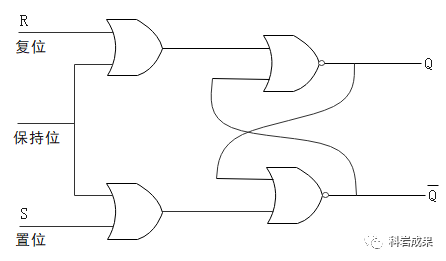

像上面把两个或非门连起来,能够稳定保存电路状态的电路被称为「触发器」。

Flip-Flop的意思是「翻转」,中文翻译比较奇怪,我们通常理解的触发器是Trigger,不过没关系,其实就是个名称而已。

上面这个触发器叫做R-S触发器,它有2个输入端S(Set)和R(Reset),2个输出端Q和~Q(实在打不出Q上面的横线o(╥﹏╥)o)。

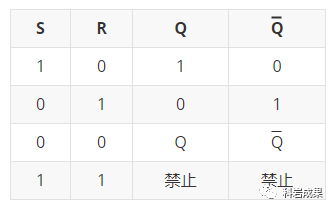

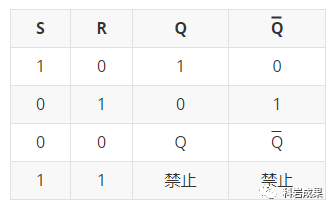

当S为1时,输出Q为1,~Q为0;当R为1时,输出Q为0,~Q为1;当S和R都为0时,输出Q和~Q保持不变;当S和R都为1时是一个不正确的状态,我们不使用这个状态。

不是特别绕吧?画个表:

R-S触发器最大特点就是它能记住2个输入端的状态。想要记住上一次的状态时,把2个输入端都置0就可以了。

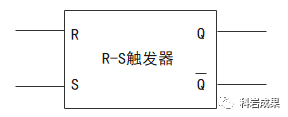

每次画2个或非门太麻烦,封装一下:

有了触发器,计算机除了算些加减乘除、与或非逻辑运算,开始具备了存储功能,我觉得触发器真是一个神奇的存在,把平平无奇的门电路连起来竟然就赋予了计算机「记忆」。

计算机中寄存器(Register)、内存(RAM)最最基础的组成单元就是触发器。

理解了触发器的工作原理,也就理解了内存的工作原理。

「触发器」的电路实现,最后画出了一个R-S触发器的框图,它有2个输入端,2个输出端:

R-S触发器最大特点就是它能记住2个输入端的状态。想要记住上一次的状态时,把2个输入端都置0就可以了。

还记得上篇文章中我们提出的那个需求吗,做一个什么器件连在加法器的输出上,这个器件能够保存加法器输出的8位数的和,并将算好的和再作为一个参数输入传递给加法器,从而实现一个累加器。

R-S触发器只能记住1位数据的状态,怎样能记住8位呢,这篇就来讲讲。

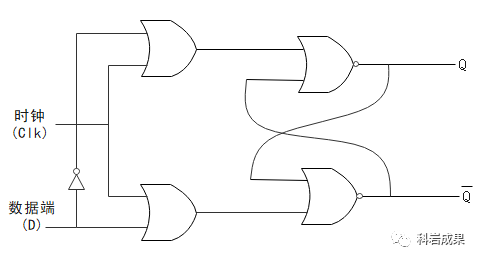

D触发器

1个R-S触发器能存1位数据,所以需要8个R-S触发器;1个R-S触发器,有2个输入端2个输出端,8个就是16个输入端,16个输出端。

而我们需要的是一个8输入、8输出的器件,我们得想办法简化R-S触发器。

观察一下R-S触发器,虽然有2个数据输入端和2个数据输出端,但实际上它只能保存1种状态,即保存1个bit数据位,因为Q和Q`的状态一定是相反的。

要保存数据时,需要把2个数据输入端都置成低电平。

这有点麻烦,因为要同时控制两个端;又有点浪费,明明只能存一位数据却用了2根线;还有点耦合,因为数据输入端也有控制作用,同时也是控制端,没区分开。

能不能把数据和控制分开,并且输入和输出只用一个数据端?

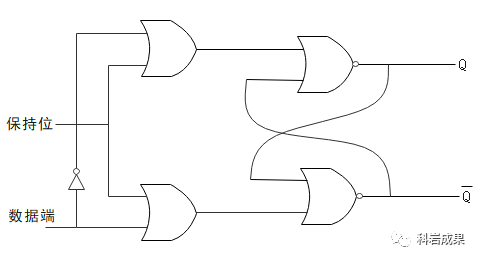

我们试着增加一个具有控制功能的「保持位」,它能决定电路当前的状态是否被「记住」。

当「保持位」为1时,数据输入的值就会被电路记住,当保持位为0时,数据输入位的任何值都不会影响电路的状态。

先画一下这个理想电路的真值表:

试着用R-S触发器搭建和这个表对应的电路:

这个电路实现了我们要的保持位的效果,保持为为1时,电路状态与R-S触发器相同;保持位置0时,相当于S和R为0,电路保存当前状态。

可这样又增加了一条线,能不能用一根线替换掉S和R这两根输入端呢?可以注意到,R与S的状态是相反的,所以很简单,用一个非门就可以了。

如上图,当保持位为1时,输出Q端与数据端相同;当保持位为0时,数据端怎么改变都不会影响电路状态,即电路会记住保持位最后一次置1时数据端的值,是不是很简洁很舒服。

上面这个电路被称为电平触发的D(Data)型触发器。

锁存器

通常,保持位需要不断的在0和1之间有规律的按一定频率变化,这就像钟表一样,滴答滴答,永不知疲倦。所以我们给保持位换一个称呼:时钟(clock)。

这样用时钟控制的D触发器也称作「锁存器」,因为存储进去的数据就好像被锁住了一样。

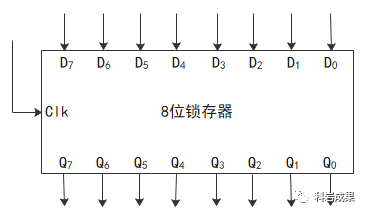

把8个锁存器的时钟端接在一起,引出输入端D和输出端Q,就构成了一个8位的锁存器:

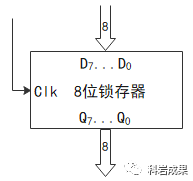

这个锁存器可以一次保存一个字节(8位数),把这个框图封装一下:

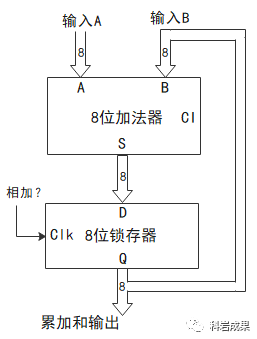

这个8位锁存器就是我们需要的那个新器件啦,把它和8位加法器相连,就能得到一个累加器:

来模拟一下它的运转过程。

最开始,输入A为0,锁存器中8个输出端数据也均为0,即输入B为0。

把输入A设为1,由于输入B为0,此时加法器输出与A相同。

这时把锁存器的时钟置1,锁存器电路状态改变,输出的值和加法器相同;再把时钟置0,锁存器保存加法器的结果,此时加法器的输出不会影响锁存器。

锁存器同时会把加和作为加法器的输入B传递给加法器,把A的值换成2,加法器会计算A和B的加和,锁存器时钟置1后置0,再保存加和,如此循环,就可以计算输入A的累加和了。

编辑:jq

-

加法器的原理是什么 加法器有什么作用2024-05-23 7753

-

D触发器与Latch锁存器电路设计2023-10-09 6012

-

加法器的原理及采用加法器的原因2023-06-09 6448

-

运算放大器的同相加法器和反相加法器2022-08-05 36512

-

锁存器和触发器2022-03-10 9509

-

什么是加法器?加法器的原理是什么 ?2021-03-11 5138

-

锁存器与触发器的区别2020-11-29 26371

-

加法器原理2019-06-19 27416

-

寄存器、锁存器和触发器的区别2018-07-03 4026

-

同相加法器电路原理与同相加法器计算2016-09-13 58858

-

FPU加法器的设计与实现2012-07-06 1226

-

锁存器和触发器原理2010-08-18 2012

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 14406

-

加法器,加法器是什么意思2010-03-08 5889

全部0条评论

快来发表一下你的评论吧 !