基于SPI串行总线接口的Verilog实现

电子说

描述

简 介:

集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。

重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。

在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台。并逐步向支持系统级的设计方向发展。而且,在设计过程中,越来越强调模块化设计。

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作。

1 SPI总线接口概述

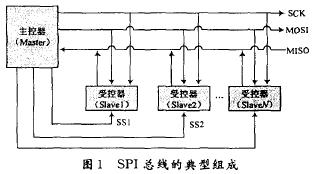

SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O器件 其典型结构如图1所示。

SPI总线具有以下特点:

(1)连线较少,简化电路设计。并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。而这种设计,仅需4根数据和控制线即可完成并行扩展所实现的功能。

(2)器件统一编址,并与系统地址无关,操作SPI独立性好。

(3)器件操作遵循统一的规范,使系统软硬件具有良好的通用性。

2 SPI总线接口的设计与实现

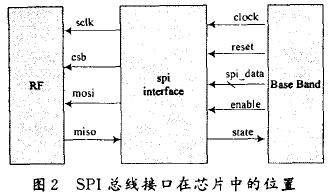

该模块是802.1lb无线局域网芯片中的一子模块,其在芯片中的位置如图2所示。

其中base band(基带)为SPI的主控器(master),RF(射频)为SPI的受控器(slave)。SPI interface作为baseband与RF的通讯接口,主要完成以下工作:

(1)将从base band接收到的16位的并行数据,转换为RF所能接收的串行数据,并将该数据根据SPI协议送给RF。

(2)产生RF所需的时钟信号SCLK,使能信号CSB。

(3)接收从RF传回的串行数据,并将其转换为并行数据。

(4)将base band发送的数据,与RF返回的数据进行比较,并把比较结果传给base band。

下面给出用Verilog HDL语言实现前两项功能的关键程序,相关变量的声明在此略去。

//generate a counter

always@ (posedge clock or negedge reset)

begin

if(!reset)

counter《= 0;

else if(enable)

begin

if(counter《 53)

counter=counter + 1;

end

end

//generate signal “csb”

always@ (posedge clock or negedge reset)

begin

if(!reset)

csb 《=1;

else if(counter》= 1 && counter 《= 50)

csb = 0;

else

csb = 1;

end

//Generate “sclk”

always@ (posedge clock or negedge reset)

begin

case(counter)

6‘d02: sclk = 1;

6’d05: sclk = 1;

6‘d08: sclk = 1;

6’d11: sclk = 1;

6‘d14: sclk = 1;

6’d17: sclk = 1;

6‘d20: sclk = 1;

6’d23: sclk = 1;

6‘d26: sclk = 1;

6’d29: sclk = 1;

6‘d32: sclk = 1;

6’d35: sclk = 1;

6‘d38: sclk = 1;

6’d41: sclk = 1;

6‘d44: sclk = 1;

6’d47: sclk = 1;

default sclk = 0;

endcase

end

always@ (counter or csb)

begin

if(csb == 0)

case(counter)

6‘h00,

6’h01,

6‘h02,

6’h03:mosi_index = 5‘h00;

6’h04,

6‘h05,

6’h06:mosi_index = 5‘h01;

6’h07,

6‘h08,

6’h09:mosi_index = 5‘h02;

6’h0A,

6‘h0B,

6’h0C:mosi_index = 5‘h03;

6’h0D,

6‘h0E,

6’h0F:mosi_index = 5‘h04;

6’h10,

6‘h11,

6’h12:mosi_index = 5‘h05;

6’h13,

6‘h14,

6’h15:mosi_index = 5‘h06;

6’h16,

6‘h17,

6’h18:mosi_index = 5‘h07;

6’h19,

6‘h1A,

6’h1B:mosi_index = 5‘h08;

6’h1C,

6‘h1D,

6’hlE:mosi_index = 5‘h09;

6’h1F,

6‘h20,

6’h21:mosi_index = 5‘h0A ;

6’h22,

6‘h23,

6’h24:mosi_index = 5‘h0B;

6’h25,

6‘h26,

6’h27:mosi_index = 5‘h0C ;

6’h28,

6‘h29,

6’h2A:mosi_index = 5‘h0D ;

6’h2B,

6‘h2C,

6’h2D:mosi_index = 5‘h0E;

6’h2E,

6‘h2F,

6’h30:mosi_index = 5‘h0F;

default:mosi_index = 5’h00;

endcase

else

mosi_index = 5‘h00:

end

assign mosi=spi_data[mosi_index3];

用Verilog HDL实现的SPI总线接口模块,在ModelSim 中编译、调试,并做了前仿真。

前仿真通过后,又在Altera公司的EPXA10 Develop Board上做了FPGA验证,结果与在ModelSim 中的仿真结果一致。最后在base band与RF的联合调试过程中,该SPI总线接口模块达到了预期的要求。

编辑:jq

-

基于FPGA的串行接口SPI的设计与实现2015-01-28 8648

-

基于Verilog的SPI接口设计资料分享2021-11-11 1428

-

基于PC/104 总线与CPLD 的SPI 接口设计2009-05-30 1138

-

SPI接口读写串行EEPROM2009-09-19 1126

-

基于SPI串行总线的语音接口电路的软硬件设计2010-05-08 512

-

基于FPGA的串行外围接口SPI设计与实现2012-05-23 10585

-

一文读懂SPI串行外设接口2017-04-27 10814

-

SPI总线接口实现数据传输的实现方法2017-11-16 940

-

使用Verilog实现SPI串行总线接口的资料和源代码免费下载2020-08-19 1277

-

基于Verilog的SPI接口设计2021-11-06 1146

-

常用串行总线(二)——SPI协议(Verilog实现)2023-01-06 10947

-

常用串行总线——SPI协议(下)2023-01-21 1677

-

SPI串行外设接口设计实现2023-05-29 2341

-

SPI总线的原理与Verilog设计实现2023-08-14 1888

-

SPI通信总线概述和Verilog实现2025-02-07 2406

全部0条评论

快来发表一下你的评论吧 !