EDA工具的发展特征

EDA/IC设计

描述

作者:赛迪智库集成电路研究所

EDA工具市场竞争特征

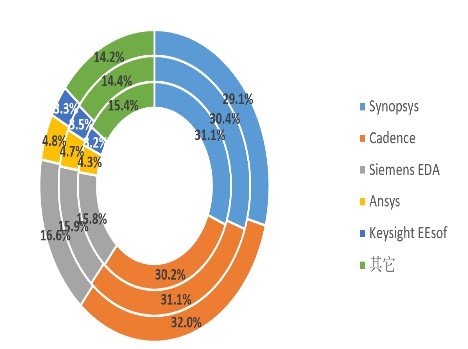

经过30余年的行业整合发展,全球EDA工具市场体现出较明显的寡头垄断特征,新思科技(Synopsys)、楷登电子(Cadence)与西门子EDA(原Mentor Graphics)作为目前仅有的拥有设计全流程EDA工具解决方案的企业,集中了全球超77%的EDA工具市场。此外,Ansys凭借热分析、压电分析等优势点工具,Keysight EEsof凭借电磁仿真、射频综合等优势点工具,获得市场第四、第五的位置。近三年来,在优势工具的巩固下,在2020年全球72.3亿美元的市场中,前五大EDA工具企业控制了约85%市场,其中市场前三大企业的市场占有率近80%。除市场前三的EDA工具企业外,其他企业缺少布局设计全流程工具技术的综合实力,各企业均在各自擅长领域开发面向特定流程或个别环节的工具产品,瓜分剩余市场份额。

图1 2018-2020年全球EDA工具市场竞争格局

注:内圈至外圈分别为2018-2020年数据

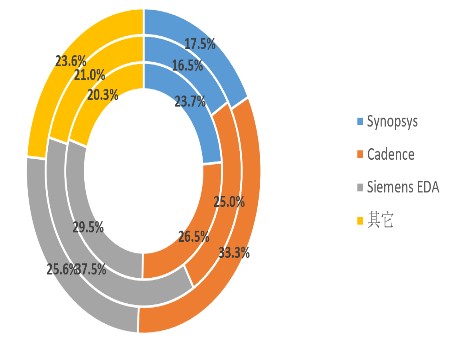

与国际市场相似,我国EDA工具市场同样呈现出市场份额集中的特点,近三年市场前五大企业的市场占有率在86%左右。其中,Synopsys、Cadence、Siemens EDA为我国市场前三大EDA工具供应商。2020年,在我国66.2亿元人民币的EDA工具市场中,前五大供应商占有85.4%的市场份额。按年度分析,由于单一市场大客户周期性订单影响,市场前三大供应商的市场份额波动较大,整体看均具有明显市场优势。我国本土的华大九天公司通过十余年市场耕耘,近年来持续实现市场突破。据统计,2020年华大九天公司在我国市场的销售额超过Ansys公司,成为我国市场第四大EDA工具企业。

图2 2018-2020年我国EDA工具市场竞争格局

注:内圈至外圈分别为2018-2020年数据

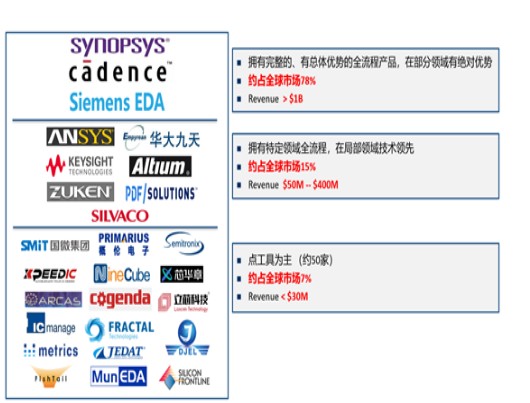

从技术格局来看,全球EDA行业企业可分为三个梯队。其中,第一梯队企业拥有完整的且总体优势明显的全流程EDA工具,部分流程工具在细分领域拥有绝对优势,EDA领域年营业收入超10亿美元,代表企业有新思科技、楷登电子和西门子EDA(原Mentor Graphics)。第二梯队企业拥有部分领域的全流程工具产品,且在局部领域具有绝对优势,年营业收入在5000万美元至4亿美元之间,面向处在第三梯队的EDA企业,相关公司产品以点工具为主,企业年营业收入普遍小于3000万美元。

图3 EDA行业技术格局

对于我国EDA行业企业,在市场驱动与资本加持的助推下,代表性企业呈加速发展势头,未来数年有望出现多家企业进入行业第二梯队。华大九天公司作为我国唯一在部分领域拥有全流程工具的EDA工具企业,在营收规模上在本土企业中具有较明显优势,目前公司已在模拟/数模混合设计、数字设计、平板显示设计以及晶圆制造部分相关领域进行布局,整体技术水平在国内具有领先性,并进一步实现了各大类工具的部分代表性点工具产品在关键参数上优于市场国际主流产品。

EDA工具行业商业模式特征

集成电路设计工具(EDA工具)从计算机辅助设计软件发展而来,在行业商业、销售模式上具有与工业软件相似的方式。经过三十余年独立发展,EDA工具结合集成电路领域特殊的市场形态和运作方式,形成了具有自身特色的行业商业和销售模式。综合看,国际主流厂商推广EDA工具商业应用的方式包括“定期授权+技术服务”,以及面向高校、科研院所推广教育应用。

面向“定期授权+技术服务”的商业模式,原美国Arcsys公司在商业竞争中为降低客户的EDA工具使用成本、增强公司与客户间的耦合度,实现公司产业市场竞争力提升,在20世纪90年代一改传统的EDA工具永久许可销售模式,将EDA工具的一次性售卖改为有限期租赁,并在产品服务期为客户提供开发技术支持等的服务。通过商业模式变革,原Arcsys在一年多时间年实现销售额超600%增长,进一步深刻影响其他EDA工具企业的经营向“定期授权+技术服务”的方式上转变。目前,EDA工具企业对客户每一期的EDA工具租赁时长普遍在2-3年,由此导致大客户新一期订单对部分企业销售收入造成周期性影响。

面向高校、科研院所的产业推广与应用是EDA企业培养市场生态、客户习惯的重要方式和手段。一方面,为支持教学和科技研发创新,包括EDA工具在内的软硬件产品生产商均有面向高校、科研院所推出“教育版”产品,产品售价普遍低于商业化产品。另一方面,面向EDA工具的推广与应用,主流EDA企业均高度重视院校市场,推出各自的“高校计划”,面对院校方以成本价或赠与的方式进行产品销售,并在院校师生使用产品进行教学和科研中提供EDA产品技术支持与服务。

EDA工具技术发展趋势特征

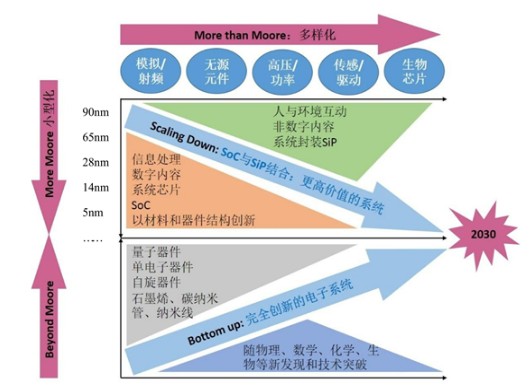

1、后摩尔时代技术演进驱动EDA技术应用延伸拓展

后摩尔时代的集成电路技术演进方向主要包括延续摩尔定律(More Moore)、扩展摩尔定律(More than Moore)以及超越摩尔定律(Beyond Moore)三类,主要发展目标涵盖了建立在摩尔定律基础上的生产工艺特征尺寸的进一步微缩、以增加系统集成的多重功能为目标的芯片功能多样化发展,以及通过三维封装(3D Package)、系统级封装(SiP)等方式实现器件功能的融合和产品的多样化。伴随芯片技术的持续发展,人工智能、高性能计算、新一代信息技术、物联网等新应用不断涌现,技术和应用发展的叠加让芯片技术和功能复杂度不断提升,同时带来对集成电路设计工具(EDA)的新发展需求。其中,面向延续摩尔定律(More Moore)方向,单芯片的集成规模呈现爆发性增增长,为EDA工具的设计效率提出更高要求。面向扩展摩尔定律(More than Moore)方向,伴随逻辑、模拟、存储等功能被叠加到同一芯片,EDA工具需具备对更强复杂功能设计的支撑能力。面向超越摩尔定律(Beyond Moore)方向,新工艺、新材料、新器件等的应用要求EDA工具的发展在仿真、验证等关键环节实现方法学的创新。

图4 后摩尔时代集成电路技术演进路径

2、设计方法学创新辅助平抑芯片设计成本

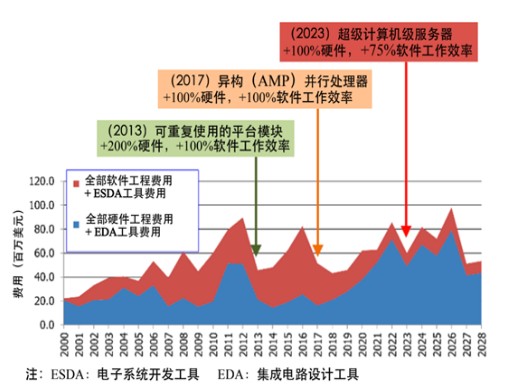

EDA工具的发展创新极大程度提高了芯片设计效率,一直以来是推动芯片设计成本保持在合理范围的重要方式。根据加州大学圣迭戈分校Andrew Kahng教授在2013年的推测,2011年设计一款消费级应用处理器芯片的成本约4000万美元,如果不考虑1993年至2009年的EDA技术进步,相关设计成本可能高达77亿美元,EDA技术进步让设计效率提升近200倍。整体看,既往及今后一段时间,推动设计效率提升的相关技术进步包括可重复使用的平台模块、异构(AMP)并行处理器的应用等。

图5 EDA技术进步对芯片设计成本的影响

在后摩尔时代,由“摩尔定律”驱动的芯片集成度和复杂度持续提升将为EDA工具发展带来新需求。在设计方法学层面,EDA工具的发展方向主要包括系统级或行为级的软硬件协同设计方法、跨层级芯片协同验证方法、面向设计与制造相融合的设计方法和芯片敏捷设计方法四方面。其中,系统级或行为级的软硬件协同设计方法可以让设计师在完成芯片行为设计的基础上自动完成后续的芯片硬件的具体实现,同时支持同步开展应用软件的开发,以达到设计效率提升的目的。跨层级芯片协同验证方法则强调验证工作实现芯片设计与封装、印制电路板(PCB)甚至整个应用系统相组合的跨层级协同验证,以确保设计的正确性。面向设计与制造相融合的设计方法则追求在芯片设计的各个阶段实现与制造工艺的融合,以期提升芯片最终生产良率。芯片敏捷设计方法则通过算法和软件需求定义芯片架构,结合模板元编程(Meta-Programming)和高层次综合(HLS)的设计方法,实现快速设计和快速迭代。

3、人工智能技术将在EDA领域扮演更重要角色

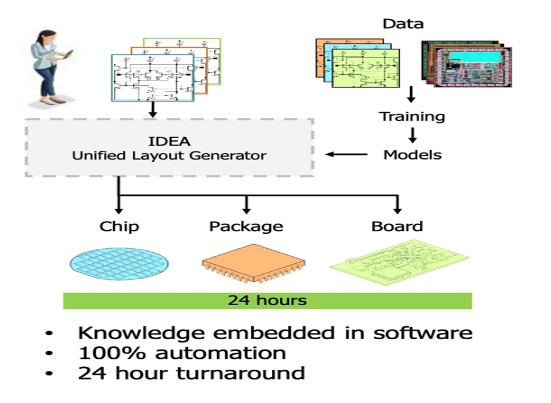

人工智能(AI)技术应用于EDA领域始于20世纪80年代,一直以来受制于运算能力不强、AI性能不理想、芯片设计的数据需求量不够大等因素,导致AI技术与EDA的融合并不充分。近年来,伴随芯片设计基础数据量的不断增加、系统运算能力的阶跃式上升,人工智能技术应用在EDA工具领域的算法和算力需求正在被更好地满足。此外,芯片复杂度的提升以及设计效率要求的提高同样要求人工智能技术赋能EDA工具的升级,辅助降低芯片设计门槛、提升芯片设计效率。2017年美国国防部高级研究计划局(DARPA)推出的“电子复兴计划(ERI)”中的电子设备智能设计(IDEA)项目,描绘出新的AI技术赋能EDA工具发展目标与方向。其中提出目标实现“设计工具在版图设计中无人干预的能力”,即通过人工智能和机器学习的方法将设计经验固化,进而形成统一的版图生成器,以期实现通过版图生成器在24小时之内完成SoC(系统级芯片)、SiP(系统级封装)和印刷电路板(PCB)的版图设计。

图6 IDEA项目设计框架

4、云技术在EDA领域的应用日趋深入

一直以来,企业对核心知识产权、工艺设计套件(PDKs)等高度敏感数据的安全顾虑是限制云技术在EDA领域应用推广的重要阻碍。近年来,伴随相关技术方式的逐步成熟、用户使用习惯的改变,叠加应用云技术进行芯片设计研发方面的综合成本、效率优势,云技术正在EDA领域获得快速发展。伴随EDA云平台的逐步发展,云技术在EDA领域的应用第一可以有效避免芯片设计企业因流程管理、计算资源不足带来的研发风险,保障企业研发生产效率;第二可以有效降低企业在服务器配置和维护方面的费用,让企业根据实际需求更加灵活地使用计算资源;第三可以让芯片设计工作摆脱物理环境制约,尤其在新冠疫情带来的居家办公需求下让EDA云平台发挥了重要作用;第四有助于EDA技术在教育领域的推广和应用,支持设计人才培养等相关工作。此外,类似RISC-V的开源化模式也更适合采用云平台进行相关如基于RISC-V内核芯片的芯片设计工作。

责任编辑:tzh

-

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展2026-01-21 1092

-

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--中国EDA的发展2026-01-20 2459

-

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况2026-01-19 1849

-

国内EDA工具AI技术应用现状及发展动态分析2024-04-12 1875

-

EDA工具市场发展趋势分析2021-06-12 4062

-

EDA技术的发展,EDA技术的基本设计方法有哪些?2021-04-21 4343

-

robei EDA简介Robei可视化EDA工具2021-01-05 7899

-

EDA技术发展概况_EDA技术的发展趋势2020-07-09 4917

-

EDA技术有什么特征?2019-10-08 2197

-

EDA技术从何而来?EDA技术发展历程2019-02-21 4179

-

简述什么是eda技术_eda技术好学吗_如何学习EDA技术2018-04-27 39455

-

什么是EDA工具?目前全球EDA行业的现状是什么?2018-04-26 40990

-

EDA设计流程及其工具2016-12-11 1199

-

EDA技术应用与发展之管窥2012-09-12 2509

全部0条评论

快来发表一下你的评论吧 !