探究FPGA的多速率信号处理技术

描述

多速率技术已广泛应用于数字音频处理、语音处理、频谱分析、无线通信、雷达等领域。作为一项常用信号处理技术,FPGA攻城狮有必要了解如何应用该技术,解决实际系统中的多速率信号处理问题。

01什么是多速率信号处理

多速率信号处理,是指对同时存在两个以上数据速率的系统进行信号处理。在软件无线电(SDR)中,多速率技术得到普遍应用。在实际系统中,需要处理的数据量越来越大,并且对处理速度的要求越来越高,经常是Gb/s级别。多速率技术已广泛应用于数字音频处理、语音处理、频谱分析、无线通信、雷达等领域。

一般情况下,多速率系统能够比单速率系统更为有效地处理信号,在多速率系统内部各节点,根据设计需要,进行内插和抽取,从而满足AD/DA和基带速率需求。

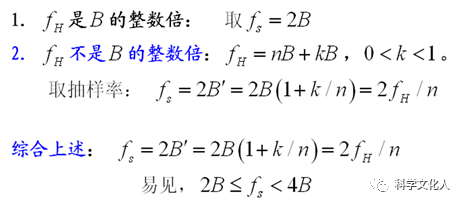

在工程中,中频采样技术使用广泛,在中频对模拟信号进行数字化,依据的是带通采样定理。我们知道,对于低通模拟信号进行抽样,遵循奈奎斯特抽样定理,也就是抽样频率fs需要大于等于模拟信号最高频率fH的2倍,才能对数字化后的信号无失真恢复出原始信号。

学习过通信原理的同学都知道,通过调制解调技术,我们可以实现频谱搬移,并实现远距离通信。从基带信号到射频信号,从理论上讲,我们可以一步到位,直接将低频的基带信号调制到射频,这样的技术叫零中频。零中频结构简单,有利于集成和降低成本,在终端获得广泛应用。当然零中频存在两个弱点:直流偏置和闪烁噪声。直流偏置因本振泄露导致,闪烁噪声则与频率有关,频率越高,闪烁噪声越小,反之越大。

在早期的实际系统中,基带信号经过两步走达到射频:先将基带调制到中频,达到几百MHz,然后再次调制,达到射频,GHz级别。接收机则采用两次降频到基带。这样的结构叫超外差结构,应用广泛。

再回到带通采样。对于带通信号,其频谱位于某一频率区间,其带宽B=fH-fL,则此时的采样率fs需满足:

由于此时的采样率已超过了奈奎斯特定义的最低采样率,进而被称为过采样。过采样的好处是,可以将采样过程中固有的量化噪声均匀地分散在更大的带宽上,从而降低有效信号带宽上的噪声功率。再通过数字滤波器对带外噪声进行衰减,从而得到比临界采样信号更优的信噪比。

ADC的采样率过高,会给FPGA进行数据处理带来压力。我们一方面希望利用过采样的优点,另一方面,我们不希望FPGA处理过于复杂,于是通过降低数字信号采样率来满足基带处理需求,这就是抽取。

实际上,抽取并不难理解,我们可以与生活中的抽样调查联系起来。样本(数据)过大,统计(处理)起来就复杂。比如,让你去调查一下,成都的FPGAer的平均薪资。你可能会从招聘网站、朋友、同事等了解到相关信息,从而大概知道成都的FPGA平均薪资水平,当然不可能去把每一个FPGAer都问一遍,再做统计,于是有了抽样调查。

在利用FPGA进行信号处理时,抽取后的信号,数据率相对较低,因而能够有效降低系统对FPGA资源的占用。这就好比吃饭,你不能吃太快,送到嘴里先嚼几下再咽下去,降低吞的频率。

在一些系统中,则需要提高采样率,即为内插。将数字基带信号搬移到目标载频后,通过内插的方式得到更高的采样率,从而驱动高速DAC。为什么需要采样率高的DAC呢?这是因为DAC采样率越高,其输出端频谱图像之间的频域分离度越高,这样可以简化DAC后的模拟滤波器工作,提升信噪比。

以抽取和内插为代表的多速率信号处理技术的典型应用即为数字下变频DDC(Digital Down Conversion)和数字上变频DUC(Digital Up Conversion),这对于从事无线通信的同学来说,耳熟能详。

02

多速率信号处理的核心

总结起来,多速率信号处理,其目的在于改变原有数字信号的频率,通过抽取实现降低采样速率,通过内插来实现提高采样速率,但抽取或内插的前提是,需要保证有用信号频带内没有频谱混叠,继而需要各种新式的滤波器来实现。

多速率信号处理的核心:抽取、内插、低通滤波。实质上不难看出,设计的难点在于滤波器。多速率滤波器实质上是具有线性相位的FIR滤波器,通常滤波器需要工作在很高的速率上,因而需要考虑如何减少运算量和运算复杂度。

常用的多速率滤波器主要有:多速率FIR滤波器、积分梳状(CIC)滤波器和半带滤波器。

多速率FIR滤波器由于信号速率高,需要工作在很高的频率上,大量的乘法器参与运算会导致资源消耗多、功耗大等问题,这对于FPGA片内有限的资源来说,实际操作不太可取,因此实际使用较少。CIC滤波器和半带滤波器结构简单,实现方便,性能良好,在软件无线电中得到广泛使用。

特别是在DDC和DUC中,将不同的滤波器进行组合实现需求。例如,在接收机中,采用CIC滤波器作为第一级滤波器,完成抽取和低通滤波;在第二级采用FIR实现的半带滤波器,此时的工作频率较低,滤波器参数得到优化,可以用较低的阶数实现,节省资源和降低功耗。

对于无线通信,收、发两端都存在多速率处理,这里我们将发射机的多速率处理叫做多速率发送处理器,相应地,在接收端,叫做多速率接收处理器。

需要注意的是,如果我们只做基带信号处理,可能你是不会去接触如何设计滤波器,完成DDC或者DUC。同样,在基带处理中,因分工问题,你可能无法一个人完成整个链路的设计,但对于处于边工作边学习阶段的我们,谁甘愿一直做一个模块,到时候只会一个功能部件设计,其余的不会,这会对职业生涯发展构成威胁。

回到对多速率发送和接收处理器的讨论中,看看其一般设计过程。

03多速率发送处理器设计

对于发射端来讲,基带信号需要经过多速率发送处理器处理后,再进行数/模转换(DAC)。多速率发送处理器的一般结构,主要由四部分组装成:可编程插值FIR滤波器(RCF)、两个固定系数的FIR滤波器(FFIR)、高速的CIC插值滤波器以及数控频率振荡器(NCO)。

RCF完成对输入信号的采样,采样倍数1~16,由于需要工作在高速时钟下,其阶数一般不会太高。FFIR对输入信号进行2倍采样,如果FFIR的带宽达到输入采样率的一半,则能够有效抑制带外信号的噪声。CIC滤波器一般采用2~5阶,完成对输入信号1~32倍的采样,其有效的线性相位冲激响应是由其插值率决定。NCO主要完成两件事:一是产生载波频率,二是完成数据调制的复数乘法。NCO需要高比特数的频率调谐精度,并需要抑制幅度和相位抖动来无杂散动态范围。

04多速率接收处理器设计

在无线通信中,多速率接收处理器在ADC之后工作,主要包含五部分:数控频率振荡器(NCO)、高速的CIC抽取滤波器、可编程抽取FIR半带滤波器(FIR HB)、两个固定系数的FIR滤波器(FFIR)、以及自动增益控制模块(AGC),其结构如图所示。

其中,NCO、CIC、FIR HB、FFIR的功能和实现与发送端类似。AGC模块主要自适应地调整信号通道增益,确保不超出模拟信号的线性范围,或保证数字信号不超出有效字长的限制,从而保证信号在一个动态范围都能工作。

在工程中,我们需要关注以下设计要点:

设计要点

抽取:下采样器+抗混叠滤波器设计

插值:抗镜像滤波器+上采样器设计

CIC滤波器设计

FIR半带滤波器设计

多相分解技术

编辑:jq

-

进群免费领FPGA学习资料!数字信号处理、傅里叶变换与FPGA开发等2025-04-07 15068

-

什么是多速率信号处理2022-06-21 3812

-

基于FPGA 的雷达信号采集系统设计2017-11-22 5242

-

基于FPGA的多速率卷积编码器的设计2017-11-18 1862

-

多速率信号处理系统(通过FPGA设计)2017-11-01 885

-

基于FPGA和多DSP的多总线并行处理器设计2017-10-19 959

-

基于FPGA数字信号处理2015-10-30 1146

-

多速率信号处理笔记——基础理论2014-08-22 2412

-

FPGA编程LVDS信号图像处理技术2014-07-17 9835

-

多速率转换信号频谱研究2011-09-05 2891

-

卫星导航软件接收机多采样率信号处理技术2011-02-11 1057

-

FPGA在软件无线电中的工程应用之多速率信号处理篇2010-02-09 737

-

基于CPCI总线的通用FPGA信号处理板的设计2009-11-28 1429

-

基于多速率DA的根升余弦滤波器的FPGA实现2009-11-13 1981

全部0条评论

快来发表一下你的评论吧 !