浅析modelsim 自动化 高效独立仿真含vivado IP核的工程

描述

1.modelsim编译vivado库

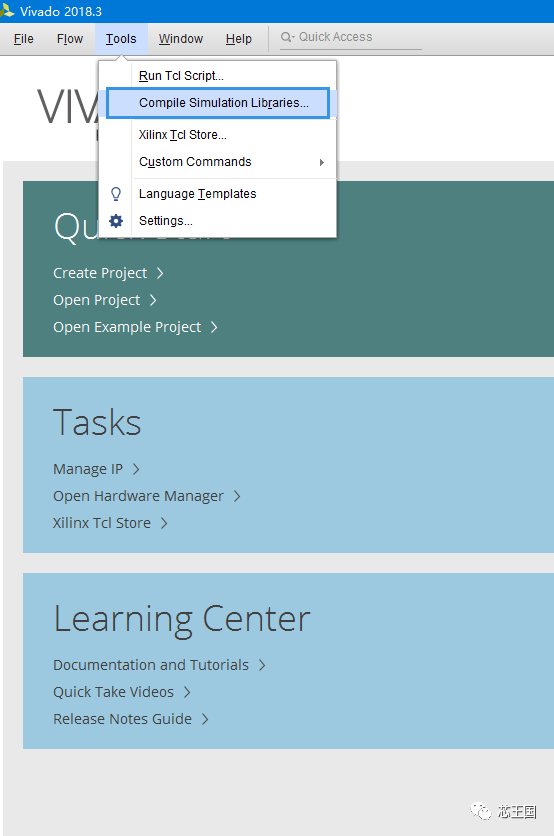

1)双击启动vivado软件,如下图操作。

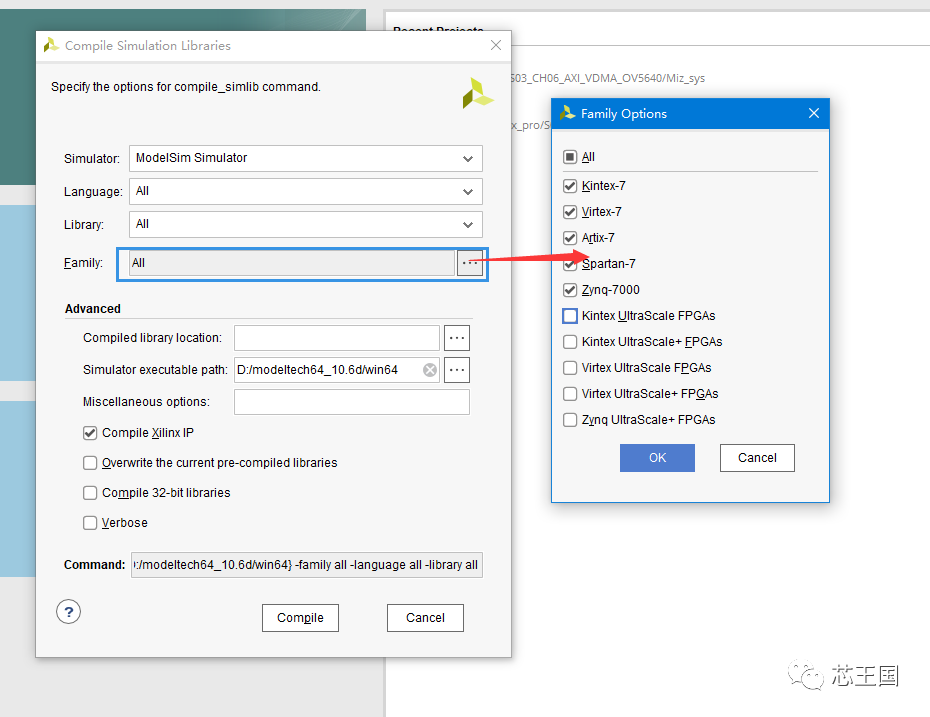

2)Simulator:选对应的,

Language:都选all,

Verilog与vhdl都用可能用到,

Library:unisim 功能仿真,simprim 时序仿真,选择all,

Famliy:如下图看你用那些,全勾选的话编译时间会很长而且会很大,所以按需要勾选。

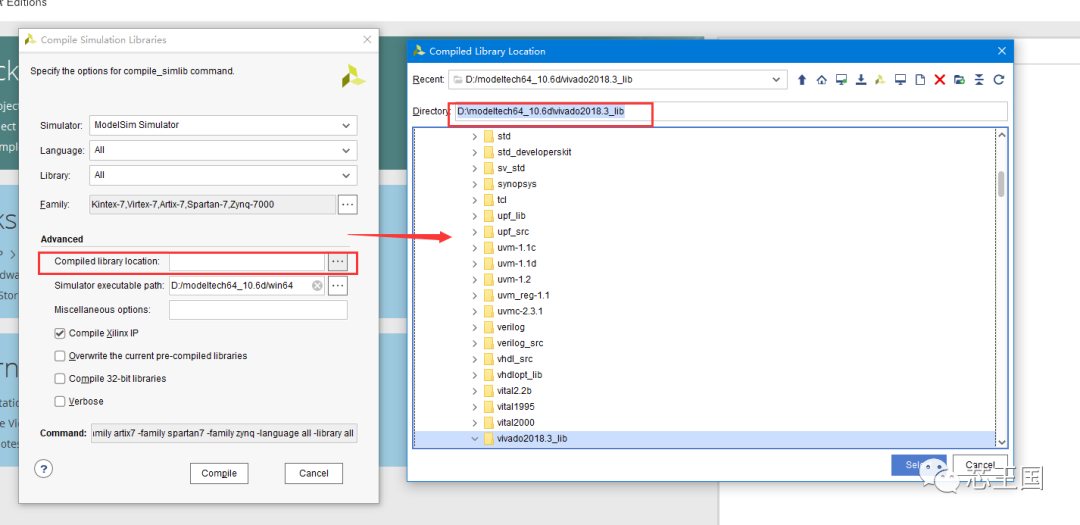

3)编译库存放位置,一般都是放置到modelsim目录下面,需要自己新建文件夹并命名,如图所示。

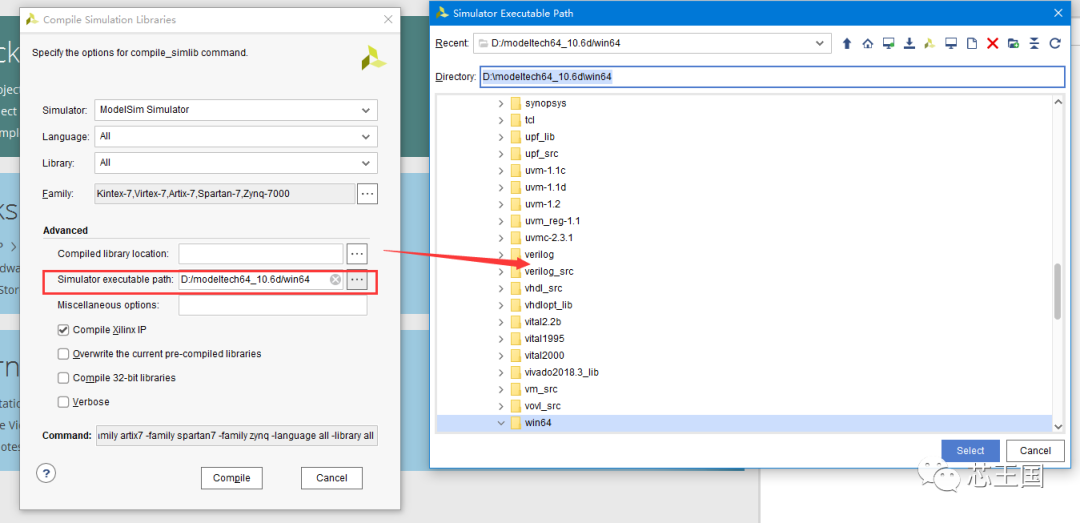

4)编译器路径,vivado会自动识别出路径,没有的话自己手动添加,选到win64文件夹就行了。

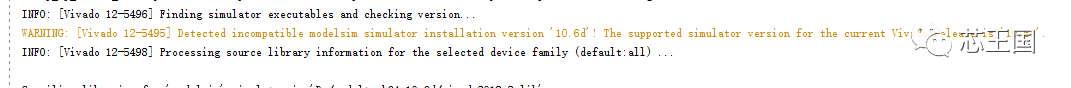

5)配置完成,点击Complie就进行编译后面有下图警告,可以不用在意,这警告的意思是vivado2018.3适合modelsim10.6c版本,要求不高可以忽略。

最后出现下图信息列表,没有错误最好,警告可以忽略。

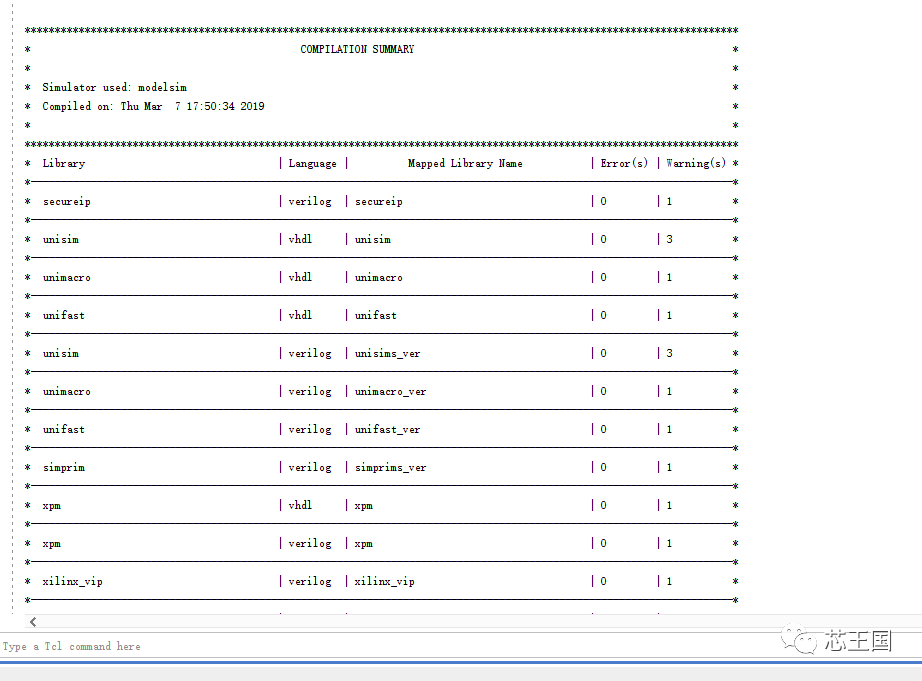

2.指定modelsim安装路径和编译库

启动vivado 进入Tools —> setting,按下图操作,对应你用的仿真器,最后点击Apply,OK退出。

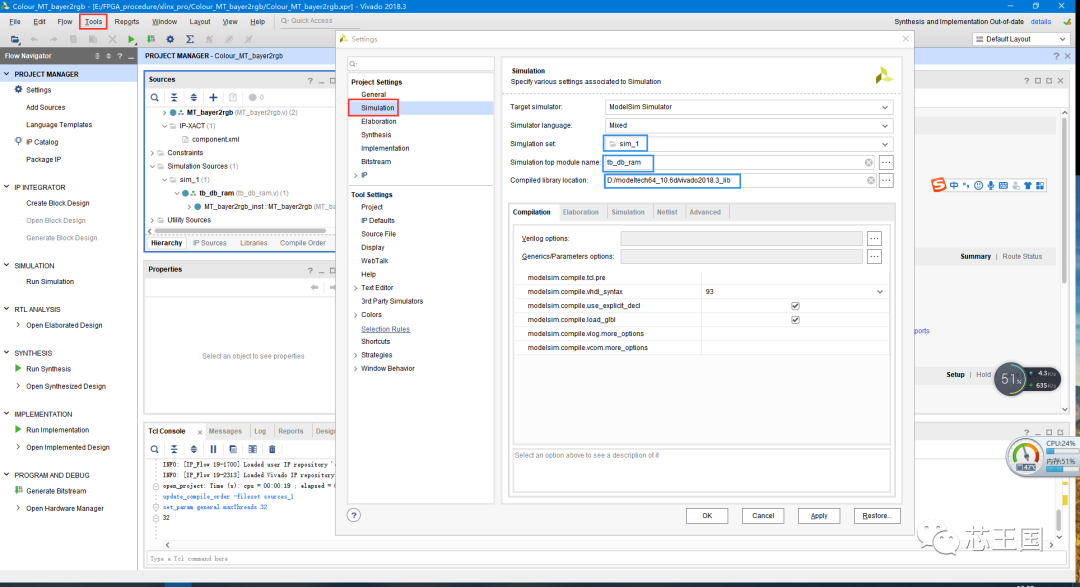

3.选择vivado仿真的工具、tb文件以及编译库路径。

1)Tools -> Setting -> Simulation,如蓝框所示:

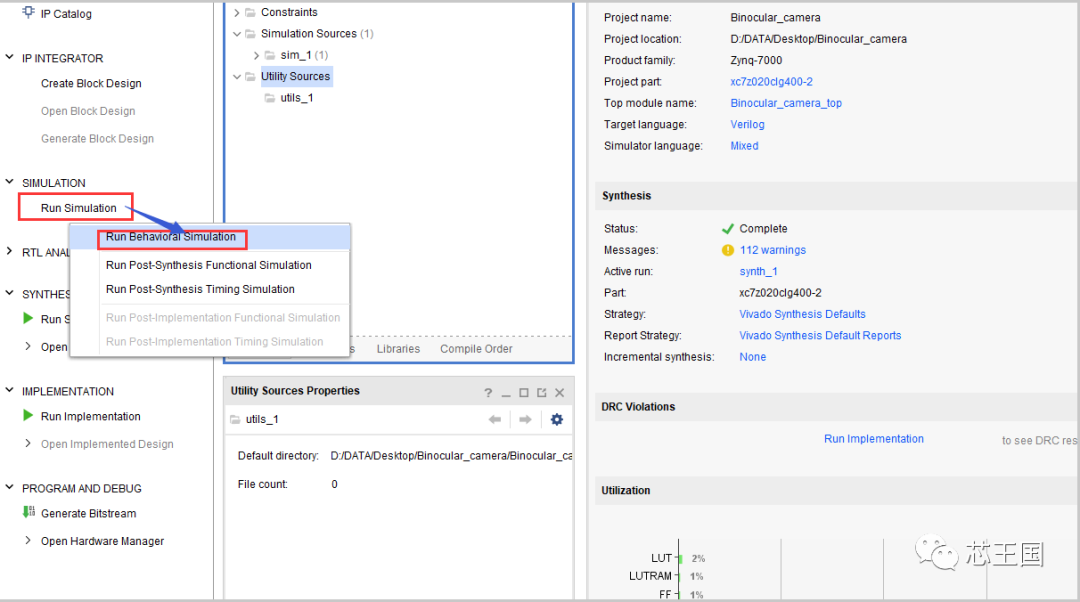

4.设置完成后启动仿真。

但是这样是联合仿真,每次修改设计重新启动仿真都需要退出modelsim,回到vivado重新启动。这样费时费力,效率极低。因此下面开始怎么实现自动化独立仿真。

5.自动化独立仿真

接着第4步,vivado启动modelsim后不要退出。

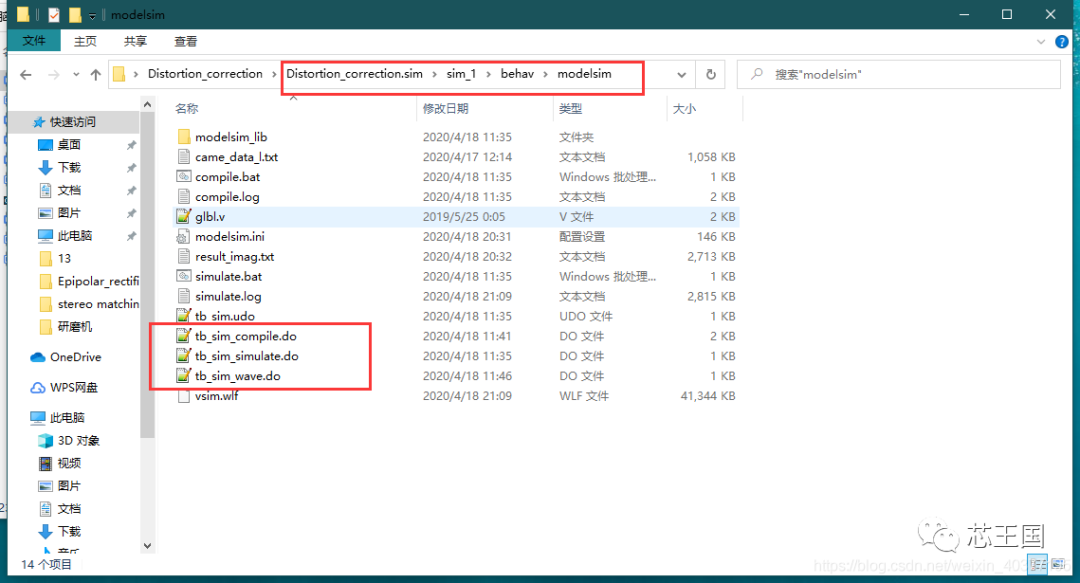

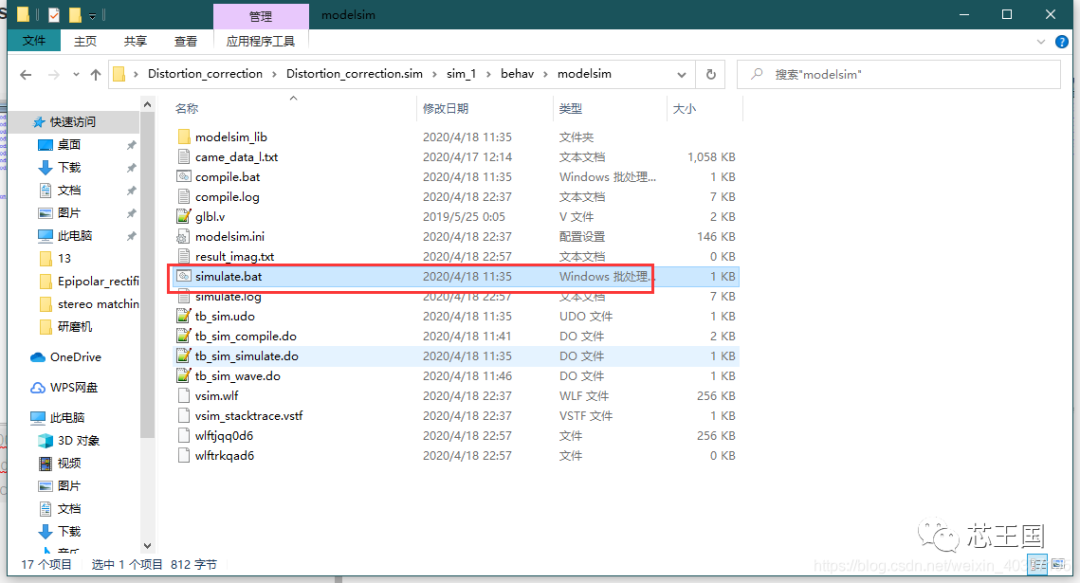

1)vivado自动在工程目录下生成下面的目录和文件,红框中就是我们需要改的。

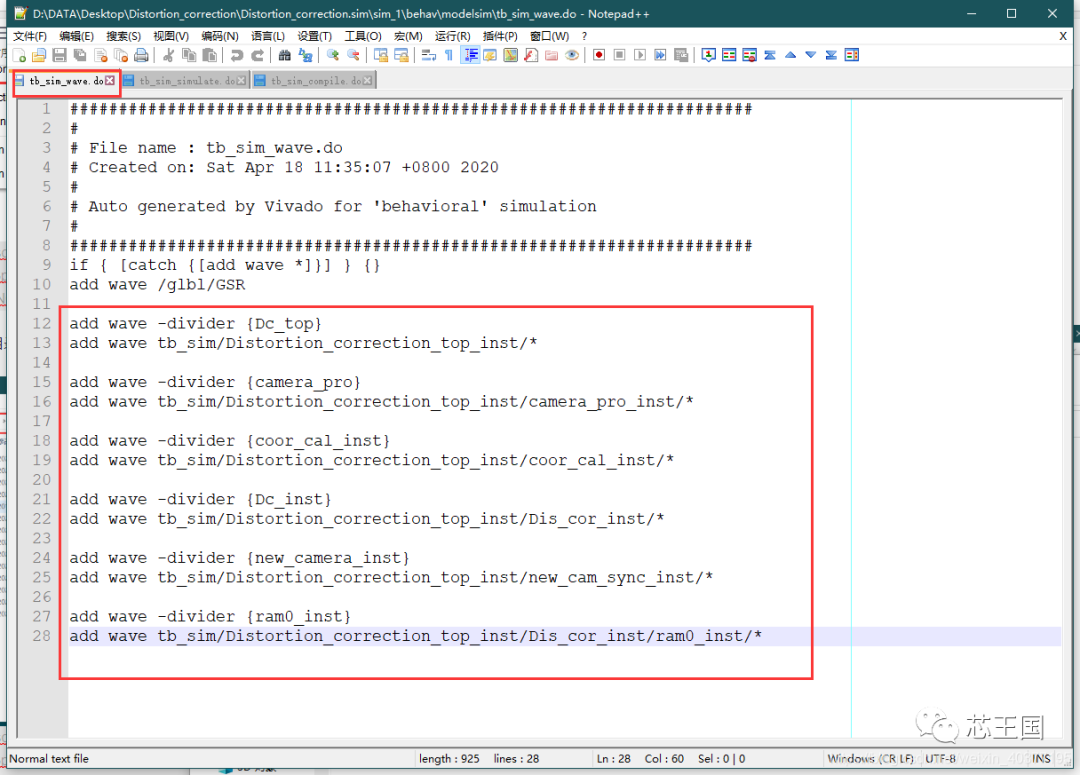

2)修改tb_sim_wave.do文件,把模块信号添加到波形显示。

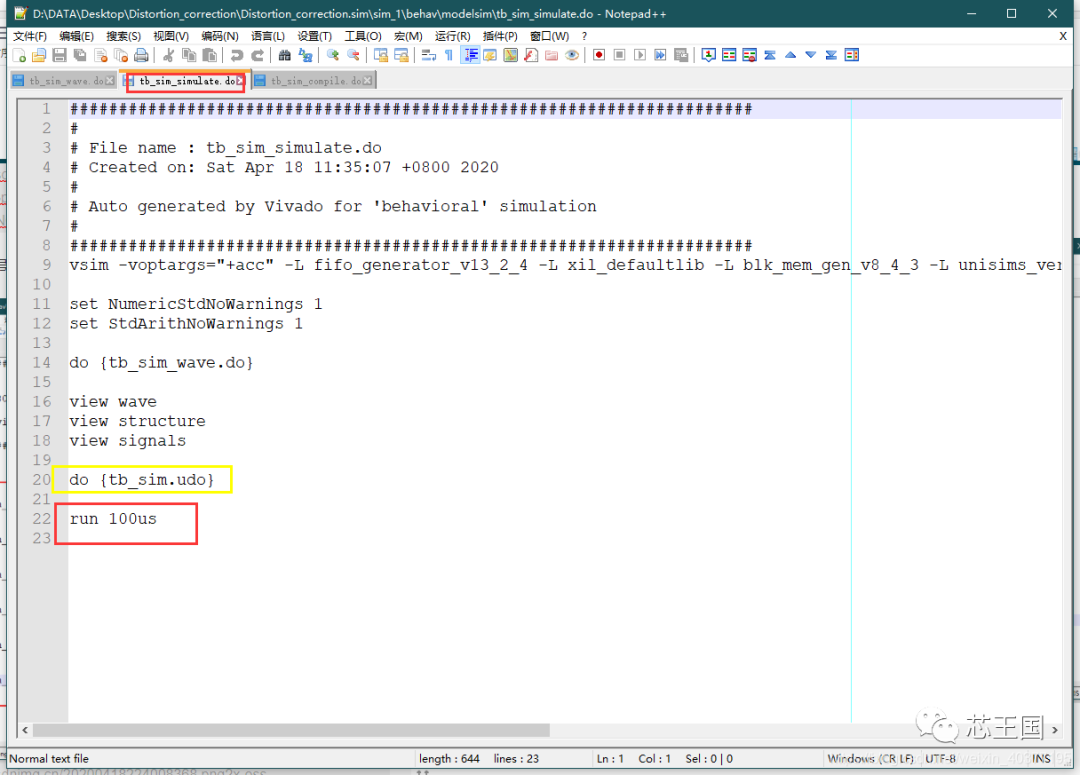

3)修改tb_sim_simulate.do文件,这个文件我只修改了仿真时间。可以看出这个do文件调用了tb_sim.udo,这个文件应该可以用户自己添加,具体我现在也不知道,明白了以后再来分享。

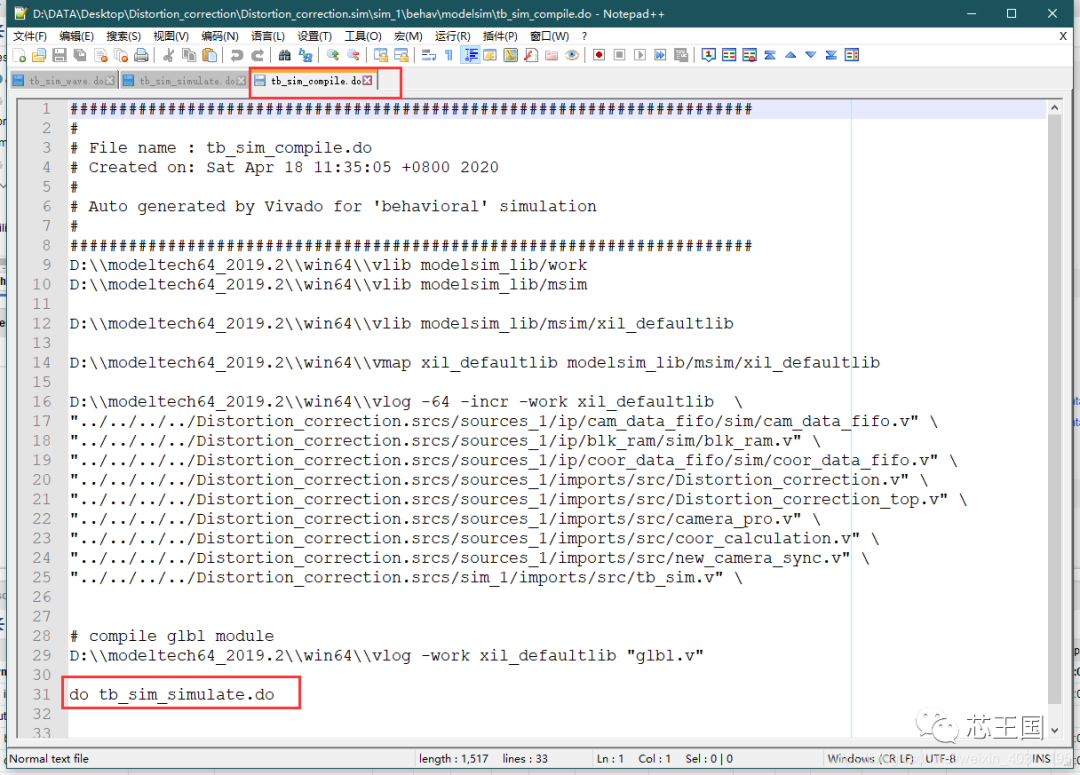

4)修改修改tb_sim_compile.do文件,这个文件最后一行是 quit ,把这行注释掉或者删除,添加 do tb_sim_simulate.do 命令。

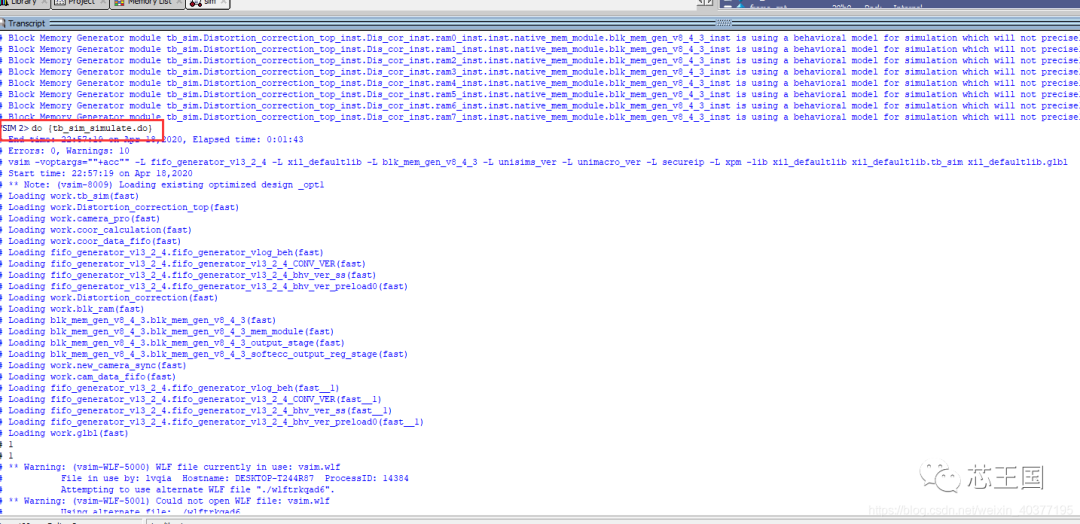

5)在modelsim 命令框输入 do tb_sim_compile.do ,就可以独立并且自动化仿真了。

6)以后就可以直接双击simulate.bat文件启动modelsim,这儿要记得输入 do tb_sim_compile.do 这个命令,而不是 do tb_sim_simulate.do。

7).bat文件无法启动modelsim问题请看:

modelsim自动化仿真 运行.bat闪退问题

4.总结

这是其中一种自动化仿真的方法,是自己摸索出来的(还有一种方法我没试过),有问题或者有更好的建议希望多多交流!!!

编辑:jq

-

怎样单独使用modelsim仿真xilinx呢?2023-12-04 3625

-

vivado软件和modelsim软件的安装方法2023-08-07 9494

-

Vivado调用Modelsim仿真2023-07-24 5883

-

VCS独立仿真Vivado IP核的问题补充2023-06-06 3147

-

Vivado生成IP核2023-04-24 3498

-

介绍用ModelSim独立仿真带Vivado IP核的仿真方案2023-02-06 6353

-

modelsim自动化独立仿真介绍2022-12-21 1684

-

使用VCS仿真Vivado IP核时遇到的问题及解决方案2022-08-29 5068

-

Vivado调用Questa Sim或ModelSim仿真小技巧2021-09-02 10545

-

如何用Python实现Vivado和ModelSim仿真自动化?2021-05-03 2769

-

VCS独立仿真Vivado IP核的一些方法总结2021-03-22 5612

-

modelsim 仿真 altera IP核(ROM,RAM实例2015-11-19 6119

-

如何仿真IP核(建立modelsim仿真库完整解析)2012-08-15 5721

全部0条评论

快来发表一下你的评论吧 !