ZYNQ PS + PL异构多核案例开发手册之1axi_gpio_led_demo案例

今日头条

描述

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。

axi_timer_pwm_demo案例

1 案例功能

案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板PL端LED5的状态。

1.1 操作说明

1.2.1 基于裸机测试

加载PS端裸机程序、PL端程序后,即可看到评估底板的LED5每隔0.5s亮灭一次。

1.2.2 基于Linux测试

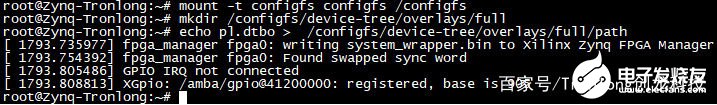

将本案例的动态设备树镜像文件pl.dtbo和PL端.bin格式可执行文件复制到“/lib/firmware/”目录下,并将PL端可执行文件重命名为system_wrapper.bin,然后执行如下命令加载设备树文件和PL端可执行文件。

Target# mount -t configfs configfs /configfs

Target# mkdir /configfs/device-tree/overlays/full

Target# echo pl.dtbo 》 /configfs/device-tree/overlays/full/path

图 4

由上图可知PL端实现的GPIO控制器为905。

请执行如下命令,配置GPIO为输出模式。

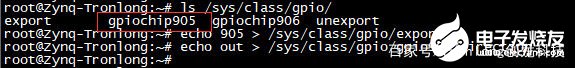

Target# ls /sys/class/gpio/

Target# echo 905 》 /sys/class/gpio/export

Target# echo out 》 /sys/class/gpio/gpio905/direction

图 5

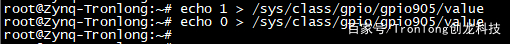

执行如下命令,即可控制评估底板LED5的亮灭。

Target# echo 1 》 /sys/class/gpio/gpio905/value

Target# echo 0 》 /sys/class/gpio/gpio905/value

图 6

1.1 Vivado工程说明

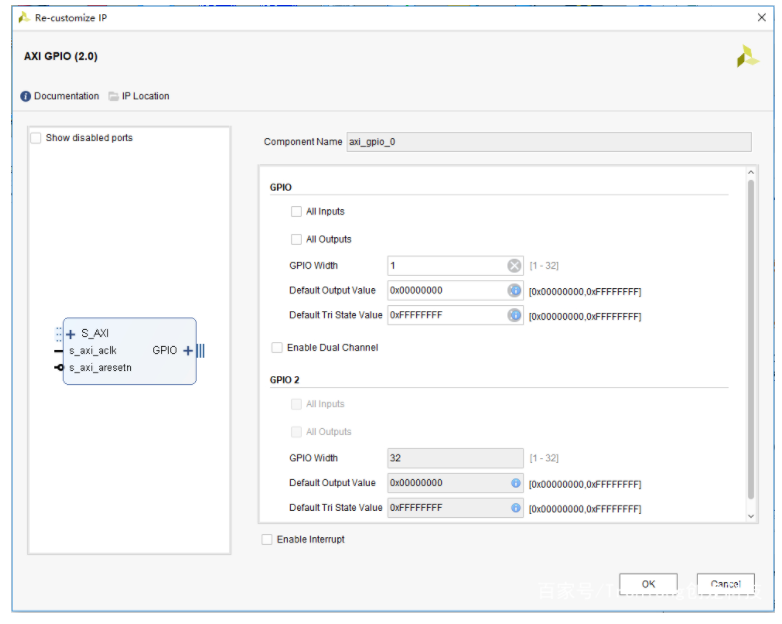

进入BLOCK DESIGN开发界面,双击IP核框图,可查看IP核的具体配置信息。

图 7

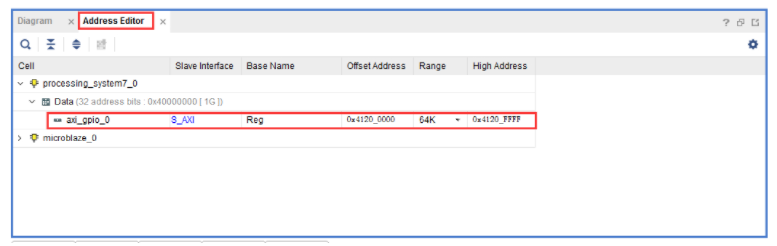

点击BLOCK DESIGN开发界面下的“Address Editor”选项,可查看IP核分配的地址为0x41200000,PS端可通过该地址对IP核进行控制。

图 8

1.2 IP核配置

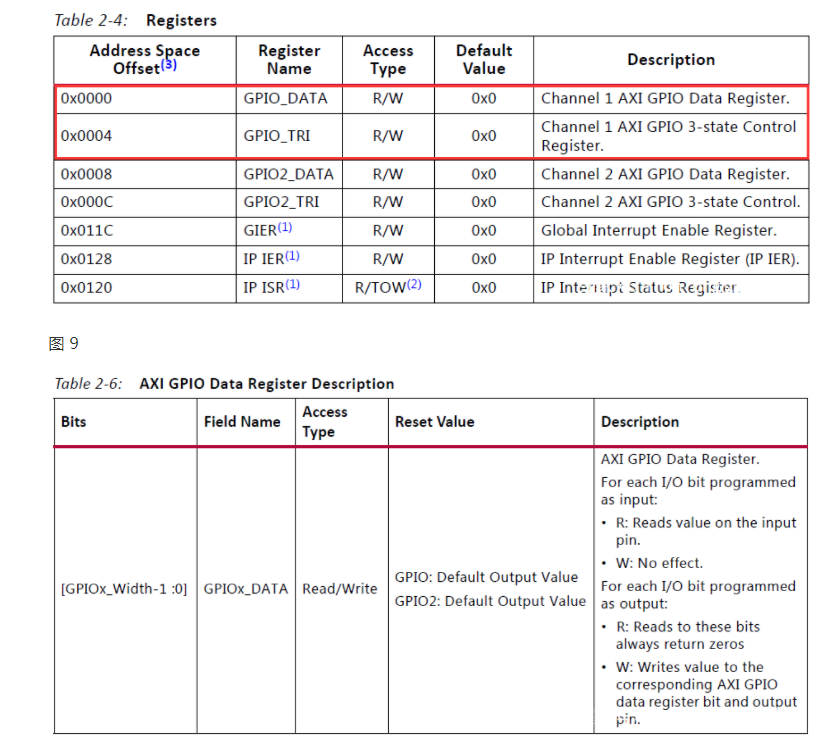

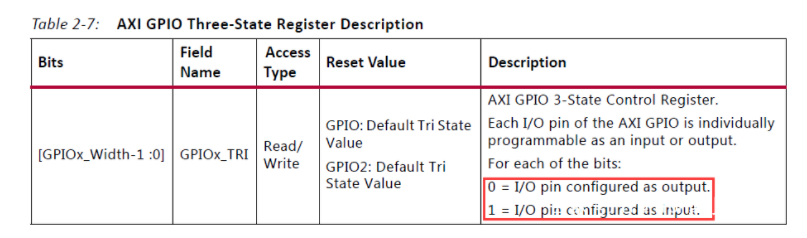

AXI GPIO IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg144-axi-gpio.pdf》。根据文档,通过寄存器GPIO_TRI可将GPIO配置为输入/输出模式;通过寄存器GPIO_DATA可将GPIO配置为高/低电平,以及可读取GPIO的电平状态。

图 10

图 11

创龙科技基于TL6678ZH-EVM评估板提供CameraLink、SDI、HDMI、PAL的测试案例,客户仅需要专注上层应用开发。

如需获取案例源码、TL6678ZH-EVM评估板或其他产品详细资料,欢迎留言或者私聊!

-

DR1 系列核心板 PS+PL 异构多核实战案例手册(一)2026-01-14 302

-

复旦微PS+PL异构多核开发案例分享,基于FMQL20SM国产处理器平台2024-08-22 2110

-

FM20S用户手册-PS + PL异构多核案例开发手册2024-07-25 1517

-

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”2023-02-01 5143

-

基于Xilinx Zynq-7010/20系列——PS+PL异构多核案例开发手册2023-01-03 1512

-

AXI_GPIO简介与使用指南2022-07-19 6816

-

ZYNQ PS + PL异构多核案例开发手册之axi_timer_pwm_demo案例2021-05-28 2086

-

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用2021-02-01 8206

-

Xilinx ZYNQ开发GPIO的三种方式:MIO、EMIO、AXI_GPIO2020-12-26 5589

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 7011

-

ZYNQ中DMA与AXI4总线2020-11-02 5317

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7569

-

ZYNQ 的三种GPIO :MIO、EMIO、AXI2017-02-08 3775

全部0条评论

快来发表一下你的评论吧 !