如何通过自动化脚本实现Questasim和Verdi的联合仿真

描述

Verdi是用来仿真以及debug波形的工具,但它不能够用来编译verilog和systemverilog文件,所以需要借助第三方EDA工具去做编译的工作。

这里主要分享一下使用questasim和verdi的联合仿真。

由于verdi工具支持FSDB格式的波形文件,所以在仿真时要把文件的信号转存到FSDB格式的波形文件中,这里需要借助一个共享的库文件:novas_fli.so.它通常位于目录:

《VERDI_HOME》/share/PLI/MODELSIM/${PLATFORM}。

首先需要把上面的库文件路径添加到系统的环境变量LD_LIBRARY_PATH 中,如下:

setenv LD_LIBRARY_PATH ${VERDI_HOME}/share/PLI/MODELSIM/${PLATFORM}:$LD_LIBRARY_PATH

然后在仿真的时候,命令行中添加如下:

vsim -pli novas_fli.so work.test do dump_fsdb_questa.tcl +fsdb+autofluash

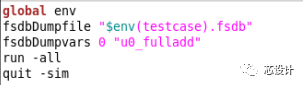

dump_fsdb_questa.tcl的内容如下:

fsdbDumpfile “test.fsdb”fsdbDumpvars 0 “test”run

02

举例说明

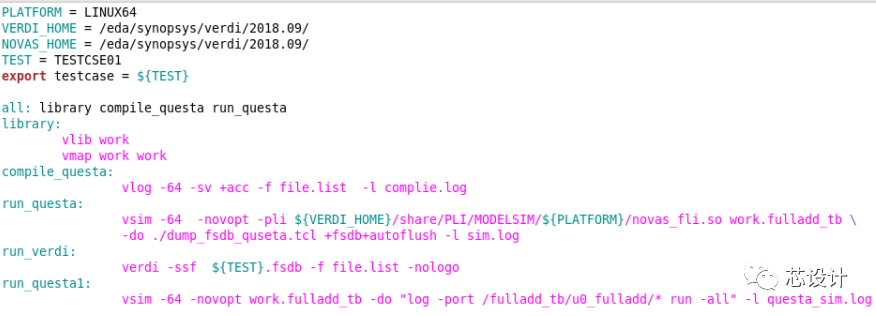

比如要验证一个简单的全加器,其Makefile的自动化脚本如下:

在dump_fsdb_questa.tcl的内容如下:

在terminal中输入下面指令(运行编译和仿真):

make all

编译仿真通过后,会在在当前的工作目录中生成:TESTCASE01.fsdb文件。

之后在terminal中输入下面指令(打开波形文件):

make run_verdi

本篇文章主要分享了如何通过自动化脚本的方式实现Questasim和Verdi的联合仿真教程。

原文标题:Questasim和Verdi的联合仿真教程

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

vcs和vivado联合仿真2025-10-24 197

-

请教VCS和verdi怎么联合使用2015-01-22 8173

-

手机自动化测试2016-07-08 3542

-

自动化测试脚本开发技巧2011-03-26 794

-

vcs和verdi的调试及联合仿真案例2020-09-22 9785

-

介绍10个Python自动化脚本2022-10-17 1264

-

10个杀手级的Python自动化脚本2022-11-28 994

-

如何创建自动化脚本2023-01-04 4389

-

10个杀手级的Python自动化脚本分享2023-01-06 1210

-

分享10个实用的Python自动化脚本2023-01-21 1839

-

使用Python脚本实现自动化运维任务2023-04-08 2373

-

全网最实用的Verdi教程12023-05-05 21454

-

Questasim与Visualizer的livesim仿真如何启动呢?2023-10-10 1824

-

keil自动化编译脚本2023-10-16 3519

-

通过Python脚本实现WIFI密码的自动猜解2024-01-25 4736

全部0条评论

快来发表一下你的评论吧 !