基于QuartusⅡ和控制器实现总线通讯板的设计

描述

PC/104嵌入式控制PC出现于20世纪80年代末,并于1992年形成IEEEP966.1标准。它一方面继承了PC的所有资源,另一方面又对PC的各个方面做了优化设计,使其与IBM PC完全兼容,并具有体积小,功耗低,工作温度宽,可靠性高等特点。采用了独特的“自栈式”总线连接、模块化结构,使用起来灵活方便;采用面向对象的硬件设计方法,使得在PC/104标准上开发的扩展模块具有更强的通用性和更长的生命期;它以其优良的品质、高可靠性及模块化,广泛应用于工业控制、航空航天、军事、医疗、消防设备、智能仪器仪表、导航、通讯、数控、自动化生产设备、便携式计算机等领域。

CAN(Controller Area Network)总线是一种有效支持分布控制或实时控制的串行通信网络,采用多主协议,废除了传统的站地址编码,而采用对通信数据块进行编码的方法,使网络内节点个数在理论上不受限制。它具有总线仲裁、错误检测、自动重发等功能。由于采用了许多新技术及独特的设计,CAN总线具有高实时性、卓越性能、高可靠性、能独特灵活设汁和低廉价格,已广泛应用于工业现场、控制、智能大厦、小区安防、交通工具、医疗仪器、环境监控等众多领域。目前,它已被公认为是几种最有前途的现场总线之一。随着科技的发展,同一系统应用多种总线技术已经成为一种趋势。本设计利用FPGA完成PC/104总线和CAN总线之间的相互通讯,将两总线相结合,优势互补,使两总线有更大应用价值和更广阔的使用前景。

1 硬件设计

1.1 系统硬件结构

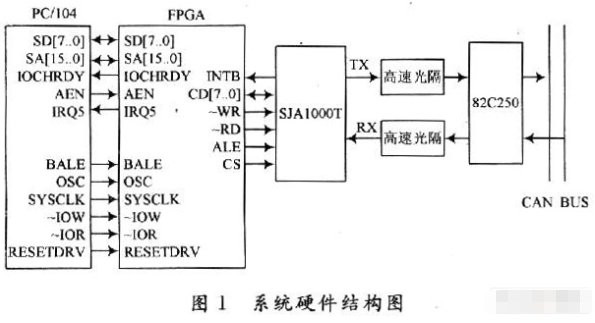

本设计采用PC/104模板形式,具有很强的方便性和可扩展性,其系统的硬件结构如图1所示。

由于PC/104总线采用的是地址数据总线分离的总线结构,而CAN总线协议控制器SJA1000T采用的是地址数据总线分时复用的总线结构,因此系统使用FPGA器件EP20K100实现总线转换和时序逻辑控制转换。该通讯板采用I/O映射方式,其内部寄存器地址为280H~2BFH。为了增强系统的抗干扰能力,在控制器SJA1000T与收发器82C250之间接入光电耦合器6N137。光耦6N137的上升时间典型值为30 ns,隔离电压为3 000 V,其支持最大频率值超过30 MHz。

1.2 FPGA设计

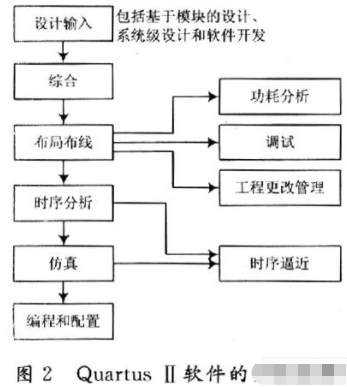

QuartusⅡ是Altera公司在21世纪初推出的FP-GA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAx+PlusⅡ的更新换代产品,其功能强大,界面友好,使用便捷。QuartusⅡ软件集成了Al-tera的FPGA/CPLD开发流程中所涉及的所有工具和第三方软件接口。QuartusⅡ软件的开发流程如图2所示。

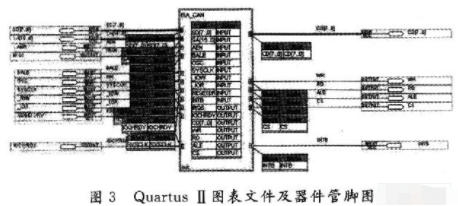

采用原理图输入和硬件描述语言相结合的方式,进行编译后写人器件中;同时可在线更改写入内容,修改和调试简单易行。FPGA的设计主要由两部分组成:第一部分实现时序逻辑控制信号的转换,第二部分实现地址译码和地址数据线的复用。QuartusⅡ图表文件及器件管脚如图3所示。

由于PC/104的地址总线和数据总线是各自独立的,SJA1000T的地址总线和数据总线是分时复用的,所以它们之间不能直接相连,必须通过时序逻辑控制,再配合软件来实现读/写操作。对SJA1000T的操作方法是:首先,对地址为CAN首地址+0(A2A1A0=000)的端口进行写操作(WR为低,有效),CANALE为高,有效,此时复用的地址、数据总线上的数据被视为地址信号,进入SJA1000T内部锁存器;然后,对地址为cAN首地址+1(A2A1A0=001)的端口进行读或写操作(RD/WR为低,有效),CANALE为低,上述中的地址信号已被锁存,此时复用的地址、数据总线上的数据被视为数据信号,这样即可完成对SJA1000T的各个寄存器和缓冲区的读或写操作。

1.3 硬件电路测试

主要检测硬件结构及电路板设计是否正确。建立一个简单的通讯连接,将两个通讯板连接进行测试,用通讯板A作为输出,通讯板B作为输入。编程通过通讯板A发送数据,内容为8个随机数,检测通讯板B接收数据,如果不同则作加1计数。反之将通讯板B作为输出,通讯板A作为输入,进行相同测试。测试200万次循环未见异常。

2 软件设计

2.1 软件流程图

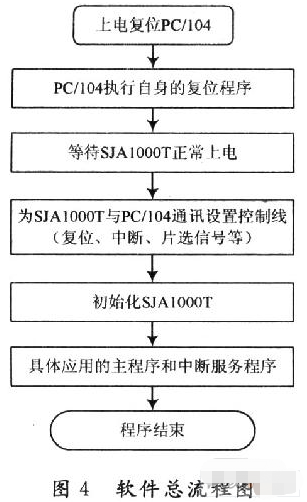

在该通讯板的设计中,控制部分的核心采用了PC/104嵌入式计算机系统。由于PC/104嵌入式计算机系统几乎具有和一般的PC机一样的强大功能,所以该通讯板的开发是在和系统模块栈接在一起后,直接在嵌入式计算机上进行的。这些工作都是采用C语言进行编程设计的。采用C语言的优点在于其快速性、高效性。在利用嵌入式计算机强大资源的条件下,C语言能满足模块的实时性要求。在系统软件的设计中,采用了结构化、模块化的设计方法,满足了仪器功能的要求。本接口系统的软件任务基本为在CAN协议芯片SJA1000T有中断发生时,根据SJA1000T的中断寄存器的内容完成相应的操作(如发送、接收数据帧等)。其流程图如图4所示。

系统设计中要进行接口驱动程序的设计,为保证操作系统的稳定和安全,驱动程序必须按一定的规范来编写。本系统的驱动程序主要考虑以下内容:设置端口和中断号,设置通讯板通讯默认参数,通讯板内存分配,映射I/O地址,创建通讯板事件和数据接收事件,初始化中断等。

SJA1000T初始化只有在复位模式下才能进行,初始化主要包括:工作方式的设置、接收滤波方式的设置、接收屏蔽寄存器和接收代码寄存器的设置、波特率设置和中断允许寄存器的设置等。SJA1000T在完成初始化后就可以回到工作状态进行正常的通讯任务了。

2.2 CAN多帧数据通信打包和解包技术

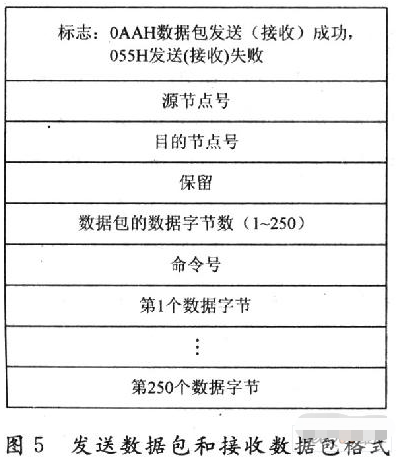

CAN通信数据传输采用短帧结构,每帧最多发送8个字节的有效数据,总线的有效传输速率很低,当在传输的数据量超过8个字节有效数据时,给用户编程带来了一定的困难。利用如图5所示的CAN的数据包格式,只需将待传输的数据进行相应的打包和解包操作即可实现数据的单帧和多帧传输,有效地简化了数据通信。

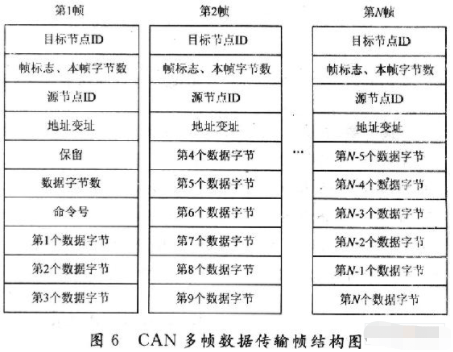

采用如图5所示的CAN数据包格式,无论是单帧还是多帧传输,只要把数据填入相应的发送缓冲区即可,在接收方,则将数据解包并放入接收缓冲区即可。与上述数据包格式相对应,当CAN总线进行多帧传输时,其CAN的多帧数据传输帧结构如图6所示。

在图6中,当发送的有效数据个数不超过4个时,一帧数据即可传输;当有效数据超过4个时,则需要多帧传输。此处的地址变址是指从发送缓冲区所取的存放于该帧的第一个有效数据的存储地址相对于缓冲区首地址的偏移量,如第一帧中地址变址为4,第二帧中的地址变址是10。地址变址的设置,使得对数据包的解包和打包实现起来较容易。

3 结 语

该通讯板设计简单,只需一块FPGA,一个CAN控制器SJA1000T和收发器PCA82C250,为增强系统的稳定性,在通信通道上均采用光电隔离技术,保护PC机避免因地环流而损坏,增强系统在恶劣环境中使用的可靠性。该通讯板采用的CAN数据包格式提高了总线的有效传输速率,经测试达到500 Kb/s,提高了通讯板通讯的实时性。本设计方案已成功应用于工业控制器中,效果理想。

责任编辑:gt

-

车载智能控制器 工程机械控制器 CAN总线控制器 硕博电子 #控制器 #can总线 #国产化替代长沙硕博电子科技股份有限公司 2024-08-29

-

PowerPC 60x总线的存储器控制器的设计与实现2009-08-26 2485

-

PCI总线目标控制器的设计2009-12-12 574

-

PCI总线从设备控制器的设计与实现2010-01-13 845

-

利用单总线控制器通讯2010-03-18 531

-

基于CAN总线的家庭控制器的设计与实现2009-11-07 956

-

基于Lonworks总线的模糊控制器实现2011-06-18 1048

-

FPGA实现CAN总线控制器源码2016-06-07 1121

-

基于MCS-51单片机和CAN总线控制器实现总线节点的设计2020-04-12 9055

-

采用CAN总线控制器SJA1000实现控制电路接口的设计2020-03-13 9119

-

浅谈PCA9564 I2C 总线控制器评估板2021-06-17 4637

-

如何使用FPGA和CAN控制器MCP2515实现惯导系统的CAN总线接口的设计2021-01-27 2124

-

如何用FPGA实现CAN总线通信控制器2022-07-29 3643

-

plc控制器为什么要带通讯口?2023-02-22 1202

-

CAN总线控制器是什么意思2024-09-03 3886

全部0条评论

快来发表一下你的评论吧 !