基于IEEE 1588时钟同步技术改善和提高系统的同步精度

描述

1 引言

以太网技术的高速发展为分布式系统在工业领域的广泛应用创造了条件。以太网具有成本低、可靠性高、传输速度快、通用性强、开放性好、发展潜力大等优点。但以太网也存在网络的确定性、实时性不强等缺陷。随着系统日益庞大复杂,分布化程度越来越高,对时钟同步的要求也逐步提高,虽然随着带宽的不断提高以及采用星形网络拓扑结构等减少冲突可能的技术的应用,以太网的确定性、实时性有一定程度的提高,但由于以太网自身冲突检测的载波帧听多路访问(CSMA/CD)机制,设备层和I/O层的数据采集与传输问题,以及TCP及UDP上的误差检测及翻译障碍等,以太网的实时性问题并未得到根本解决。仍不能满足精确定时的要求。

网络测量和控制系统的精密时钟同步协议标准IEEE1588适用于以太网、CAN总线和PROFIBUS等。IEEE 1588的基本功能是使分布式网络内所有从时钟与主时钟保持同步,该标准定义一种精确时间协议PTP(Precision rime Protocol),用于对标准以太网或其他采用多播技术的分布式总线系统中的传感器、执行器以及其他终端设备中的时钟进行微秒级同步。早期的网络时间协议(NTP)只有软件,而PTP协议同时使用硬件和软件,从而获得更精确的定时同步。PTP针对相对本地化、网络化的系统,子网或内部组件相对稳定的环境,特别适合于分布式系统在工业自动化方面的应用。

2 时钟同步原理

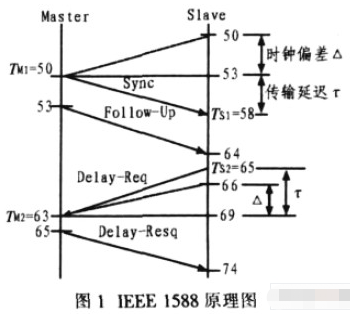

理论上,为每个系统节点配备GPS模块可得到精确的时间,这样系统中所有节点的时钟就和标准时间一致。从而达到同步;但分布式系统中节点数量大,GPS设备成本高、能耗大,且结构复杂,抗屏蔽性差,且出于安全性考虑排除大规模使用GPS的时钟同步方式。而基于以太网的IEEE 1588是通过在分布式系统各节点间交换时间报文的方法达到整个系统的时间同步。IEEE 1588通过交换报文来确定主时钟(Master)和从时钟(Slave)之间的时间偏移及报文传输的网络延迟。图1为IEEE 1588原理图。

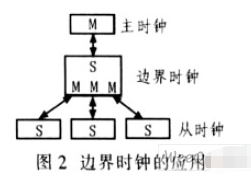

由图1可知,主时钟的节点按照定义的间隔时间(缺省是2 s)周期性地向网络上所有从时钟节点发送“同步报文”(Sync),同时主时钟节点记录同步报文实际发送的时间戳,并在随后的“跟进报文”(Follow-up)中传送该精确时间戳TM1。这样,对传递和接收的测量与标准时间戳的传播可以分开。网络上所有其他从时钟节点收到上述报文后,记录同步报文的接收时间戳TS1,TS1和TM1的偏差中不但包含主从时钟的时间偏差,还包含未知的报文传输延迟,分布式系统中每个节点在网络中所处位置、布线方式、布线长度以及目前网络技术中的固有问题,也将造成测控数据在传输过程中的不同延迟。因此需要进一步测量并消除该传输延迟。与偏移测量不同,延迟测量是不规则进行的,从时钟节点按照定义的间隔时间(缺省值是4~60 s之间的随机值)向主时钟节点发送一个“延迟请求”(Dclay Request)报文,同时记录该报文的实际发送时间,作为精确的发送时间戳TS2,而主时钟接收到该报文时也记下接收时刻的精确时间戳TM2,并将该时间戳在随后的“延迟响应”(Delay Response)报文中发送给相应的从时钟节点。假设网络延迟是对称的,则有以下两式:

根据偏差△,调整从时钟,实现对时。

3 影响同步精度的因素

(1)网络对称性从图1看出,分布式系统为计算其网络延迟和时钟偏移所进行的4次测量都是建立在报文的传输延迟(Delay)在传输方向上是相同的基础上。但这只是理想的情况,在大网络负载的情况下,Delay在传输方向上的差异会越来越大。造成同步精度的下降。但由于工业上的分布式系统多为相对本地化、局域网的系统,子网或内部组件相对稳定的环境,因此可忽略Delay在传输方向上的差异。

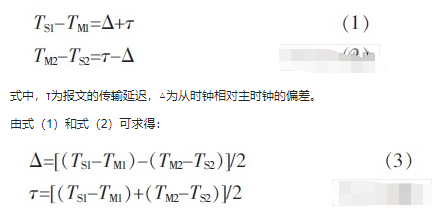

(2)网络拓扑结构系统测量时,点对点的传输能提供最高的精度,网络的拓扑结构也会对同步精度造成影响,当采用Hub连接时,网络延迟抖动为300~400 ns,当采用交换机时,由于存储-转发机制的影响,网络延迟会随着网络负载的变化而变化,因此具有较大的抖动值,使得上述网络传输延迟测量方法精度大大降低。为此,PTP采用边界时钟(Bounday Clock)的方法解决这一问题,如图2所示。在交换机内部与主时钟连接的端口可以看成从时钟端口,在接收主时钟发送的同步报文后调整自己的本地时钟,然后用调整后的时钟去同步所有与交换机主时钟连接的从时钟设备,这样带有拓扑结构的连接就变成简单的点对点连接,从而有效去除交换机所造成的延迟抖动。

(3)晶振的频率由于产生时钟的不同晶体本身的速度是不同的,而且晶体容易受温度等影响,产生晶振漂移,引起误差增大,因此需时从时钟的晶振频率进行补偿。使从时钟的晶振频率与主时钟保持一致。

4 时间戳的生成

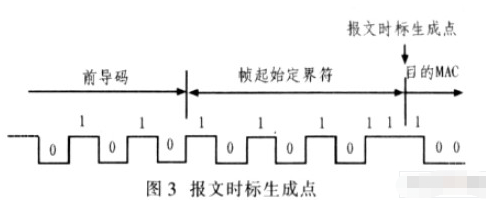

基于以上方法,可有效消除主、从时钟偏差和报文在网络中的传输延迟,从而实现分布式系统的时钟同步。同步信息检测和时间戳生成方法不同,时钟同步精度也不一样,IEEE802.3中规定以太网帧的基本结构:前导码、帧起始定界符、目的MAC、源MAC、长度、数据和帧校验序列。其中,前导码由7个‘1 0’交替的8位字节组成,用于信号同步;而帧起始定界符包含6位交替的‘1 0’及末位的2个1,末位的2个1通知接收端,跟在后面的是帧的实际字段,表示一帧开始。在以太网中,IEEE 1588所定义的各种时钟报文(Sync报文等)均以UDP/IP多播包形式发送的,报文的时标生成点位于帧起始定界符最后一位,如图3所示。

IEEE 1588的同步原理决定了时钟同步的精度主要取决于时间戳的精度。时间戳的加盖有3种方法:

(1)硬件加盖方式 时间戳主要加盖在MAC层和PHY层之间的MII(media independent interface)层,这也是最精确的加盖方式,需用硬件电路实现。

(2)软件加盖方式 时间戳加盖在网络的驱动层,在网络接口的驱动程序中实现,精度略低。

(3)加盖在应用层 因为这种方式无需修改其他系统软件,所以协议栈的操作延迟和负载都能对同步精度造成影响,因此同步精度最低。无论在网络驱动层还是在MII产生的时间戳都必须返回到PTP应用层并经由系统内核处理,然后才发送到PTP终端,由此可以看出时间戳的生成决定了PTP协议的运行。只有获得精确的时间戳才能发挥IEEE 1588所能达到的时钟同步精度。

以太网自身的CSMMCD机制、上一层通信(如TCP及UDP)上进行的误差检测及翻译障碍等,都占用以太网的时间。因此,用软件方式产生时间戳,必须优化加盖时间戳的驱动程序以提高系统内核处理带有时间戳报文的运算效率,同时优化报文发送前在网卡内部的排序,减小程序运行和网络负载对收发报文的影响,从而降低报文发送过程中的软件延迟和抖动。

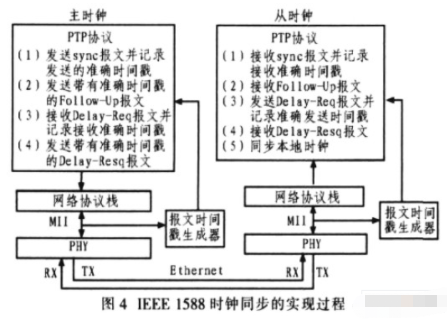

在以太网中,也可以在物理层放置硬件电路加盖时间戳,这样可以避免协议栈上部较大的时间抖动,消除报文传输中的网络延迟。由于主从时钟不同步的原因除了网络延迟外还有时钟偏差,可以采用频率可调时钟来校正从时钟相对主时钟的时钟偏差,根据从时钟处得出的自身与主时钟的偏差计算出相应的频率补偿值,从而控制时钟计数器的数值达到与主时钟的同步。硬件电路从物理层获得每个发送和接收报文的比特流,并记录时间戳信息,判断其是否为IEEE 1588相关协议报文,如果是相关报文,则把时间戳信息传送给上层软件,否则丢弃该报文的时间戳信息。对于100 M以太网,由于采用4B/SB编码和Scrambler技术,只能在物理层与数据链路层之间的MII层加盖时间戳信息。IEEE 1588时钟同步实现过程如图4所示。

5 基于FPGA的硬件同步方案

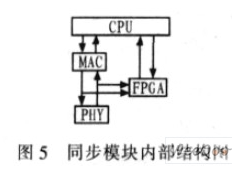

因为采用硬件电路获取时间戳,从而获得更高的同步精度,这里采用FPGA实现时间戳的获取和从时钟相对主时钟的频率纠偏。分布式系统中节点时钟同步模块的内部结构如图5所示。

每个节点包含CPU、以太网媒体访问控制器(MAC)、以太网物理层收发器(PHY)、FPGA等4种主要器件。物理层收发器和MAC控制器通过标准的MII接口相连,CPU通过总线与MAC控制器和FPGA相连。物理层收发器、MAC控制器和CPU构成通讯协议栈完成数据包的发送和接收。

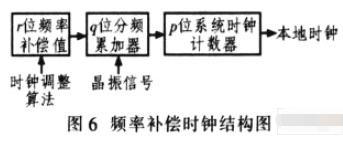

为了使从时钟的晶振频率与主时钟保持一致,FPGA中需要有一个频率可调的时钟以实现晶振纠偏,如图6所示,由r位频率补偿值寄存器、g位分频累加器、p位系统时钟计数器组成,一个普通晶体振荡信号输入FPGA模块。在每个晶振周期,r位频率补偿值寄存器内保存的频率补偿值累加到q位分频累加器中,与累加器中的值相加。

如果发生溢出,则在下一个晶振周期,时钟计数器增加一个增量,这个增量就是整个频率补偿时钟的分辨率;如果没有溢出,则在下一个晶振周期,时钟计数器保持原值。计数器的当前值即为调整后的本地时钟。因此可以通过改变频率补偿值来改变时钟计数器数值增加的频率,实现对晶振频率的补偿。q和r越大,频率补偿值的改变对累加器发生溢出的频率的影响越小,对晶振频率的补偿越精细。本系统选择r=32,q=32,p=64。

使用FPGA不但能够获得最精确的时间戳,而且能够采用数字电路的方法精确补偿从时钟的晶振频率。FPGA的控制器实现时钟调节算法,并由得到的时间戳和本地时钟相比较,得到频率补偿值,从而控制时钟计数器数值,补偿晶振的频率。而CPU则主要负责驱动MAC控制器完成相关的通讯功能。

6 结束语

采用IEEE 1588精确时钟同步协议的以太网时钟同步技术,解决了通用以太网实时性和同步性差的问题。为基于多播技术的标准以太网的实时应用提供了有效的解决方案。IEEE 1588精确时钟同步协议的制定满足网络化分布式系统的需求,利用IEEE 1588时钟同步技术可以在不增加网络负荷的情况下,实现整个分布式系统的高精度时钟同步,从而可以有效解决分布式系统的实时性问题,进而改善和提高系统的同步精度。

责任编辑:gt

-

STM32 IEEE1588时间同步2024-02-23 5523

-

浅谈网络精确时间同步—PTP(IEEE1588)2023-10-09 12817

-

如何使用IEEE1588 (PTP) 同步时间?2023-04-19 755

-

IEEE1588协议及测试技术,总结的太到位了2021-04-09 1859

-

瑞萨电子推出业界首款基于清晰源代码格式的IEEE1588同步软件2021-02-02 2362

-

IEEE 1588助力下一代测试测量系统设计2019-05-16 2351

-

IEEE1588同步原理及其在PTN网中的实现2017-11-16 1657

-

IEEE1588的原理2016-04-16 3361

-

基于TMS320DM642的硬件实现IEEE1588时钟同步2014-11-05 3039

-

IEEE1588时钟同步在PTN网中的实现2012-05-30 1440

-

分析PTN时钟同步技术及应用2011-12-16 6151

-

工业以太网的时钟同步协议对比研究2011-08-09 903

-

基于IEEE1588协议的分布式系统时钟同步方法2010-12-30 822

全部0条评论

快来发表一下你的评论吧 !