基于Windows2000操作系统和PCF1536的PCI卡的设计

描述

在视频输出、声呐仿真等实际应用中,经常要求计算机能根据要求稳定输出连续数据流。然而,当计算机工作于Windows2000操作系统下时,由于该操作系统是一个多任务的非实时操作系统,当它收到外部设备发来的中断时,需要延迟一定时间间隔后,才开始执行中断服务程序。这样,从计算机I/O口直接输出的数据流只能是间歇的数据流,无法提供连续数据流,不能满足实际应用的需要。

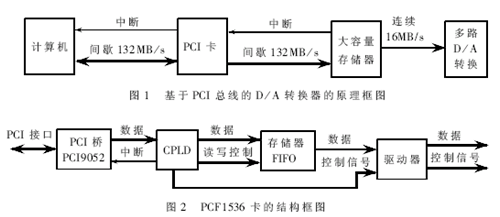

幸运的是,许多实际应用只需要低速的连续数据流。可以利用PCI总线的高速数据传输特性,在PCI接口后加入一个大容量FIFO存储器,高速的PCI数据流从FIFO存储器的输入端输入,在FIFO的输出端就能获得低速的连续数据流。这样屏蔽了Windows2000的非实时性,成功满足实际应用的需要。在图1所示的具体应用中,计算机与PCI卡之间通过PCI总线形成峰值速率达132MB/s的间歇数据流;PCI卡通过局部总线与大容量存储器之间同样是峰值速率达132MB/s的间歇数据流;最后通过多路D/A转换电路获得了速率为16MB/s的连续数据流。为了便于应用,将PCI接口模块与大容量存储器结合,设计了一块能在Windows2000下以16MB/s的速率连续输出数据的PCI卡PCF1536。

1 PCF1536的工作原理

PCI卡PCF1536是一个带有1536KB FIFO的通用PCI卡;在Windows2000操作系统下,它能以16MB/s的速度连续输出数据。图2是PCF1536的结构框图,整个PCF1536包括PCI接口、大容量FIFO存储器和驱动器三个模块。

1.1 PCI接口模块

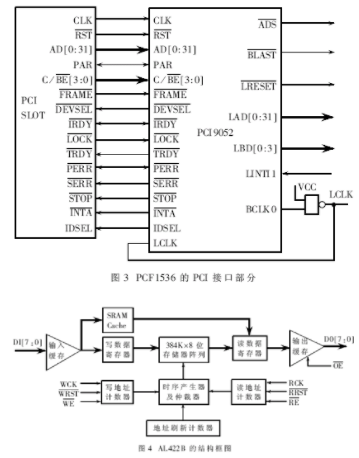

PCI接口模块由PCI9052和配置EEPROM 93LC46组成。PCI9052是PLX技术公司的产品,兼容于PCI协议(2.1版);它可作为PCI总线的从设备,支持32位数据突发传输。图3是PCI9052与PCI金手指和存储器模块的连接示意图。

PCI9052与存储器有三种连接方式:数据地址复用、数据地址非复用和ISA方式。在PCF1536中,PCI9052采用数据地址非复用方式连接FIFO存储器。其时序参见文献。PCI9052与FIFO的连接信号中,ADS表示一次突发传输的开始,BLAST表示一次突发传输的结束,LAD[0:31] 为32位数据,LBE[0:3]为字节有效信号。缓存后的时钟输出信号BCLKO经74LS00送回PCI9052,同时也送到FIFO。FIFO半满时发出的中断信号通过LINTI1进入PCI9052,再通过INTA发送给CPU。由于FIFO的写入不需要地址,因此PCI9052与FIFO之间没有地址连接。

1.2 存储器模块

1.2.1 存储器组织

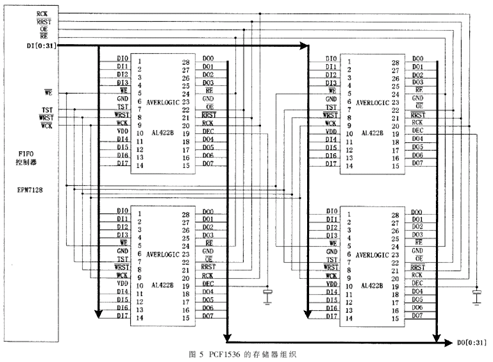

存储器模块由CPLD器件EPM7128SQC100和四片FIFO器件AL422B组成。AL422B是AVERLOGIC公司的产品,每片AL422B包含384K×8位DRAM,主要应用于视频输出。在现有的FIFO存储器中,AL422B具有最低的价格/存储位比。这是PCF1536选择使用AL422B的主要原因。AL422B的结构框图如图4所示。它能完成初始化、复位、写和读等四种操作。初始化操作发生在上电后0.1ms内,和 保持为低电平,然后可以开始正常操作。复位操作中,有效,则输入数据地址设置为0且清空输入缓存; 有效,则数据输出地址设置为0且将数据预取到输出缓存。当有效时,完成写操作,在WCK上升沿将DI7~DI0写入写数据寄存器;无效时,禁止写操作,写地址计数器保持不变。四片AL422B通过位扩展成384K×32位的FIFO存储器,如图5所示。

1.2.2 存储器控制器

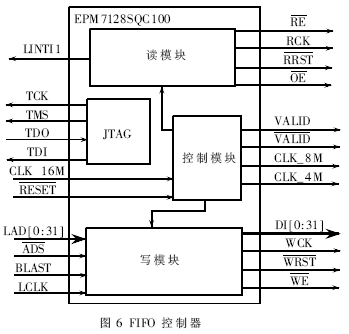

AL422B虽然有不同的数据输入和输出端口,但与通用FIFO存储器不同,它并不提供半满信号、数据有效信号等。因此AL422B不是完全意义上的FIFO存储器。在PCF1536上,使用一片可编程逻辑设备EPM7128作为FIFO控制器,全面控制AL422B的功能。从图2和图5可以看出,EPM7128为FIFO提供RCK、、、DI[0:31]、、、TST、和WCK等读写控制信号;当FIFO半满时提供半满信号HF;另外EPM7128为外设提供正负数据有效信号、4MHz和8MHz的时钟信号等,供外设灵活使用。图6是用VHDL语言对EPM7128编程而成的FIFO控制器。该控制器由JTAG模块、写模块、读模块和控制模块组成。计算机通过JTAG接口对EPM7128现场编程。当PCI9052的数据准备好后,写模块按LCLK时钟将数据读入,接着按WCK时钟将数据写入AL422B。在FIFO控制器的控制下,整个384K×32位的FIFO存储器被分为A、B两部分。当数据从A部分读出时,PCI9052将数据写入B部分;反之,当数据从B部分读出时,PCI9052将数据写入A部分。数据读出的速率为16MB/s。当A(或B )部分数据读完后,FIFO控制器接着从B(或A)部分读数,并通过中断通知CPU向A(或B)部分写入数据。如此循环往复。

1.2.3 最大允许中断延迟

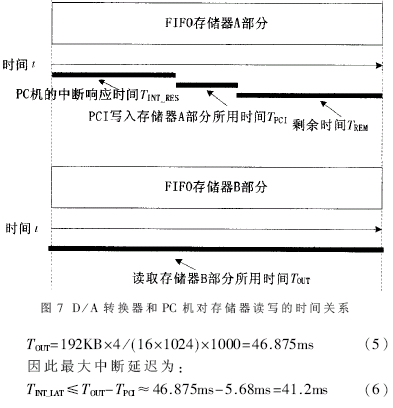

要保证PCF1536输出连续数据,就必须保证FIFO不会被读空。FIFO输出数据的同时,PC机必须及时补充数据。从上可知,整个FIFO存储器被分成A、B两部分,每部分容量均为192K×32位。下面分析当数据从存储器B部分读取、向存储器A部分写入时,读写FIFO存储器的时间关系,如图7所示。

假定PC机的中断延迟时间为TINT_LAT,PC机写满存储器A部分所用时间为TPCI,剩余时间为TREM;读完存储器B部分所用时间为TOUT。如PCF1536输出连续数据流,剩余时间TREM必须大于等于0。

TREM = TOUT-TINT_LAT-TPCI≥0 (1)

根据公式(1),有: TOUT-TINT_LAT-TPCI≥0 (2) TINT_LAT≤TOUT-TPCI (3)

PC机写满存储器A部分所用时间: TPCI=192KB×4/(132×1024)×1000≈5.68ms (4)

读完存储器B部分所用时间:

通过以上计算,在Windows2000操作系统的最大中断延迟不大于41.2ms的情况下,PCF1536能以16MB/s的传输率连续输出数据。

中断延迟决定了硬件产生的中断并得到PC机正确响应的最高频率。实际上,根据各种资料分析,虽然Windows2000操作系统的中断延迟会随着应用条件不同而差异很大;但可以肯定的是,其中断延迟远远小于41.2ms。

1.3 驱动器模块

驱动器模块由七个74LS245构成。每个74LS245能为8位数据(信号)提供驱动,其中四个74LS245用作32位数据线的驱动器,另外三个用作控制信号的驱动。每个74LS245的输出分别连接到16脚的插座。16脚插座中的8个脚接信号线,另外8个脚接地线,以提高输出信号的抗干扰能力。采用这种输出方式,PCF1536与外设之间可以用4m的排线连接而不会受明显干扰。

2 测试过程及测试结果

图8是PCF1536卡的测试系统。计算机重复发送如下数据:0x20002000、0x32CF32CF、0x3E6F3E6F、0x3E6F3E6F、0x32CF32CF、0x20002000、0x0D300D30、0x01900190、0x019-00190、0x0D300D30。以上10个数据实际上是对一个正弦波的10个均匀采样值。用示波器监视D/A转换器的输出。

在示波器上可以观测到:36路的D/A输出都是稳定的20kHz正弦波。该测试系统经过连续48小时运行,没有出现计算机死机和停止发送数据的现象。因此,结论显而易见:在Windows 2000操作系统下,PCF1536能以16MB/s的速度连续输出数据,它满足某些系统对连续数据流的要求。利用该测试系统,虽然不能准确测出Windows2000的中断延迟到底有多大,但可以肯定:Windows2000的中断延迟远远小于41.2ms。

责任编辑:gt

-

求一种Windows2000下连续输出数据的PCI卡2021-05-28 1264

-

求助:请问WINDOWS2000系统能装哪个版本的labview2017-03-27 2530

-

求Windows2000系统风格的Bool控件2016-09-24 2869

-

Windows2000下的Popup发送功能_Delphi教程2016-03-16 620

-

Windows2000/98下USB驱动程序的开发2011-11-17 1854

-

安全配置Windows2000服务器2010-02-01 590

-

WINDOWS操作系统有哪些?2009-12-26 7711

-

Windows2000/XP下进行端口操作的通用模块的实现2009-09-04 531

-

PCI串口通信卡WDM驱动程序设计与实现2009-09-01 709

-

Windows2000/XP下端口访问器的编写2009-03-25 871

-

Windows 2000中文操作系统培圳教程2009-03-11 574

-

中文Windows 2000操作系统2009-03-10 2314

-

Windows XP操作系统 ppt课件2008-11-07 1620

-

一种Windows2000下连续输出数据的PCI卡2006-03-24 1300

全部0条评论

快来发表一下你的评论吧 !