基于XC2VP20—FF896CGB0345 FPGA实现IPV6数据包的拆装

描述

作者:王志远,杜诗武,曲晶

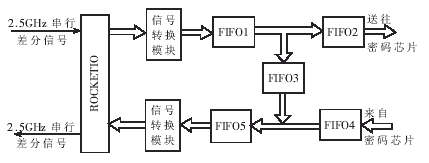

在参与国家“863”重大专题项目“高速密码芯片及验证平台系统”的过程中,遇到了将IPV6数据包的包头和数据部分拆开,然后把数据部分送密码芯片进行加/解密处理,最后再将处理后的数据部分与包头重新封装为数据包的课题。以往对IP包进行拆装多利用软件实现,但本项目涉及到配合高速密码芯片(处理速度在2Gbit/s以上)工作的问题,显然利用软件实现IP包的拆装在速度上达不到要求。为此,运用FPGA(型号为Xilinx公司的XC2VP20—FF896CGB0345)来实现IPV6数据包的拆装。该FPGA内部逻辑框图如图1所示。

图1 FPGA内部逻辑框图

其工作流程为:2.5GHz的标准IPV6数据包串行差分信号通过ROCKETIO高速通道后转换为16位125MHz并行信号,再经信号转换模块进一步转换为66位62.5MHz并行信号后进入FIFO1缓存,然后对其输出数据进行判断,若是报头则送入FIFO3缓存,若是数据部分则送入FI

FO2缓存,最后将FIFO2数据送往密码芯片进行处理;经密码芯片处理的数据首先放入FIFO4进行缓存,然后控制FIFO3和FIFO4将一个数据包的头和数据写入FIFO5中,重新封装成一个完整的数据包;重新封装的IPV6数据包经过信号转换模块变为16位125MHz的并行信号,并通过ROCKETIO高速通道转换为2.5GHz高速串行差分信号送出。

可以看出,经过以上流程,实现了一个数据包的拆分和重新封装。

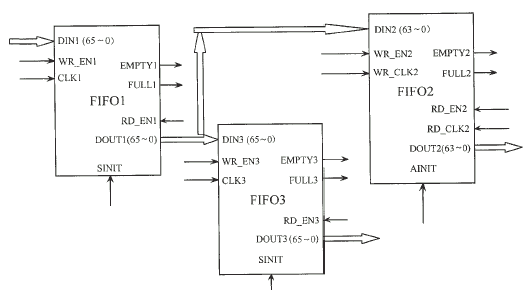

1 IPV6数据包的拆分

用FPGA实现IPV6数据包的拆分,主要是通过控制几个FIFO的数据输入输出来实现的。FPGA内部的拆分单元电路的物理连接如图2所示,其中FIFO1的作用是缓存IPV6数据包,FIFO2的作用是缓存IPV6数据包的数据部分,FIFO3的作用是缓存IPV6数据包的包头。

图2 拆分单元电路物理连接图

图中的三个FIFO都是由Xilinx公司的开发工具ISE6.1自带的Core IP生成的。其中FIFO1和FIFO3是同步FIFO,工作时钟为频率62.5MHz,输入输出数据宽度都是66bit;FIFO2是异步FIFO,输入时钟频率为62.5MHz,输出时钟频率为50MHz(密码芯片的工作时钟频率为50MHz),输入输出数据宽度都是64bit。

FIFO1的输入数据为IPV6数据包,格式如表1所示。可以看出,该数据是以并行的66bit信号传输的,即每一时钟周期并行传送66bit数据。其中每个周期的高两位(即65位和64位)为数据包的头尾标志,这是IPV6路由器内部根据实际处理需要加上的,“10”表示一个完整数据包的第一周期,“11”表示数据包的中间内容,“01”表示一个完整数据包的最后一个周期。因为IPV6数据包的包头是固定长度的,为40字节(等于5×64 bit),故数据的前五个周期为IPV6数据包的包头,包头后面跟的就是数据包的数据部分。

下面讨论IPV6数据包的包头和数据部分的拆分过程。

首先判断FIFO1输入端数据的头尾标志DATA(65~64)与FIFO1的满标志FULL1,如果DATA(65~64)=“10”且FULL1=“0”,即判断到一个完整数据包的开始且FIFO1未满,则使FIFO1的写使能WR_EN1有效,写入数据;如果DATA(65~64)=“01”,即判断到一个完整数据包结束时,则使WR_EN1无效,这样一个完整的数据包就缓存到了FIFO1中。

当判断到FIFO1的空标志EMPTY1=“0”,即FIFO1非空时,令FIFO1的读使能信号RD_EN1有效,将FIFO1中的数据读出,直到EMPTY1=“1”,即FIFO1空为止。对读出的数据设定一计数器COUNTER1进行计数,当DOUT1不为0即FIFO1输出端有信号时开始计数。当05时,令WR_EN3无效,WR_EN2有效,将IPV6数据包的数据部分送FIFO2缓存,准备送密码芯片处理,直到头尾标志DOUT1(65~64)=“01”时,将COUNTER1清零,在判断到COUNTER1为0后,将WR_EN2置为无效。注意:FIFO1的输出端口是66位的,FIFO2的输入端口是64位的,故在FIFO1向FIFO2写数据的过程中,应将FIFO1的输出端口信号DOUT1(63~0)传送给FIFO2的输入端口DIN2(63~0)。当判断到FIFO2非空时,将其读使能信号RD_EN2置为有效,即可向密码芯片送出数据。

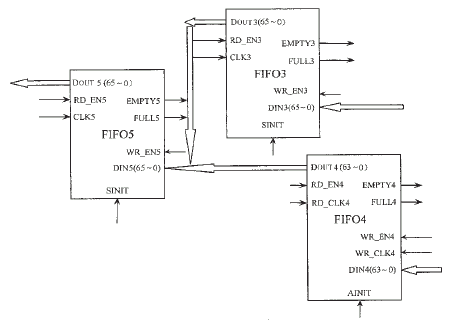

2 IPV6数据包的重新封装

用FPGA实现IPV6数据包的重新封装,同样是通过控制几个FIFO的数据输入输出来实现的,FPGA内部的重新封装单元电路的物理连接如图3所示,其中FIFO4的作用是缓存密码芯片送出的加解密处理后的数据;FIFO5的作用是缓存重新封装后的IPV6数据包;FI FO3与拆分单元共用,作用是缓存IPV6数据包包头。

图3 重新封装单元电路物理连接图

图4 密码芯片输出指令格式

图中的FIFO4和FIFO5也都是由Xilinx公司的开发工具ISE6.1自带的Core IP生成的,其中FIFO4是异步FIFO,输入时钟为50MHz,输出时钟为62.5MHz,输入输出数据宽度都是66bit;FIFO5是同步FIFO,工作时钟为62.5MHz,输入输出数据宽度都是66bit。

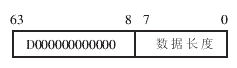

密码芯片对数据进行加/解密处理完毕之后,在送出处理数据前,首先向外部系统发送一64bit长的接收指令,指明处理数据所用的加解密算法和数据长度。例如,在对数据进行3DES加密处理的情况下,接收指令格式(16进制)如图4所示,其中高56位为指令编码,低8位为将要输出的处理数据的长度。

因此,在接收处理数据时,首先判断是否有接收指令,如果有接收指令,则将接收指令中的数据长度放入寄存器中进行寄存,并设定计数器COUNTER2开始计数。当0这时,包头已经缓存到FIFO3中了,处理后的数据已经按格式要求缓存到FIFO4中了,最后要做的就是控制FIFO3和FIFO4,把一个完整的IPV6数据包写入FIFO5中。具体做法是:设定计数器COUNTER3,当FIFO3和FIFO4都非空时,COUNTER3开始计数。当COUNTER3>0时,将FIFO5的写使能信号WR_EN5置为有效;当COUNTER3=0时,WR_EN5置为无效。当0=6时,令RD_EN3无效,RD_EN4有效,将FIFO4的输出数据DOUT4(65~0)写入FIFO5的输入端DIN5(65~0),直到DOUT4(65~64)=“01”时,将COUNTER3清零,RD_EN4置为无效。这样,一个完整的IPV6数据包就重新封装在FIFO5中了,当判断到FIFO5非空时,就可以令RD_EN5有效,向外输出处理后的完整的IPV6数据包了。

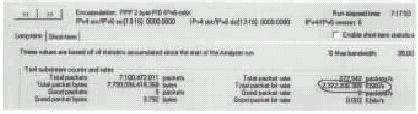

从上述讨论可以看出,本课题在FPGA中采用了五个FIFO,并设定了三个计数器控制这五个FIFO的输入输出来实现对IPV6数据包的拆分和重新封装。总的来看,整个FPGA设计思路巧妙,电路结构简单,达到了预期的处理速度。图5是整个测试系统在对1024字节的IPV6数据包进行拆包、送密码芯片加密、重新封装处理后测试仪控制软件界面上显示的收包数据统计。从该图可以看出,整个系统对IPV6数据包的处理速度达到了2.372Gbit/s,而这样的处理速度用软件是不可能达到的。

图5 测试仪收包数据统计

责任编辑:gt

- 相关推荐

- 热点推荐

- 芯片

-

IPv6地址是什么,IPv6的意思2011-01-25 4904

-

基于IPv6的无线传感器网络边界路由器有什么优点?2020-04-21 2508

-

怎样利用FPGA来实现IPV6数据包的拆装?2021-04-28 1473

-

基于FPGA的IPV6数据包的拆装是如何实现的?2021-05-28 1938

-

IPv6不能外发数据包如何解决呢2022-09-05 3238

-

一种IPv6数据包安全传输的实现2009-07-30 809

-

基于IPv6的防火墙的关键技术与实现2009-08-19 699

-

基于FPGA的IPV6数据包的拆装2010-06-25 640

-

移动IPV6在改进数据包发送路径模型下性能分析2012-01-12 544

-

IPv6中的网络隐蔽通道技术研究2012-02-23 863

-

基于FPGA的IPV6数字包的分离与封装的实现2012-05-21 2627

-

如何用隧道搭建ipv62017-12-26 29952

-

通过运用FPGA器件实现IPV6数据包的拆分和重新封装2019-05-13 3197

-

如何使用FPGA实现一种2Gbps的多数据包透明传输机制2021-04-02 956

-

什么是IPv6隧道技术2024-10-30 2040

全部0条评论

快来发表一下你的评论吧 !