沁恒微电子 RISC-V系列MCU+亮相首届RISC-V中国峰会

控制/MCU

描述

首届RISC-V中国峰会主会于2021年6月22日盛大开幕,作为国内迄今为止规模最大的以RISC-V为主题的峰会,吸引了100多家厂家参会。峰会覆盖产业界最新技术介绍及产品发布、学术界前沿成果交流。沁恒微电子作为RISC-V国际基金会战略会员受邀参会。

沁恒微电子自成立后,从自研8位RISC内核、自研E8051到引入ARM等内核的MCU,已有十多年的MCU发展历程。

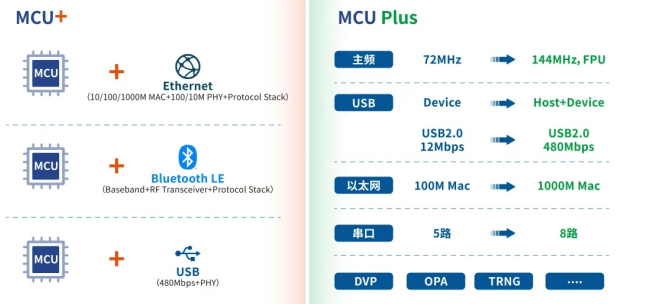

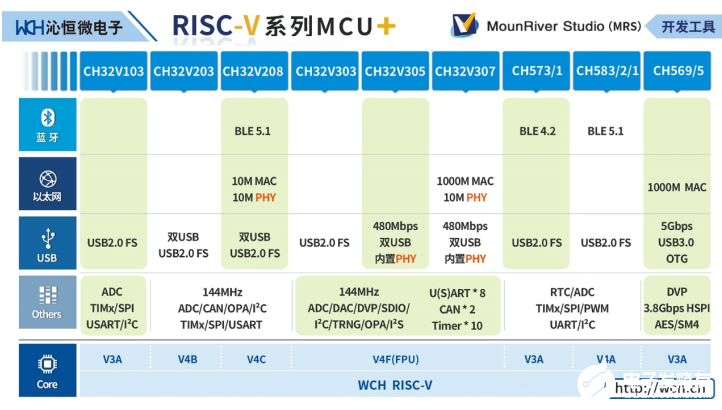

近年来,结合USB3.0、低功耗蓝牙、千兆以太网等接口的设计经验,深入研究RISC-V指令集,在压缩指令集、硬件压栈、快速中断等实际应用方向上进行优化,研发多款RISC-V内核IP,并基于32位通用MCU架构外加USB高速PHY、蓝牙收发器、以太网PHY等专业接口模块推出增强版MCU+,进一步拓展了RISC-V在低功耗、无线通讯、高速率传输等多种嵌入式环境下的应用。

何为沁恒MCU+?

峰会期间沁恒技术总监杨勇发表了“面向嵌入式MCU的RISC-V研究与成果”的主题报告。

报告介绍了沁恒微电子以应用为驱动,结合USB、蓝牙、以太网等特色接口,在面向嵌入式MCU的RISC-V所做的研究及成果:

- 针对将ARM平台上多年自研成熟的低功耗蓝牙和以太网协议栈移植至RISC-V平台,编译后占用代码空间变大的问题,自定义可支持半字和字节的16位压缩指令c.lbu、c.lhu、c.sb、c.sh,使得占用空间缩减6%;

- 针对PLIC中断控制器不能满足USB3.0、千兆以太网、SerDes等高速接口的实时性要求,研发了快速中断控制器和硬件压栈模式,并创新性的设计了VTF(Vector Table Free)中断跳转方式,中断响应速度较软件压栈提升6.8倍以上;

- 针对低功耗应用场景,率先引入WFE睡眠模式,并增加了如idle、halt、sleep、shutdown等多种睡眠等级;

- 针对JTAG调试占用I/O资源、速度慢等问题,自定义两线调试接口,速度大幅提高。

上述优化所配合使用的集成开发环境(IDE)为MounRiver Studio(MRS),由MounRiver团队开发,GCC工具链编译,可免费使用。支持RISC-V/ARM双核开发,支持跨内核芯片工程迁移。(www.mounriver.com)

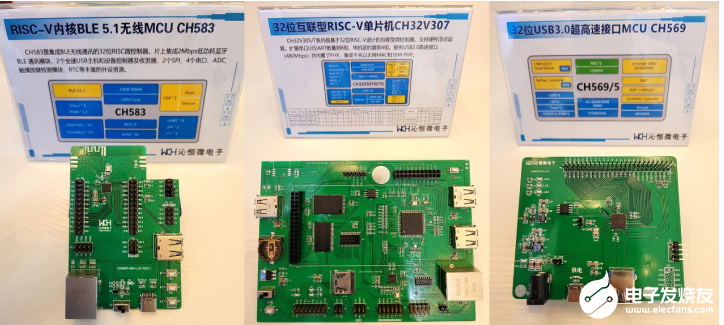

峰会主会为期三天,并设置专门的厂商展区,沁恒微电子携自研“一核三接口”的RISC-V系列MCU+参展,备受瞩目。

(部分展品如图)

沁恒微电子研究MCU内核多年,以应用驱动、将内核外设深度结合形成多款芯片,应用于计算机和手机周边、联网工控设备等。同时针对各种应用持续优化改进,助力RISC-V在国内更好的扎根落地,并在应用中发展壮大。

-

沁恒微电子:从互连互通应用推动RISC-V落地发展2025-06-26 1354

-

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地2024-08-30 1635

-

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!2024-08-26 1423

-

Andes晶心科技将亮相RISC-V中国峰会2023-08-22 1079

-

2023 RISC-V中国峰会:RISC-V深圳技术分享会(同期会议)2023-08-15 1729

-

教你玩转32位RISC-V内核CH32V系列MCU(附样例)2022-08-15 3631

-

4款玄铁RISC-V芯片亮相2022-03-08 2827

-

RISC-V的相关资料分享2021-12-09 2425

-

沁恒(WCH)和RT-Thread达成合作,共建RISC-V应用生态2021-09-18 3573

-

[WCH RISC-V系列MCU+]32位互联型RISC-V单片机CH32V3072021-06-30 5206

-

首届RISC-V中国峰会正式开幕,RISC-V中国峰会直播地址分享2021-06-22 3347

-

沁恒微电子受邀参加首届RISC-V中***会2021-06-17 5518

全部0条评论

快来发表一下你的评论吧 !