国产AGM FPGA设计流程的详细介绍

国产AGM FPGA设计流程的详细介绍

描述

AGM Micro是领先的可编程SoC、通用32位MCU、和异构(MCU)边缘计算芯片和方案提供商,致力于为消费电子、工业和AIoT中高量市场提供智能化的设计软件和芯片系统。AGM针对不同的纵向应用市场,并拥有19个知识产权,以及获得专利的编译软件(包括数据库、综合、布局、布线、时序分析、比特流产生等)及电路。公司的所有芯片产品线均达到接近ASIC的低成本,并兼具灵活性。

以下是AGM FPGA的一份快速入门介绍,限于篇幅,如有不详尽的地方,欢迎留意或者邮件沟通交流。

3. 设计流程

从新建工程一步一步操作,直到生成编程文件,烧录到目标器件上。此部分将Supra和Quartus II一起配合使用。

3.1 在Supra中新建工程

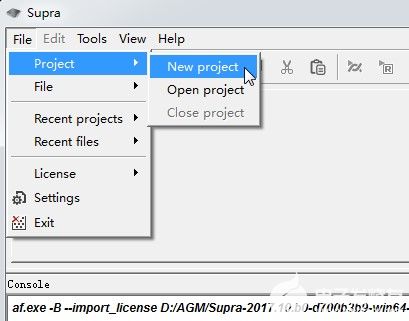

打开 Supra,新建工程(File->Project->New Project),设置工程目录和工程名称。具体步骤如下:

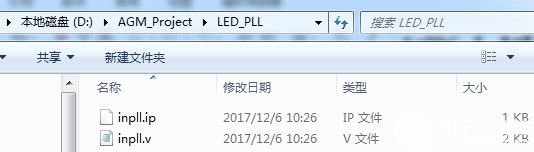

1、 准备工作:在电脑上先建立一个保存AGM项目工程文件的文件夹。比如在D盘,建立一个AGM_Project\LED_PLL的文件夹。并将使用内置晶振的inpll.v和inpll.ip这2个文件放在该文件夹的目录下。(若不需要使用内置的时钟及PLL,则导入inpll.v和inpll.ip的步骤可以忽略)。

2、 打开Supra软件新建工程;

图 3.1 在Supra中新建工程

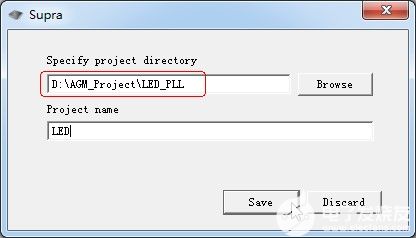

3、 选择保持路径及输入工程名称;

保存的目录选择D:\AGM_Project\LED_PLL,Project name的框内输入工程名称:LED。然后点击Save保存工程。

图 3.2 选择保存位置及输入工程名称

点击Save后,弹出的对话框点OK。

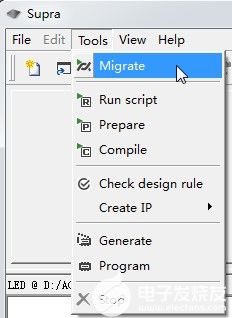

4、 工程转换(Migrate);

选择菜单: ”Tools -> Migrate” ,或者点击Migrate按钮。

图 3.3 菜单选择

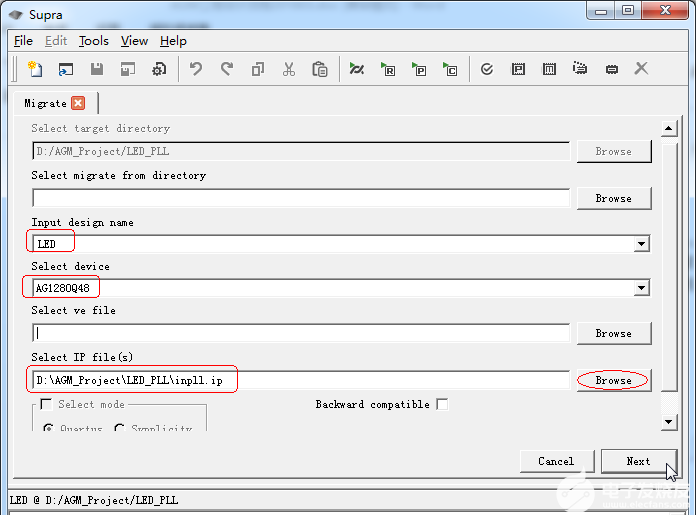

Target Directory:是默认选择当前的工程目录,无法修改;

Select migrate from directory:不填;

Input design name:输入设计名称(例如这里填入:LED);

Select device:从下拉菜单中选择AG1280Q48;

Select ve file:不填;

Select IP file(s) :点击Browse,在LED_PLL工程目录下导入事先保存的inpll.ip;

(注意:1、因为该例程使用了芯片内部集成的晶振,所以需要导入此inpll.ip。若是不需要使用晶振,则不需要导入inpll.ip。

2、现在设的这个PLL的模块inpll.ip,test1输出大约37M,test2输出62MHz,芯片不同略有不同;)

将上述信息设置完成后,如图 3.4所示,点击Next。

图 3.4 Migrate 窗口设置

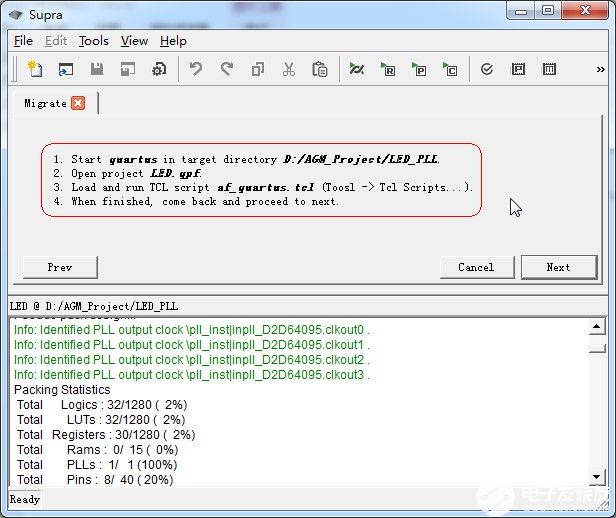

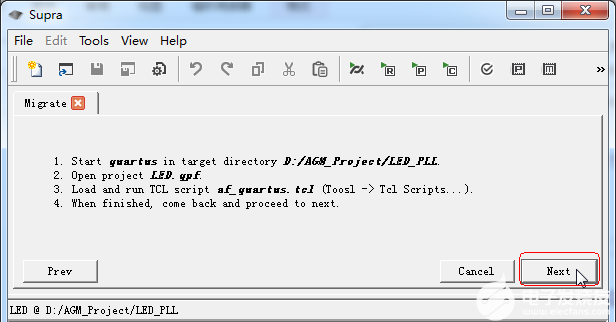

5、点击 Next后,出现如图 3.5所示的画面。软件会生成一个以 LED 命名的Quartus II格式的Project文件,。下一步操作切换到Quartus II软件中继续进行。

图 3.5 Migrate设置完成

3.2 在Quartus II中进行HDL设计

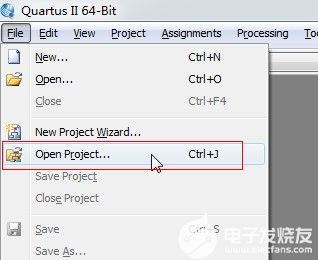

打开Quartus II, 然后选择Open Project…,打开上一步在Supra中建立的LED Project。

图 3.6 Quartus II中打开Supra建的工程

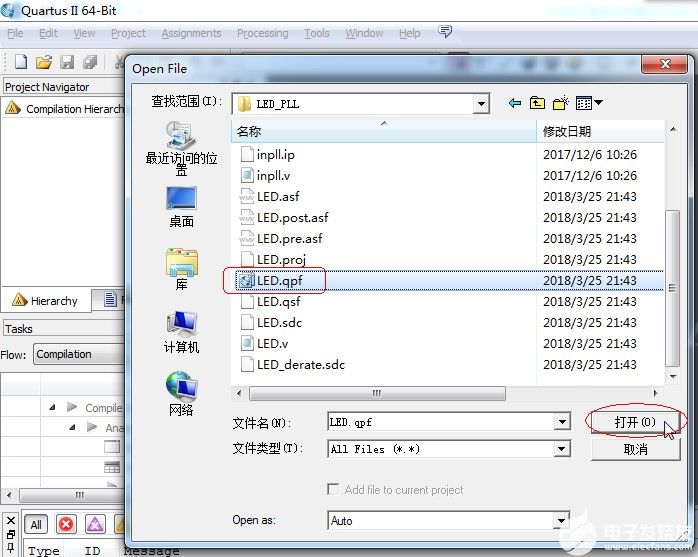

图 3.7 在Quartus II打开LED.qpf文件

LED的工程已经建立好,在Quartus II中,对应选择的器件是EP2C70F896C8,这个不用关注,只需要在Quartus II中编写HDL代码,综合等。

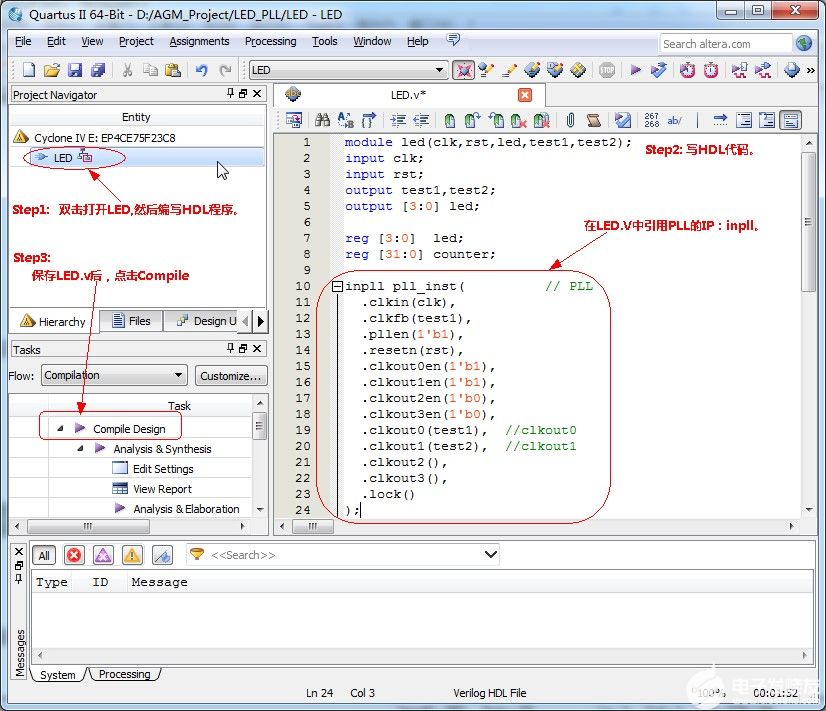

图 3.8 在Quartus II中编写HDL代码

HDL程序编写完成点保存,然后选择菜单栏的Processing-àStart Compilation。编译如果提示有错误,就对代码进行修改,直到没有Error提示为止。

图 3.9 HDL程序编译

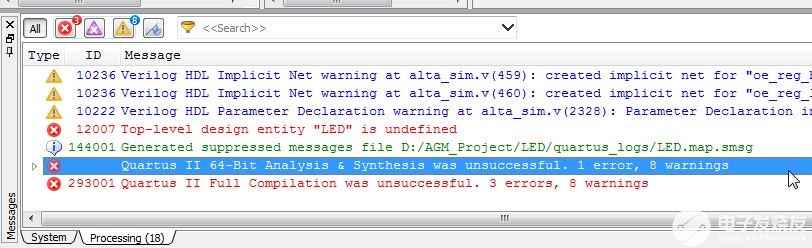

编译若有错误,可以根据下面的报错提示,如”LED” is undfined( LED未声明),故需要修改HDL代码。

图 3.10 Qurtus II 错误报告

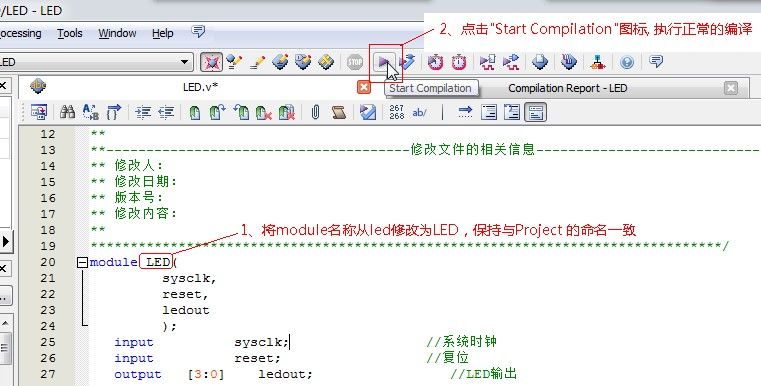

在LED.v的程序代码中,将module名称从led修改为LED,然后点击保存。以后修改原设计,在Quartus II里只需执行正常的编译(Start Compilation)。

图 3.11 修改程序后,重新编译

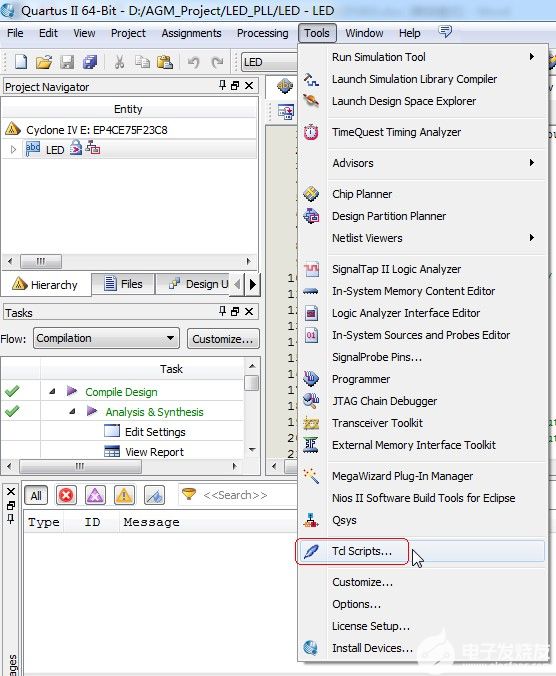

重新再编译,等编译通过后, 在Quartus II 中选择菜单中 Tools -> Tcl Scripts...。

注意:Tcl Scripts...只需要在第一次新建工程的时候需要执行,后续修改HDL代码,Compile通过后,不需要再执行Tcl Scripts...。

图 3.12 Tcl 操作

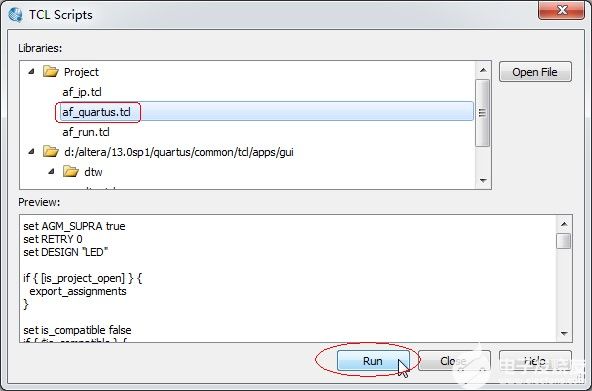

在Tcl Scripts窗口中选 af_quartus.tcl,点击 Run。

图 3.13点击 Run进行编译

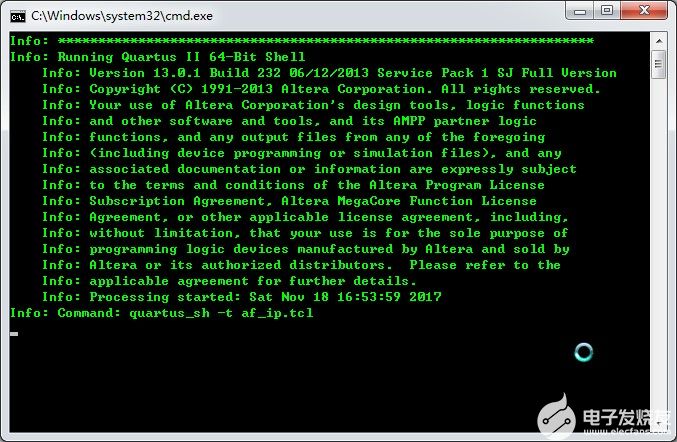

中间会弹出命令窗口,不用理会,后台会自动处理。

图 3.14 临时弹出命令窗口

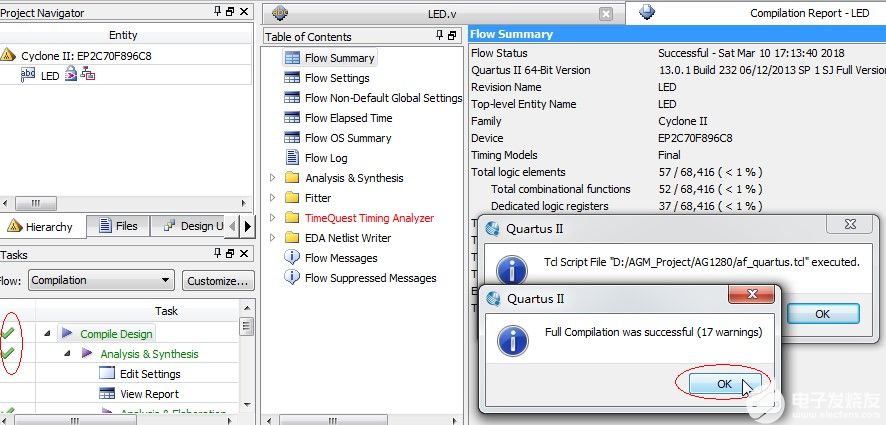

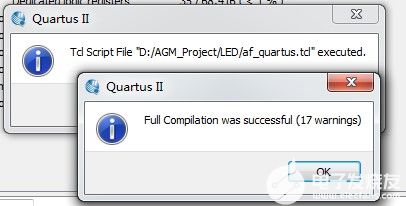

图 3.15 执行TCL操作完成后提示通过OK

如下图,点击OK。

图 3.16 编译成功

3.4 功能引脚分配

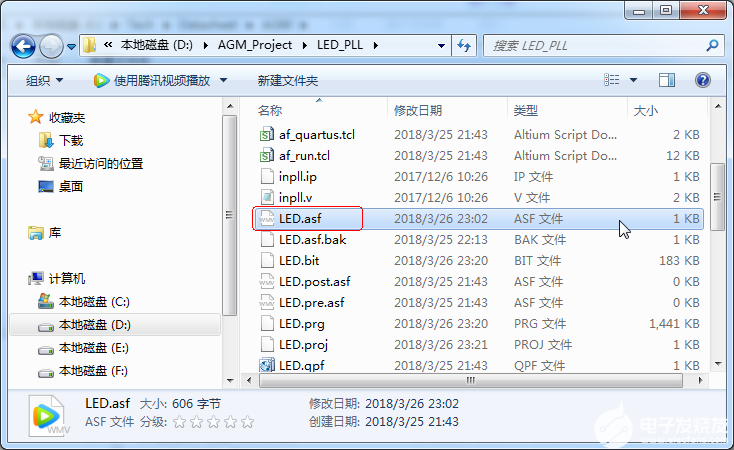

Quartus II 里编译成功后,在工程目录D:\AGM_Project\LED_PLL中,找到LED.asf 文件。

图 3.17 打开工程目录下的管脚配置文件LED.asf

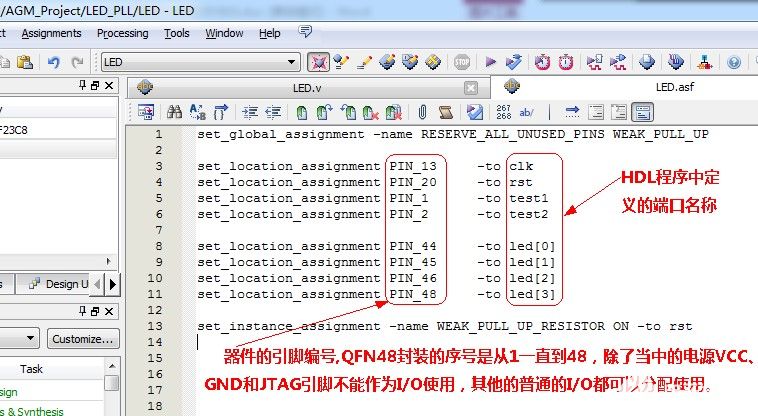

该LED.asf文件可以通过记事本打开,也可以直接拖动到Quartus II中打开。LED.asf文件初始状态是一个空文档,打开后是一片空白,用户可以直接编辑管脚分配说明,(具体请参考芯片的管脚映射列表,确定 IO 名称及位置),注意:PLL 的输入时钟必须是芯片的全局输入时钟管脚(AG1280Q48的是Pin_13,Pin_15,Pin_19 这三个)。LED.asf的管脚指定描述如下。LED.asf文件内容如图 3.18所示,编辑完成后,点击保存即可。

set_global_assignment -name RESERVE_ALL_UNUSED_PINS WEAK_PULL_UP

set_location_assignment PIN_13 -to clk

set_location_assignment PIN_20 -to rst

set_location_assignment PIN_1 -to test1

set_location_assignment PIN_2 -to test2

set_location_assignment PIN_44 -to led[0]

set_location_assignment PIN_45 -to led[1]

set_location_assignment PIN_46 -to led[2]

set_location_assignment PIN_48 -to led[3]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rst

注意:1、器件的引脚序号,QFN48封装的序号是从1一直到48,除了当中的电源VCC、GND和JTAG引脚不能作为使用,其他的普通的I/O都可以分配使用。

2、CLK信号必须要通过名称为IO Global的全局引脚接入,否则可能导致无法分配引脚。

3、Reset信号也建议从IO Global的全局引脚接入。

图 3.18 编写管脚配置文件

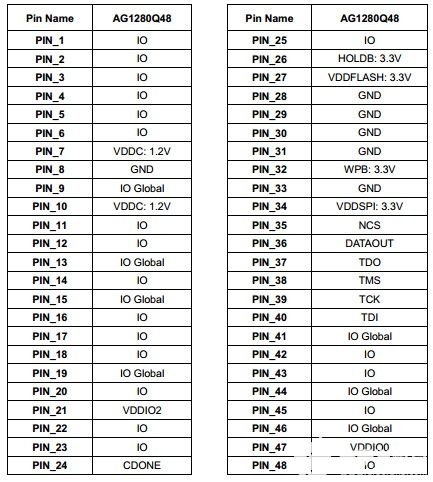

补充,AG1280Q48的引脚定义如下:

图 3.19 AG1280Q48 PINOUT

3.5 在Supra中进行项目编译

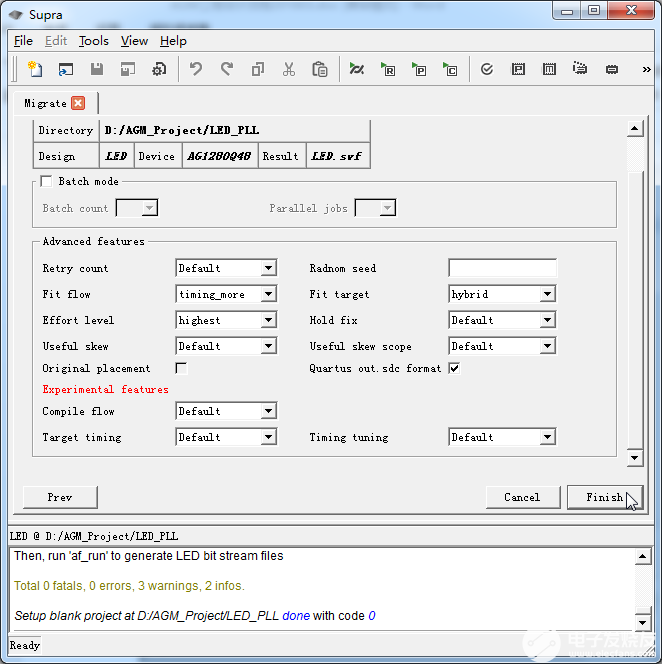

返回Supra 中,点击Next,开始进行编译,参数按照默认的。如图3.20和图3.21所示。

图3.20 点击Next

图3.21 保持默认参数

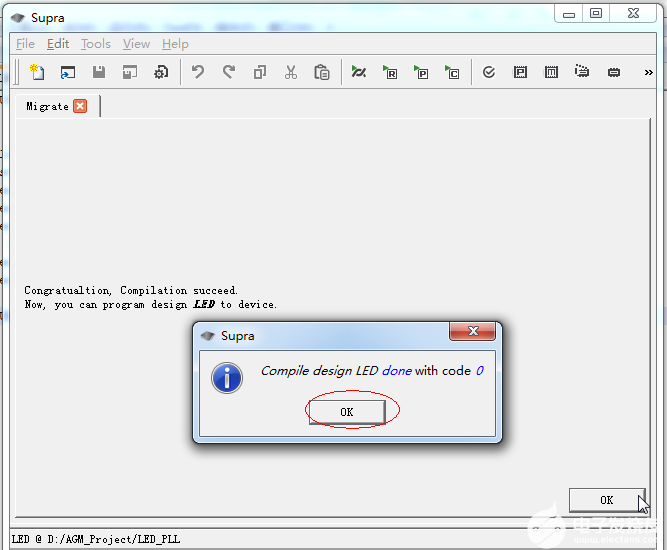

参数保持默认的,然后点击Finish,软件后台将进行布局布线等操作。等待软件提示成功,如图3.22所示。

图3.22 设计编译成功

编译成功后,软件将自动生成烧写文件,LED_hybrid.prg。

3.6 芯片烧写

在Supra 软件菜单栏中选Tools ---à Program,或者点击Program图标。选中 DesignName_hybrid.prg,这里我们选择LED_hybrid.prg,然后点击Program开始程序烧写。烧写成功后,CDONE 管脚会变高。

审核编辑:符乾江

-

AGM Micro推出STM32兼容MCU产品系列2023-12-29 1582

-

FPGA的详细开发流程2023-07-04 7106

-

国产FPGA, 兼容替代ALTERA, XILINX资料详解2022-01-30 15143

-

AGM FPGA 快速入门手册2021-07-26 7029

-

AGM FPGA快速入门2021-06-01 5356

-

学习 AGM 与FPGA快速入门2020-09-03 2838

-

国产FPGA傲格芯AGM,分享大家的AGM FPGA的技术资料2020-09-01 8248

-

FPGA教程之ISE设计流程简介的详细资料说明2019-04-04 2146

-

FPGA视频教程之NIOS II开发流程的详细资料说明2019-03-22 1857

-

FPGA视频教程之FPGA开发流程的详细资料概述2019-03-01 1906

-

国产FPGA,最新资料,推出的最新产品会及时更新,希望大家关注下,支持国产!2019-01-01 9746

-

FPGA的设计流程是怎么样的?FPGA设计流程指南详细资料免费下载2018-10-17 1840

-

国产FPGA开发经验分享之初识AGM2018-10-12 8942

-

AGM国产高端FPGA系列产品线发布,国产FPGA芯片市场再进一步2018-07-12 12695

全部0条评论

快来发表一下你的评论吧 !