串行解串器的关键技术及应用分析

描述

作者:Michael Peffers,TI公司

本文我们将探讨串行解串器 (SerDes) 以及各种技术及其应用。

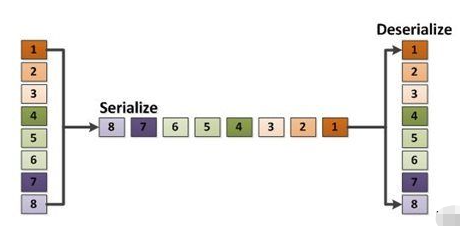

串行解串器是可将大位宽并行总线压缩成少量(通常为一条)差分串行链路的器件,该链路可在远远高于低速大位宽并行总线的速率下进行切换。串行解串器对大位宽并行总线进行了串行化,不仅可实现在系统内部、系统间或位于两个不同地点的系统间进行大量数据的点对点传输,同时还可降低功耗、板级空间和成本。下图 1 是串行解串器的基本概念。

图 1:串行∕解串

随着数据速率的增加,有关实施并行总线的问题也随之增多。较快总线比较慢总线功耗高,而且由于定时容差的降低,信道数量的增加,布局难度也越来越大。随着数据速率的增加,保持信道间的时滞也日益重要,原因是较大的时滞差异会导致系统定时问题,因为接收器需要按对齐位组在并行数据总线中进行时钟计时。此外,由于如今的设计日益紧凑,板级空间也格外珍贵,因此大型并行总线会消耗宝贵的 PCB 基板空间。串行解串器能够降低成本、功耗以及板级空间,可为上述设计挑战提供良好的解决方案。

我们首先用一个简单的串行解串器实例来描述基本工作原理,因为当前有些串行解串器器件可能比较难处理。时钟定时对于使用串行解串器的应用来说极为重要,因为一切都不能随机出现,必须在给定的时间内发生。系统时钟可分配给包括串行解串器在内的所有组件,以帮助实现同步工作。网络处理单元 (NPU) 或 FPGA 等终端器件不仅可在所需的系统频率下实现并行数据输出运行,而且还可连接至串行解串器器件的并行接口。并行数据可在系统时钟的时钟上升沿、下降沿或上升及下降沿上、在串行解串器 FIFO 中进行定时。数据怎么在 FIFO 中进行定时,取决于串行解串器厂商以及所针对的最终应用。

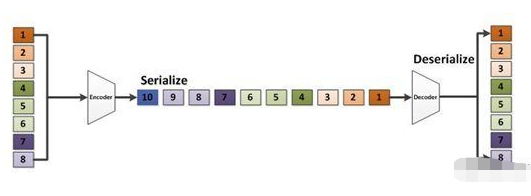

并行数据通常将编码为标准编码方案(例如 8B/10B 编码),因而适用于串行化。原始应用数据可能包含病态模式、长期运行的 1 和 0,这会使串行解串器难以捕捉位跳变。对数据进行编码能够消除病态模式,确保数据流的转换密集度平衡和 DC 平衡。未编码数据的另一个挑战是字符描述会在串行化过程中丢失,因此将数据编码为 10 位字符可确保接收器能够判定正确的字符描述。通常使用逗号字符(0011111 或 1100000)或 K28.5(0011111010 或 1100000101),也可使用其它同步字符。K28.5 字符由发送串行解串器针对接收器插入,从而可检测为对齐字符。串行化数据随后将通过介质送达接收串行解串器器件。下图 2 是 8B/10B 编码实例。

图 2:8B/10B 编码

该接收串行解串器可将流入的比特流(表现为电压摆幅)转换为数字比特流。此外,该接收器还整合有时钟数据恢复电路 (CDR),其可从流入的 DC 平衡数据流中恢复字节时钟。接收串行解串器可运行自己的本地参考振荡器,但这不仅要与恢复的字节时钟相位对齐,而且还要用于为接收到的比特流时钟计时。接收到的比特流随后可进行解串,反馈至并行总线,送达等待中的终端器件。

TLK1501 是一款多千兆位收发器,可用于高速点对点数据传输系统。TLK1501 支持 16 位大并行接口,可在参考时钟上升沿读入数据。并行总线经过 8B/10B 编码并经过串行化后,通过差分高速介质进行有序传输。TLK1501 的接收器部分可接受 8B/10B 编码数据,对此,其 CDR 将锁定从输入数据流提取比特时钟并对该数据流进行重定时。串行数据流随后对齐到分开的 10 位字符边界,经过解码后通过 16 位总线传输至等待中的终端器件。TLK1501 是一款简洁的器件,采用它进行设计,可降低系统成本与功耗,缩小板级空间。

责任编辑:gt

-

简单认识串行解串器2023-12-26 3122

-

串行解串器 (SerDes) 以及各种技术及其应用2022-11-21 909

-

获得连接:串行解串器接口2022-11-04 685

-

串行解串器以及各种技术及其应用2022-01-28 7065

-

什么是串行解串器?其有哪些应用?2021-05-24 4750

-

GMSL串行器/解串器技术的应用范围2018-10-08 13913

-

探讨串行解串器的技术及其应用2018-09-13 2396

-

人机交互系统:如何选择串行解串器?2018-08-16 4859

-

【视频】智能家居系统关键技术分析与应用2016-02-26 5085

-

英特尔在14nm制程技术上推出32 Gbps串行解串器2014-12-02 1550

-

嵌入式系统关键技术分析与开发应用2012-08-09 3736

-

Maxim推出高速LVDS串行器/解串器MAX9263/MAX9265/MAX92642011-04-14 4601

全部0条评论

快来发表一下你的评论吧 !