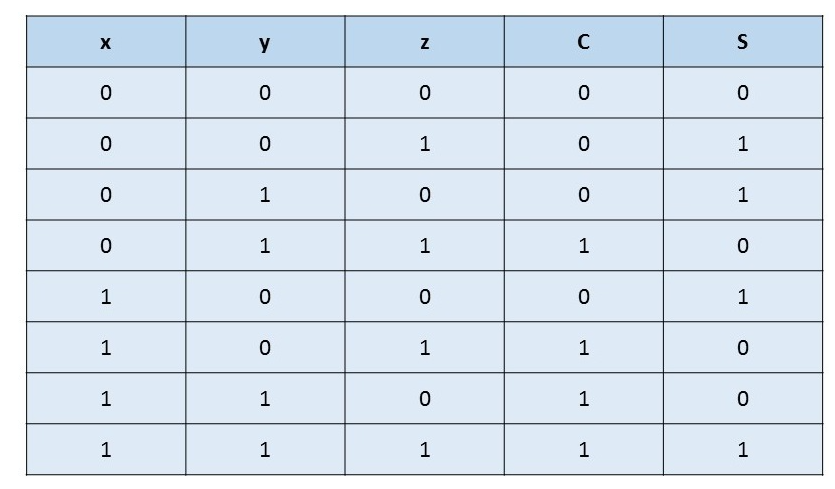

全加器的真值表

电子说

1.4w人已加入

描述

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进行级联可以得到多位。

全加器是形成三位算术和的组合电路,它由三个输入和两个输出组成。

真值表

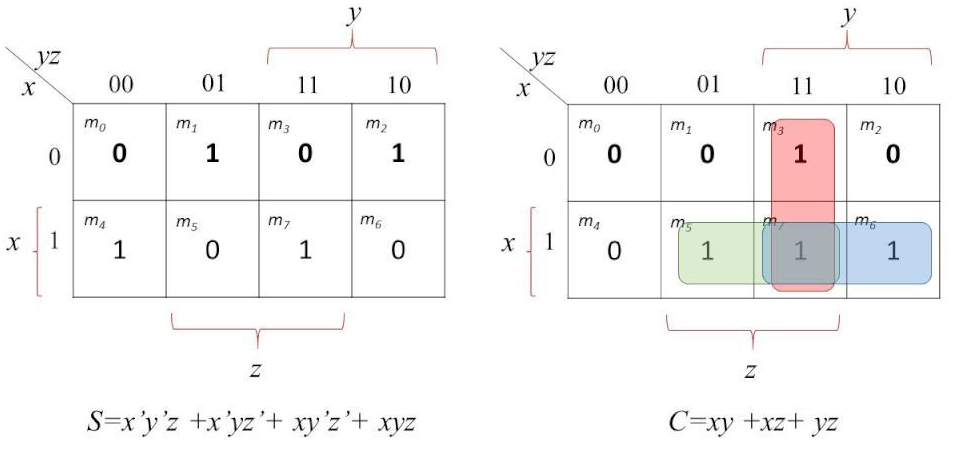

a.) 基于真值表,S 和 C 的卡诺图如下:

S 和 C 的 K 映射

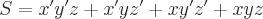

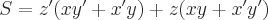

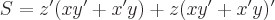

b.) S 输出可以减少为:

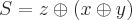

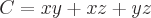

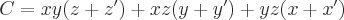

进位输出 C 为:

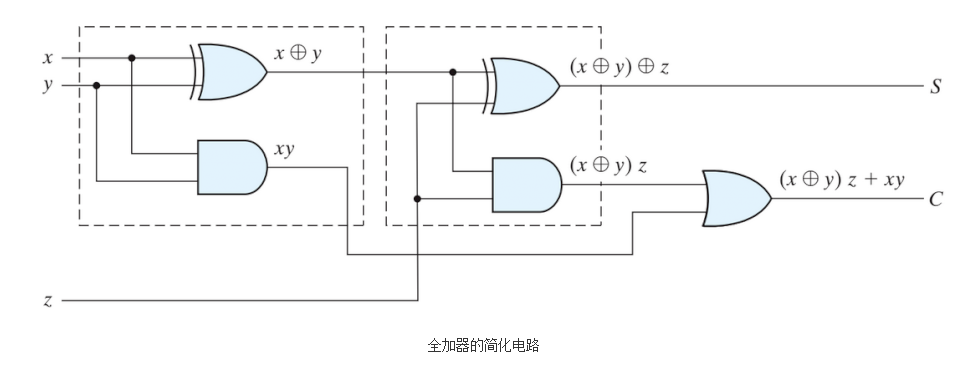

全加器的简化电路

逻辑电路变成了两个级联的半加器和一个或门。

文章来源:eeweb avon ampo

编辑:ymf

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

怎么利用QuartuesII查元件真值表2012-11-15 3439

-

74LS00芯片资料及真值表2012-12-07 22210

-

怎么利用QuartusII查元件真值表2012-12-20 7496

-

求常用单片机的功能表、引脚图、真值表2013-04-25 3304

-

关于多位输入真值表的问题2013-07-11 2619

-

帮忙看下,我仿真出来的怎么和真值表不一样啊,是不是.....2013-10-08 3876

-

输入真值表相同 输出结果不同 74HC1382014-10-26 8782

-

LUT真值表在实施期间发生了变化2018-11-01 2803

-

LUT与真值表有何关系2021-11-02 3700

-

真值表,真值表是什么意思2010-03-08 30013

-

与门真值表2011-03-20 27731

-

与门真值表和与非门真值表的区别2018-01-30 124211

-

全加器真值表和半加器真值表详细分析2018-07-25 146582

-

全加器真值表解释2021-02-18 61531

全部0条评论

快来发表一下你的评论吧 !