模拟集成电路的设计是什么 设计过程如何

描述

什么是模拟IC设计?

在本文中,我们将高层次地了解模拟集成电路的设计过程。

1模拟ICVS数字IC

首先模拟IC设计与数字IC设计上有很大的不同。数字IC的设计大多是在抽象的层次上完成的,这些层次的系统和过程决定了门/晶体管级的布局和走线的细节,而模拟IC的设计通常涉及到每个电路更多的个性化焦点,甚至是每个晶体管的尺寸和细节。

此外,许多制造工艺主要是针对具有模拟功能的数字IC开发的,这就要求模拟IC设计人员应对工艺限制和更适合数字IC的功能进行工作。

1设计规格

模拟设计团队通常从一组规格和特性开始,就像数字集成电路设计一样。从那里,各种功能的功能模型被用来进一步缩小约束,并导致关于设备大小、类型和其他过程特性的决策。这可能包括晶体管的选择,高层次的布局规划,包括电感和电容技术,以及 IC 和子电路的期望值。

体系结构硬件描述语言(AHDL) ,如 VHDL-AMS,用于在高层进行仿真,并确定子块的约束。在这个阶段也可以开发一个测试台,这个测试台后来用于仿真,尽管模拟设计人员也经常为他们的子电路设计开发测试台。

2分电路设计,物理布局和模拟

有了这些细节,并根据模拟电路的复杂性,模拟设计团队通常将子电路设计分配给个人。理想化的宏观测量进一步确定子电路的约束条件和性能期望。

接下来,这些宏示意图被分解为示意图与电路元件模型从铸造过程。对这些电路进行了仿真和优化,然后开始物理布局过程。布局和路由之后的设计规则检查(DRC)和电路佈局验证是在寄生提取和布局后仿真之前完成的。

版图后仿真可能会揭示设计中的缺陷,需要一个迭代的重新设计、版图设计和仿真过程,以满足最终的设计目标,并提交芯片进行输出。在整个芯片布局和仿真之前,子电路也可能经历它们自己的设计、布局和仿真过程,不过这两种方法都可能导致需要在tape-out之前重新设计电路。

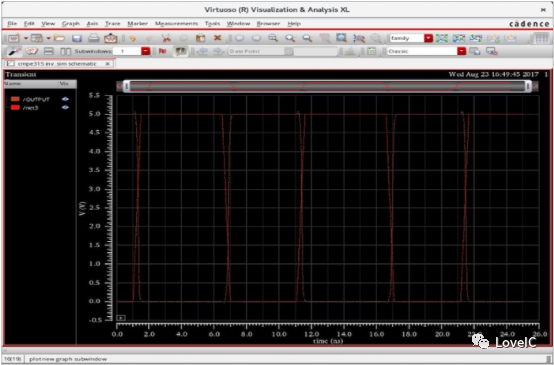

Cadence 模拟设计环境的波形窗口实例

文章出处:【微信公众号:FPGA开源工作室】

责任编辑:gt

-

简单认识模拟集成电路2023-12-08 3098

-

模拟集成电路及其构成 模拟集成电路设计过程2023-09-20 4667

-

分析与设计模拟集成电路2021-06-15 1367

-

模拟集成电路设计2021-03-22 1584

-

模拟集成电路是什么2020-05-22 6292

-

模拟集成电路的应用2019-06-12 8245

-

模拟集成电路的分析与设计,模拟集成电路的基本原理和概念是是什么?2018-07-18 2051

-

CMOS模拟集成电路设计2018-03-26 1408

-

什么是模拟集成电路?2011-11-14 5022

-

模拟集成电路与系统图书2011-10-28 1991

-

模拟集成电路,模拟集成电路是什么意思2010-03-09 2335

-

模拟集成电路基础与应用2008-11-02 1138

-

模拟集成电路原理与应用2008-08-28 1422

全部0条评论

快来发表一下你的评论吧 !