FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案

描述

所谓FPGA动态可重构技术,就是要对基于SRAM编程技术的FPGA实现全部或部分逻辑资源的动态功能变换。根据实现重构的面积不同,动态可重构技术又可分为全局重构和局部重构。

1、何为局部动态可重构

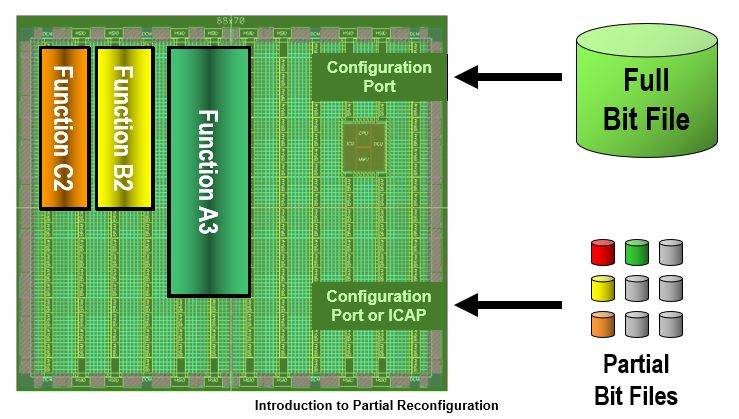

局部动态可重构可以简单的理解为通过下载局部分区bit 文件来动态修改对应分区的逻辑功能,同时其余分区的逻辑功能持续运行而不中断。

2、局部动态可重构技术的优势

a、系统灵活性:可以在保持通信连接的同时执行更多的系统功能;

b、降低FPGA资源和成本:通过分时复用的方式降低FPGA硬件尺寸;

c、降低功耗:通过卸载掉暂时不用的局部逻辑的方式降低FPGA功耗;

3、 FPGA局部动态重构流程

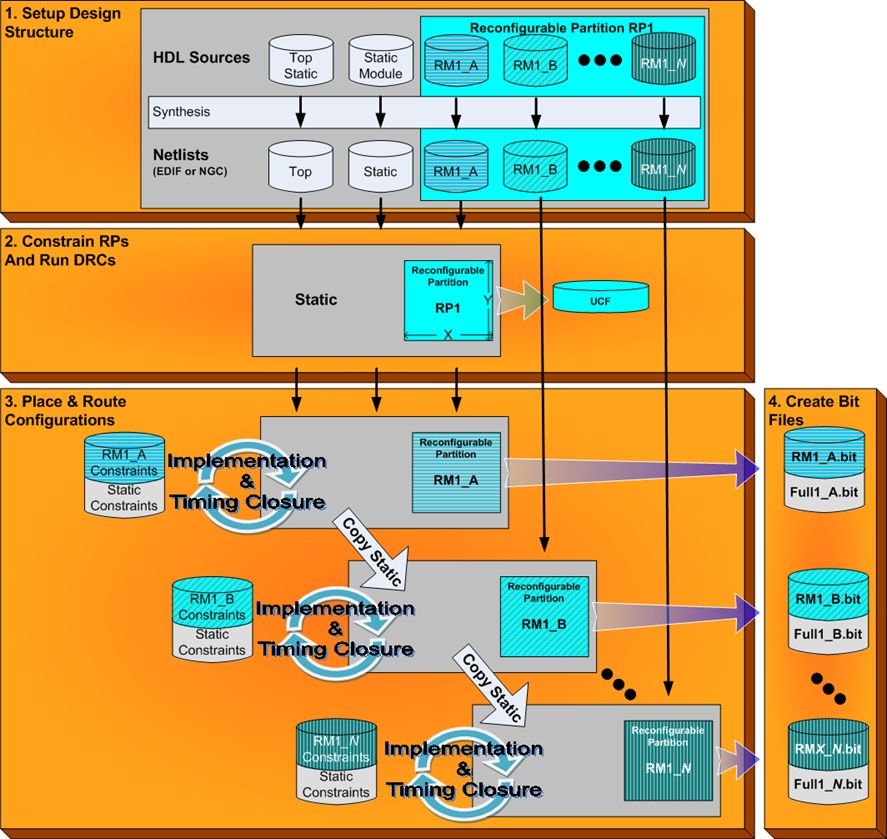

a、规划系统整体框架和可重构模块框架,编写各模块HDL代码,综合生成各子模块网表文件;

b、规划分区以及给各分区分配足够资源,创建各分区及静态部分的时序约束文件,执行DRC检查;

c、对各分区进行布局布线配置;

d、遍历各种可能的配置,编译生成全局bit文件和可重构模块的局部bit文件。

4、局部动态可重构的时序问题

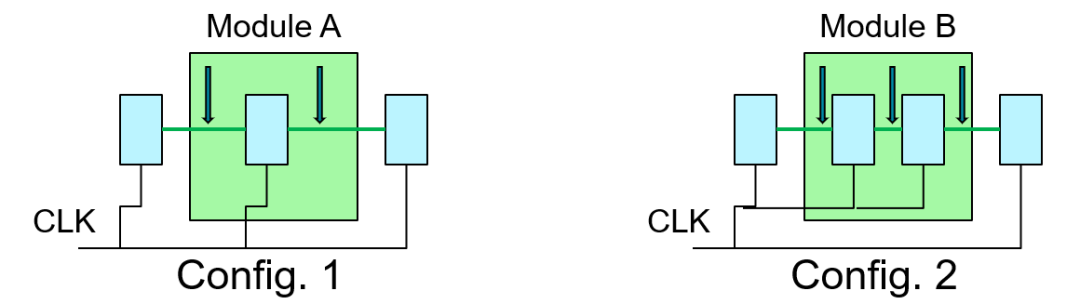

如上图所示,局部重构会带来时序路径的变化,使得局部可重构工程的时序约束问题变得更加复杂。

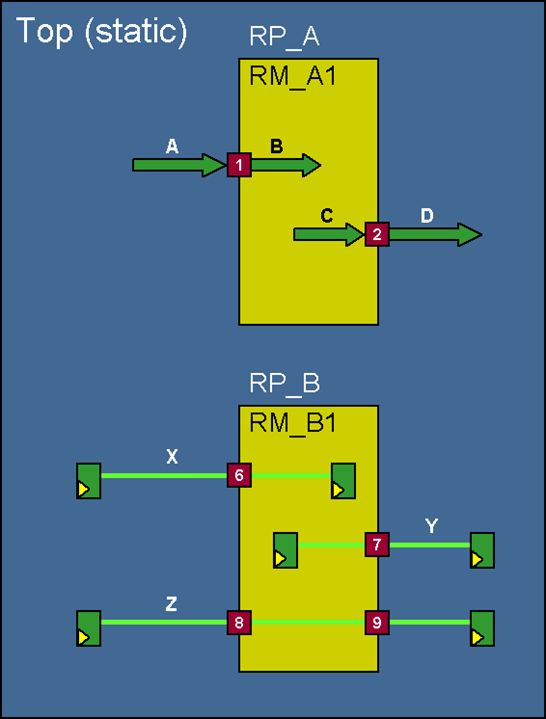

解决方法:在静态逻辑和可重构模块间的信号传递路径上添加代理逻辑点,如下图红色数字点,将单条时序路径分割为两个独立的部分,然后分别对两部分的路径进行单独约束,以达到时序要求。

文章出处:【微信公众号:OpenFPGA】

责任编辑:gt

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于xilinx ISE的动态可重构2014-03-10 2534

-

基于PAD的接收机动态可重构结构应用2019-07-10 1010

-

怎么设计PAD在接收机动态可重构结构中的应用?2019-08-13 1100

-

如何采用FPGA部分动态可重构方法设计信号解调系统?2019-09-05 1801

-

基于部分动态可重构技术的信号解调系统该怎么设计?2019-09-19 1841

-

如何在FPGA动态部分重构功能设计中进行模块化设计?2019-09-20 2588

-

可重构体系结构分为哪几种?动态可重构系统有哪些应用实例?2021-04-28 2011

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 3028

-

划分和时延驱动的动态可重构FPGA在线布局算法2010-01-18 507

-

动态可重构系统的通信结构分析2009-03-29 1411

-

PAD在接收机动态可重构结构中的应用设计2009-12-28 1058

-

基于CPLD的FPGA快速动态重构设计2017-11-22 1579

-

可重构技术分析及动态可重构系统设计2017-11-25 14673

-

如何在FPGA动态局部可重构中进行TBUF总线宏设计2018-12-14 1470

-

关于FPGA可重构技术分析2022-11-03 1434

全部0条评论

快来发表一下你的评论吧 !