TLV2544/2548多通道12位串行A/D转换器的原理与

模拟技术

描述

TLV2544/2548多通道12位串行A/D转换器的原理与应用

1 概述

TLV2544/2548是TI公司生产的一组高性能12位低功耗/高速(3.6μs)CMOS模数转换器,它精度高,体积小、通道多,使用灵活,并具有采样-保持功能,电源电压为2.7V~5.5V。另外TLV2544/2548还个有3个输入端和一个三态输出端,可为最流行的微处理器串行端口(SPI)提供4线接口。当与DSP连接时,可用一个帧同步信号(FS)来表明一个串行数据帧的开始。该器件除了具有高速模数转换器和多种控制功能外,还具有片内模拟多路器,可选择多部的模拟电压或三个内部自测试电压中的任一个外部的模拟电压或三个内部自测试电压中的任一个作为输入。TLV2544/2548工作时的功耗非常低,而软件/硬件/自动关机模式以及可编程的转换速度又进一步增强了其低功耗的特点。同时它还具有内置转换时钟(OSC)和电压基准,可以采用外部SCLK作为转换时钟源以获取更高的转换速度(在20MHz的SCLK时可高达3.6μs)。并有两种不同的内部基准电压可供选择。图1和图2分别是TLV2544/2548的功能方框图和引脚排列,表1是其引脚说明。

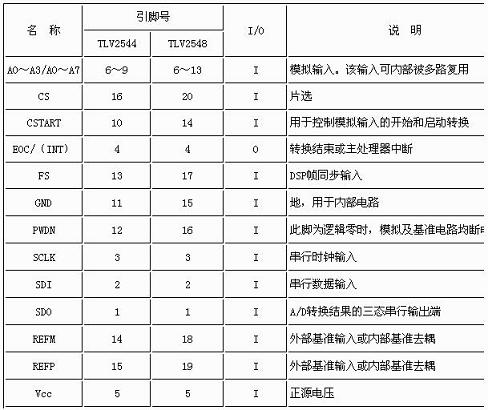

表1 引脚说明

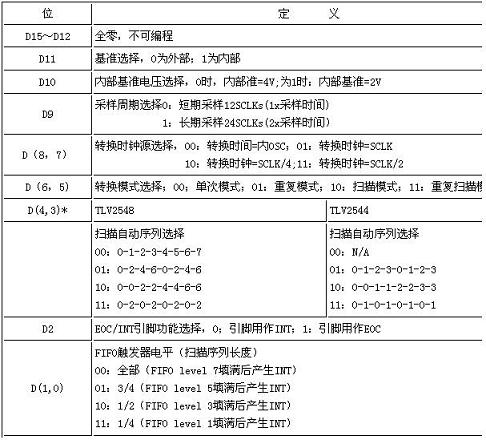

表2 TLV2544/TLV2548配置寄存器(CFR)的位定义

*这些位仅在10和11转换模式中有效

TLV2544/2548两芯片的内部功能结构相同,不同之处就是前者的模拟输入通道为4路,而后者为8路。下面以TLV2544为例为介绍。

2 工作原理

TLV2544有4路模拟输入和3个内部测试输入端,它们可由模拟多路转换器根据输入的命令来选择。输入多路转换器采用先开后合型,因为这可减少由通道切换引起的输入噪声。

TLV2544 的工作周期的开始模式有两种:一种是当不使用FS时(在CS的下降沿FS=1),CS的下降沿即为周期的开始。这时的输入数据在SCLK的上升沿移入,输出数据下降沿改变。这种模式虽然也可用于DSP,但一般常用于SPI微控制器。另一种是当使用FS时(FS是来自DSP的有效信号),FS的下降沿即为周期的开始,这时的输入数据在SCLK的下降沿移入,输出数据在其上升沿改变,这种模式一般用于TMS320系列的DSP。

TLV2544 具有一个4位命令集(存于命令寄存器CMR中)和一个12位配置数据域。大多数命令只需要前4个MSB,即不需要低12位数据。值得注意的是,器件在上电初始化时首先需要将将始化命令A000h写入CFR配置寄存器,然后对器件进行编程,其编程方法是在初始化命令A000h的低12位000h写入编程数据以规定器件的工作方式。编程定义如表2所列,编程信息被保留在H/W或S/W的断电状态。当器件被编程时,由微处理发送一个16位串行数据写入CFR,如果在输入了前8位后SCLK中断,那么余下的8位则在SCLK被恢复后再输入。一个读CFR命令可读出CFR的状态,以校验写入控制命令是否正确,其他控制命令可参见表3。

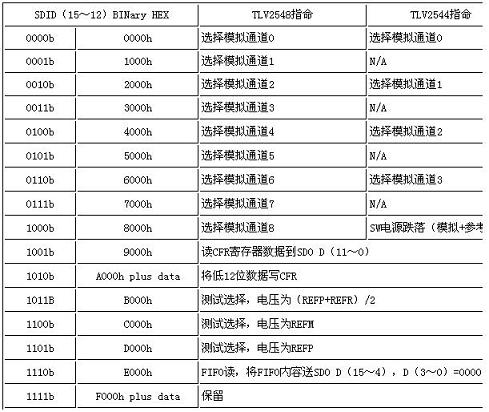

表3 TLV2544/TLV2548命令集

如果前高4位输入数据被译码为转换命令之一,那么采样周期开始。一般有两种采样方式:正常采样和扩展采样。正常采样实际上是采用软件启动A/D变换方式,当 A/D转换器正常采样时,采样周期是可编程的,它可以是12SCLKs(短周期采样)或24SCLKs(长周期采样)。当SCLK高于10MHz或输入源电阻较高时,长周期采样可使被采样的输入模拟信号达到0.5LSB的精度。如果正常采样达不到所要求的A/D变换精度,则应采用扩展采样,扩展采样采用硬件启动A/D变换,在引脚CSTART输入一个宽度大于800ns的负脉冲信号后,A/D转换开始。CSTART的下降沿即为采样周期的开始,CSTART的上升沿是采样周期的结束和转换的开始。

3 TLV2544的转换模式

TLV2544 具有四种转换模式,分别为:单次模式、重复模式、扫描模式和重复扫描模式。可用模式00、01、10、11表示。每种模式的工作稍有区别,这取决于转换器如何采样和采用哪一种接口。转换的触发信号可以采用有效CSTART(扩展采样)、CS(正常采样、SPI接口)或FS(正常采样,TMS320系列 DSP接口)模式。当FS用作触发信号时,CS可保护一直有效而不需要通过触发顺序跳转。不同类型的触发信号不应在重复模式和扫描模式中混合使用。当 CSTART用作触发信号时,转换开始于CSTART的上升沿。如果一个有效CS或FS用作触发信号,则转换将在第16个或第28个SCLK的边沿开始。

TLV2544/2548 的工作时序分为二大类:转换和无转换。无转换周期为读和写周期(配置),这些周期都不执行转换,而转换周期有四种转换模式的周期,图3、图4分别给出了 TLV2544/2548的CFR写周期(FS=1)和模式00时单次扩展采样(使用FS信号,FS脚连至TMS320系列DSP)时序图。

另外,TLV2544/2548还具有一个内置基准,其电平可编程为2V或4V。如果采用内部基准,REFP就被设为2V/4V,而REFM则设为0V。如果基准源编程为外部,那么也可通过两个基准输入脚REFP和REFM使用外部基准。模拟输入、外部基准的最大或最小值不应超过正电源或低于GND。正输入信号等于或高于REFP时,数字输入为满度,而在输入信号等于或低于REFM时为零。

器件的上电和初始化要求先通过向TLV2544/2548写入A000h的方法确定处理器的类型,然后对器件进行编程。器件在上电后或从断电方式中恢复后的第一次转换无效。

4 应用

TLV2544 和微处理器之间的数据传输最快和最有效的方法是用串行外设接口(SPI),但这要求微带有SPI接口能力。对不带SPI或类似接口能力的微处理器,需用软件合成SPI操作来和TLV2544连接。图5为TLV2544和单片机AT89C2051的接口电路,因为是与微处理器连接,所以不用FS端(接至高电平)。该电路采用内部基准,REFP与REFM之间接0.1μF和10μF两个退耦电容。TLV2544的SDI、SCLK、EOC/INT、CS端由单片机的双向I/O口中的P1.3、P1.4、P1.5和P1.6提供。转换结果的输出(SDO)数据由口1的P1.2接收。电路使用扩展采样方式, CSTART端接P1.7,通过硬件来控制采样与转换。其接口软件由一个主程序和一个子程序组成。主程序首先对P1口初始化,后对TLV2544进行编程以确定的工作方式。子程序“SPI-IO”用来模拟SPI的I/O操作,SPI功能用累加器A和带进位的左循环移位指令(RLC)模拟SPI移位寄存器的操作来实现。程序如下:

ORG 0000H

AJMP START

ORG 0030H

START:MOV P1,#0FFH

MOV P3,#0FFH

CLR EA

CLR ET1

CLR P1.4

SETB P1.6

CONFIG:MOV R1,#0A0H

ACALL SPI_IO

MOV R1,#00H

ACALL SPI_IO

SETB P1.6

MOV R1,#10101000B;

ACALL SPI_IO

MOV R1,#00000000B

ACALL SPI_IO

SETB P1.6

S/R:MOV R1,#ACALL SPI_IO

RESULT

MOV R1,#00H

ACALL SPI_IO

MOC R3,A;LOW BYTE RESULT

SETB P1.6

NOP

CLR P1.7/CSTART LOW,START SAMPLING

MOV R6,#08H

DELAY:NOP

NOP

NOP

DJNZ R6,DELAY

SETB P1.7;

JB P1.5,$;/INT

SETB P1.6

·对转换结果的处理

AJMP S/R

SPI_IO;CLR P1.6

CLR P1.4

MOV R0,#08H

MOV A,R1

SPI_IO1:MOV C,P1.2

RLC A

MOV P1.3,C

SETB P1.4

CLR P1.4

DJNZ R0,SPI_IO1

RET

-

TLV2544Q,TLV2548Q,TLV2548M模数转换器(ADC)数据表2024-07-31 416

-

TLV2548和TLV2544 CMOS模数转换器(ADC)数据表2024-07-16 412

-

PM7543:12位串行输入倍增CMOS D/A转换器废弃数据表2021-05-20 1085

-

LTC1594/LTC1598:4通道微功耗采样12位串行I/O A/D转换器数据表2021-05-09 996

-

DAC8143:12位串行菊花链CMOS D/A转换器数据表2021-05-08 1043

-

DAC8043A:12位串行输入乘法D/A转换器数据表2021-05-07 1047

-

关于TLV2544的知识点总结的太棒了2021-04-20 1380

-

LTC1598的8通道,微功耗采样12位串行I / O A / D转换器2020-06-16 1070

-

4通道和8通道3V微功耗采样12位串行I/OA/D转换器2019-06-10 1416

-

比较TLV2462,TLV2272和TLV2544,TLV2548的AC性能的方法的概述2018-05-29 2110

-

多通道14位串行AD转换器MAX11482016-01-25 860

-

TLV2544/TLV2548,pdf (2.7-V to2010-06-04 922

全部0条评论

快来发表一下你的评论吧 !