十进制计数器,十进制计数器原理是什么?

基础知识

描述

十进制计数器,十进制计数器原理是什么?

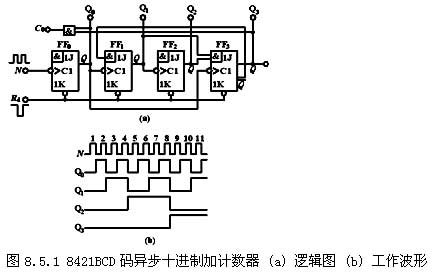

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特别是当二进制数的位数较多时,阅读非常困难,还有必要讨论十进制计数器。在十进制计数体制中,每位数都可能是0,1,2,…,9十个数码中的任意一个,且“逢十进一”。根据计数器的构成原理,必须由四个触发器的状态来表示一位十进制数的四位二进制编码。而四位编码总共有十六个状态。所以必须去掉其中的六个状态,至于去掉哪六个状态,可有不同的选择。这里考虑去掉1010~1111六个状态,即采用8421BCD码的编码方式来表示一位十进制数。 8.5.1 8421BCD码异步十进制加计数器: 用JK主从触发器组成的一位异步十进制加计数器如图8.5.1(a)所示。 1.电路结构: 由四个JK主从触发器组成,其中FF0始终处于计数状态。Q0同时触发FF1和FF3,Q3反馈到J1,Q2Q1作为J3端信号。 2.工作原理 (1)工作波形分析法由逻辑图可知,在FF3翻转以前,即从状态0000到0111为止,各触发器翻转情况与异步二进制递增计数器相同。第八个脉冲输入后,四个触发器状态为1000,此时Q3=0,使下一个FF0来的负阶跃电压不能使FF1翻转。因而在第十个脉冲输入后,触发器状态由1001变为0000,而不是1010,从而使四个触发器跳过1010~1111六个状态而复位到原始状态0000,其工作波形如图8.5.1(b)所示。

当第十个脉冲作用后,产生进位输出信号C0=Q3Q0。

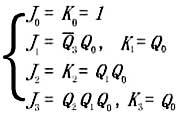

(2)状态方程分析法: 首先列出各触发器驱动方程:

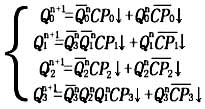

触发器在异步工作时,若有CP触发沿输入,其状态由特征方程确定,否则维持原态不变。这时触发器的特征方程可变为Qn+1=(JQn+KQn)CP↓+QnCP↓,其中CP↓=1表示有CP触发沿加入,CP=0表示没有CP触发沿加入。所以可以写出以下状态方程:

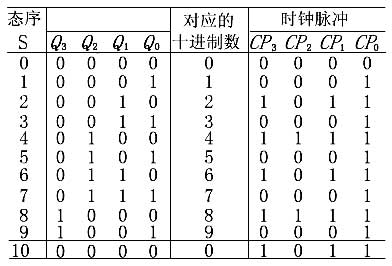

根据以上状态方程,即可列出计数器的状态转移表,如表8.5.1所示。表8.5.1 异步十进制加计数器的状态转移表

以上两种方法均表明该逻辑电路具有8421码异步十进制递增计数的功能。

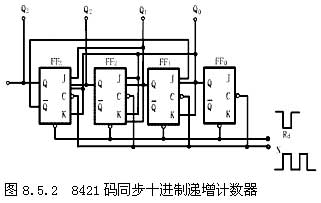

8.5.2 8421码同步十进制加计数器: 1.电路结构如图8.5.2所示,由四个主从JK触发器组成,各触发器共用同一个计数脉冲,是同步时序逻辑电路。

2.工作原理: 各触发器方程:

由于各触发器共用同一个时钟脉冲,故上式中的CP↓可忽略不写。 (3)列状态转移表设计数器状态为Q3Q2Q1Q0=0000,根据状态方程可列出状态转移真值表,该表与表8.5.1相同(不包括CP部分)。所以该电路是8421码十进制递增计数器。

-

十进制和4位二进制计数器数据表2024-05-31 593

-

双4位十进制和二进制计数器数据表2024-05-13 427

-

双十进制纹波计数器-74HC_HCT3902023-02-15 787

-

基于FPGA的十进制计数器2022-12-20 1045

-

十进制计数器的工作原理2022-10-31 30207

-

CD4017十进制计数器的应用实验2022-05-11 1273

-

74ls160十进制计数器2018-01-18 265432

-

十进制计数器/分频器2017-04-06 3965

-

二五十进制计数器2016-03-22 1706

-

DIY十进制计数器2013-12-03 3710

-

4位十进制可逆计数器电路2010-12-10 7811

-

8421码同步十进制递增计数器2009-09-24 6883

-

十进制计数器工作原理2008-01-21 30760

-

十进制计数器2007-06-20 5519

全部0条评论

快来发表一下你的评论吧 !