全加器,全加器是什么意思

半导体器件

描述

全加器,全加器是什么意思

full-adder

用门电路实现两个二进数相加并求出和的组合线路,称为一个全加器。

一位全加器 全加器是能够计算低位进位的二进制加法电路

一位全加器(FA)的逻辑表达式为:

S=A⊕B⊕Cin

Co=AB+BCin+ACin

其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;

如果要实现多位加法可以进行级联,就是串起来使用;比如32位+32位,就需要32个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法,

超前进位加法前查阅相关资料;

如果将全加器的输入置换成A和B的组合函数Xi和Y(S0…S3控制),然后再将X,Y和进位数通过全加器进行全加,就是ALU的逻辑结构结构。

即 X=f(A,B)

Y=f(A,B)

不同的控制参数可以得到不同的组合函数,因而能够实现多种算术运算和逻辑运算。

半加器、全加器、数据选择器及数据分配器

一、实验目的

1.验证半加器、全加器、数据选择器、数据分配器的逻辑功能。

2.学习半加器、全加器、数据选择器的使用。

3.用与非门、非门设计半加器、全加器。

4.掌握数据选择器、数据分配器扩展方法。

二、实验原理

1.半加器和全加器

根据组合电路设计方法,列出半加器的真值表,见表7。逻辑表达式为:

S =AB + AB= A⊕B

C = AB

半加器的逻辑电路图如图17所示。

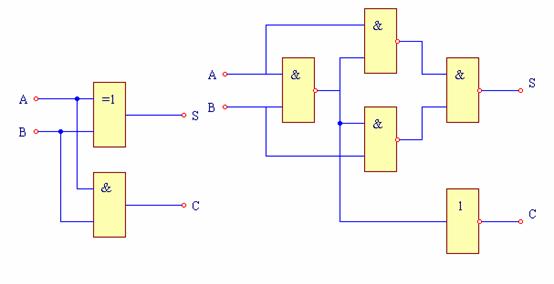

用两个半加器可组成全加器,原理图如图18所示。

在实验过程中,我们可以选异或门74LS86及与门74LS08来实现半加器的逻辑功能;也可用全与非门如74LS00、反相器74LS04组成半加器。这里全加器不用门电路构成,而选用集成的双全加器74LS183。其管脚排列和逻辑功能表分别见图19和表4.9所示

(a)用异或门组成的半加器(b)用与非门组成的半加器

图17 半加器逻辑电路图

图18 由二个半加器组成的全加器

图19 74LS183双全加器管脚排列图

2.数据选择器和数据分配器

数据选择器又叫多路开关,其基本功能相当于单刀多位开关,其集成电路有“四选一”、“八选一”、“十六选一”等多种类型。这里我们以“八选一”数据选择器74LS151为例进行实验论证。

数据分配器,实际上其逻辑功能与数据选择器相反。它的功能是使数据由1个输入端向多个输出端中的某个进行传送,它的电路结构类似于译码器。所不同的是多了一个输入端。若选择器输入端恒为1,它就成了上一实验的译码器。实际上,我们可以用译码器集成产品充当数据分配器。例如,用2-4线译码器充当四路数据分配器,3–8线译码器充当八路数据分配器。就是将译码器的译码输出充当数据分配器输出,而将译码器的使能输入充当数据分配器的数据输入。

三、实验内容与步骤

1.半加器、全加器

(1)根据组合电路设计方法,列出半加器的逻辑功能表,见表7。由异或门74LS86和与门74LS08组成半加器,半加器的实验电路图如图20所示。74LS86的管脚排列图见图21所示(74LS08管脚排列图见门电路实验的图2)。

将74LS86、74LS08集成片插入IC空插座中,按实验电路图20接线,进行半加器逻辑功能验证。

实验时输入端A、B接输入信号,输出端S、C接发光二极管LED,观察和数与进位数,并记录。

(2)全加器逻辑功能验证:本实验中全加器不用门电路构成,而选用集成的双全加器74LS183。将74LS183集成片插入IC空插座中验证其逻辑功能与表8中结果进行比较。

图20 用异或门组成的半加器实验电路图

图21 74LS86管脚排列图

表7 半加器逻辑功能表

|

输 入 |

和 |

进 位 |

|

A B |

S |

C |

|

0 0 0 1 1 0 1 1 |

0 1 1 0 |

0 0 0 1 |

表8 全加器逻辑功能表

|

输 入 |

输 出 |

|

Ci-1 B A |

Si Ci |

|

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 |

0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 |

将全加器74LS183集成片插入IC空插座,输入端A、B、Ci-1分别接逻辑开关K1、K2、K3,输出Si和Ci接发光二极管LED。按全加器逻辑功能表输入逻辑电平信号,观察输出Si及进位Ci并记录下来。

2.数据选择器和数据分配器

(1)数据选择器

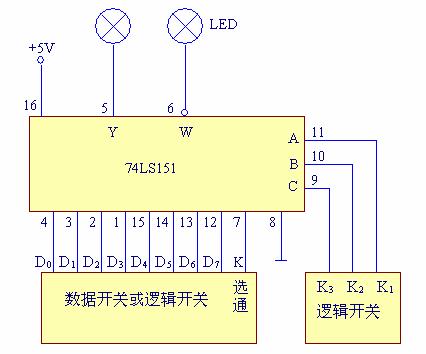

将74LS151“八选一”数据选择器插入IC空插座中(管脚排列图如图22所示),按图23接线。其中C、B、A为三位地址码,S为低电平选通输入端,D0~D7为数据输入端,输出Y为原码输出端,W为反码输出端。置选通端S为0电平(即低电平),数据选择器被选中,拨动逻辑开关K3~K1分别为000,001,…111(置数据输入端D0~D7分别为10101010或11110000),观察输出端Y和W输出结果,并记录。

图22 74LS151管脚排列图

图23 八选一数据选择器实验接线图

(2)数据分配器,其逻辑功能与数据选择器相反,常常用译码器集成片充当数据分配器。在多路分配器中用3线-8线74LS138译码器接成数据分配器形式,从而完成多路信号的传输。具体实验接线见图24。

图24 多路信号传输实验接线图(多路分配器)

将74LS138集成片插入IC空插座中(管脚排列图见“编码器”图4.27),按图4.46接线。D0~D7分别接数据开关或逻辑开关,D'0~D'7接8个发光二极管LED显示输出,数据选择器和数据分配器的地址码一一对应相连,并接三位逻辑电平开关(也可用8421码拨码开关的4、2、1三位或三位二进制计数器的输出端QC、QB、QA)。把数据选择器74LS151原码输出端Y与74LS138的G2A和G2B输入端相连,二个集成片的通选分别接规定的电平。这样即完成了多路分配器的功能验证。

置D0~D7为11110000和10101010两种状态,再分别两次置地址码A3~A0为0~7,观察输出发光二极管LED的状态,并记录。

四、实验总结

1.整理实验数据和实验线路图。

2.试用数据选择器实现全加器及比较器功能,画出具体线路图。

五、注意事项

所有实验用集成片在实验时都必须接“+5V”电源和接地。

- 相关推荐

- 热点推荐

- 全加器

-

半加器和全加器的区别是什么2024-10-18 12929

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1577

-

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)2021-12-05 659

-

如何对全加器进行实验2021-10-29 2326

-

怎样去设计一种基于FPGA的1位全加器2021-09-17 1671

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 1553

-

全加器的真值表2021-06-29 63045

-

全加器逻辑表达式_全加器的逻辑功能2020-04-23 134587

-

高性能CMOS全加器设计的详细资料说明2019-07-03 2972

-

请问Quartus2中的用一位全加器来实现四位全加器2019-03-06 6248

-

全加器是什么?全加器和半加器的区别?2018-07-25 76406

-

什么是一位全加器,其原理是什么?2010-03-08 78268

-

全加器2009-04-07 10178

全部0条评论

快来发表一下你的评论吧 !