简述FPGA中亚稳态的产生机理及其消除方法

描述

亚稳态的概念

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

FPGA纯工程师社群

亚稳态产生原因

在同步系统中,触发器的建立/保持时间不满足,就可能产生亚稳态。当信号在异步时钟域或者不相关电路间传输时,往往导致亚稳态的产生。系统中有异步元件时,设计的电路要减少亚稳态导致错误的产生,其次要使系统对产生的错误不敏感。

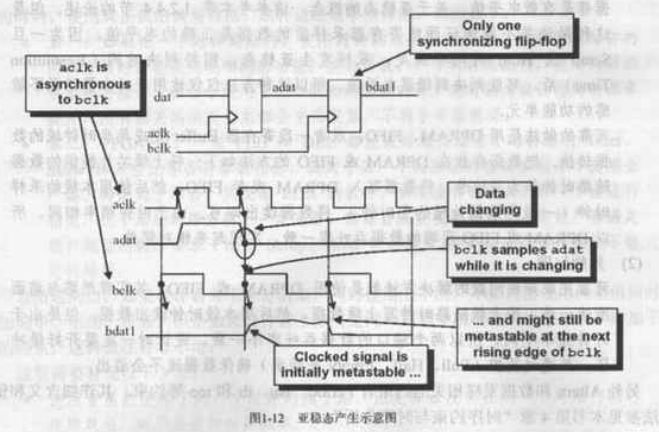

异步时钟域转换的核心就是保证下级时钟对上级时钟数据采样的 Setup 和 Hold 时间。如果触发器的 Setup 和 Hold 时间不满足,就可能产生亚稳态,此时触发器输出端 Q 在有效时钟沿之后比较长的一段时间内处于不确定的状态。

在这段时间内 Q 端产生毛刺并不断振荡,最终固定在某一电压值,此电压值并不一定等于原来数据输入端 D 的数值,这段时间成为决断时间(Resolution time)。经过 Resolution time 之后 Q 端将稳定到 0 或 1 上,但是究竟是0 或 1,这是随机的,与输入没有必然的联系,如下图所示:

亚稳态的危害

亚稳态的危害主要体现在破坏系统的稳定性。由于输出在稳定下来之前可能是毛刺,振荡或固定的某一电压值,因此亚稳态将导致逻辑误判,严重情况下输出 0 ~1 之间的中间电压值还会使下一级产生亚稳态,即导致亚稳态传播。逻辑误判导致功能性错误,而亚稳态的传播则扩大了故障面。

另外,在亚稳态状态下,任何诸如环境噪声、电源干扰等细微扰动豆浆导致更恶劣的状态不稳定,这是这个系统的传输延迟增大,状态输出错误,在某些情况下甚至会使寄存器在两个有效判定门限(VoL、VoH)之间长时间振荡。

降低亚稳态发生概率的方法

只要系统中有异步元件,亚稳态就无法避免,因此设计的电路首先要减少亚稳态导致的错误,其次要使系统对产生的错误不敏感。前者要靠同步设计来实现,而后者根据不同的设计应用有不同的处理办法。

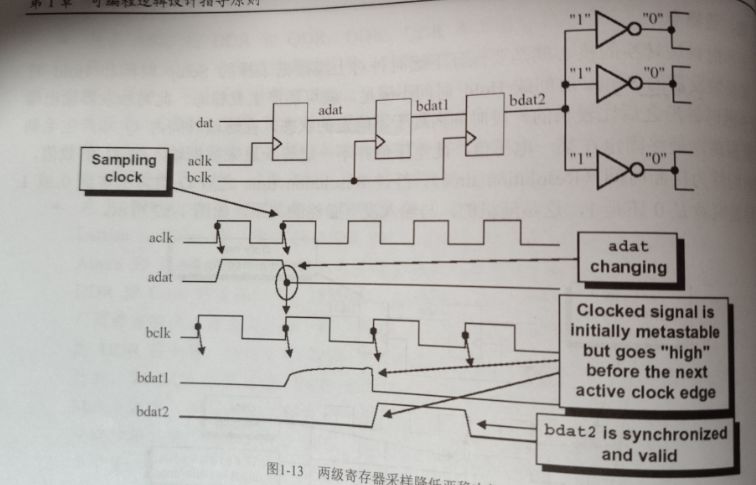

使用两级寄存器采样可以有效地减少亚稳态继续传播的概率。如下图所示,左边为异步输入端,经过两级触发器采样,在右边的输出与 bclk 同步,而且该输出基本不存在亚稳态。其原理是及时第一个触发器的输出端存在亚稳态。

经过一个 Clk 周期后,第二个触发器 D 端的电平仍未稳定的概率非常小,因此第二个触发器 Q 端基本不会产生亚稳态。理论上如果再添加一级寄存器,使同步采样达到 3 级,则末级输出为亚稳态的概率几乎为 0 。

用上图所示的两级寄存器采样仅能降低亚稳态的概率,并不能保证第二级输出的电平就是正确电平。前面说过经过 Resolution time 之后寄存器输出的电平是一个不确定的稳定值,也就是说这种处理方法并不能排除采样错误的产生,这时要求所设计的系统对采样错误有一定的容忍度。

有些应用本身就对采样错误不敏感,如一帧图像编码,一段语音编码等;而有些系统对错误采样比较敏感,这类由于亚稳态造成的采样是一些突发的错误,所以可以采用一些纠错编码手段完成错误的纠正。

编辑:jq

- 相关推荐

- 热点推荐

- FPGA

-

数字电路中的亚稳态是什么2024-05-21 3459

-

FPGA设计中的亚稳态解析2023-09-19 3785

-

简述噪声的产生机理和来源2023-08-22 3244

-

什么是亚稳态?如何克服亚稳态?2023-05-18 6306

-

今日说“法”:让FPGA设计中的亚稳态“无处可逃”2023-04-27 901

-

亚稳态产生原因、危害及消除方法2022-09-07 11745

-

FPGA--中复位电路产生亚稳态的原因2020-10-22 2099

-

在FPGA复位电路中产生亚稳态的原因2020-10-19 1755

-

简谈FPGA学习中亚稳态现象2018-06-22 4106

-

基于FPGA的亚稳态参数测量方法2017-01-07 822

-

FPGA中亚稳态——让你无处可逃2012-01-11 4683

-

一种消除异步电路亚稳态的逻辑控制方法2011-10-01 1205

-

利用IDDR简化亚稳态方案2010-12-29 3633

全部0条评论

快来发表一下你的评论吧 !