深入分析intel FPAG AES应用笔记

电子说

描述

FPGA在运行期间,把配置文件存储在SRAM中。SRAM是易失性的。掉电之后会丢失,所以FPGA每次上电都要从外部的Flash中加载数据到FPGA。这样在加载时Flash中的数据很有可能被拦截,被拦截的数据如果没有被加密则很有可能被盗用。

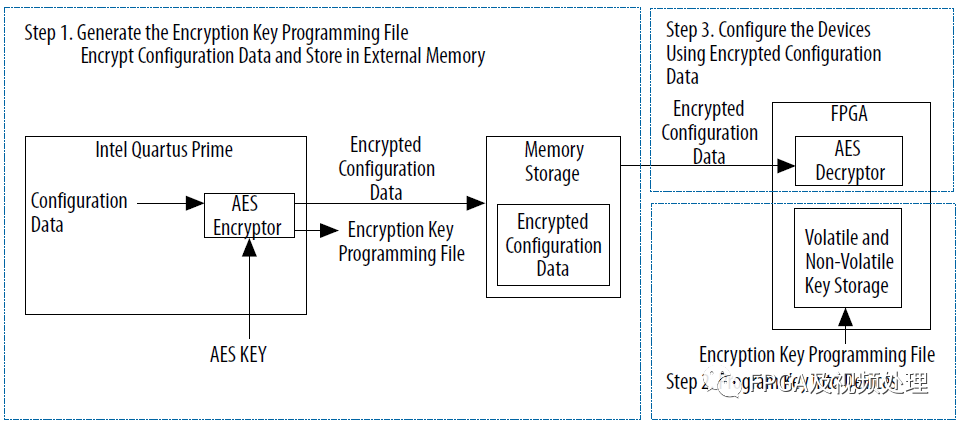

通俗的讲加密的原理就是,用户用自己的密钥把配置文件进行加密,并把密钥烧写到FPGA;FPGA通过该密钥再对配置文件解密,并把解密后的数据存放在SRAM中。

这里以一个实验来描述AES的操作步骤,软件采用QuartusPrame 18.1 Standard版本,硬件采用的是arrow的Cylone V soc demo板。

步骤如下:

1、通过用户寄密钥生成.ekp 文件,并加密配置数据。

2、将用生成的密钥加密编程到FPGA 中。

3、配置FPGA 器件。

1、通过用户寄密钥生成.ekp 文件,并加密配置数据。

这里以Arria10为例。

在菜单File -》 Convert Programming File

选择sof烧写文件,点击Properties,打开Bitsteam Encryption对话框。

添加密钥的两种方式,一种是手动256位16进制数字,一种是添加文件。

(1)添加key文件。

key文件的后缀为.key。格式为:

The “#” symbol is used to denote comments. Each valid key line has the following format: 《key identity》《white space》《256-bit hexadecimal key》。

(2)通过按键输入密钥

点击Add。在这里Key Name我们命名为‘aa‘,Key要求256位,这里手动添加了’0123456789abcfef0123456789abcfef0123456789abcfef0123456789abcfef’。这让我想起以做加密的时候遇到的一个问题:就是数据的LSB是指0还是指f呢?当然这里是完全不需要关注的。

设置完成后点击ok,再Convert Programming File对话框中的Generate就生成了加密的.ekp和加密和配置文件(这里以jic为例)。

2、将用生成的密钥加密编程到FPGA 中。

FPGA 内嵌一个专用的解密模块,通过运用AES 算法对采用用户定义的256-bit 密钥的配置数据进行解密。您必须在接收到加密数据前将用户定义的256- bit 密钥写入器件中。

FPGA 支持易失性以及非易失性密钥存储。易失性密钥需要电池来存储和更新密钥,而

非易失性密钥存储仅支持对一个密钥进行编程,不需要电池。电池的供电PIN为VCCBAT.

并通过Tools-》Options-》Programmer来配置烧写的密钥寄存器位置。

勾选Configure volatile design security key when available来配置易失性密钥寄存器。

不勾选 Configure volatile design security key when available则配置非易失性密钥寄存器。

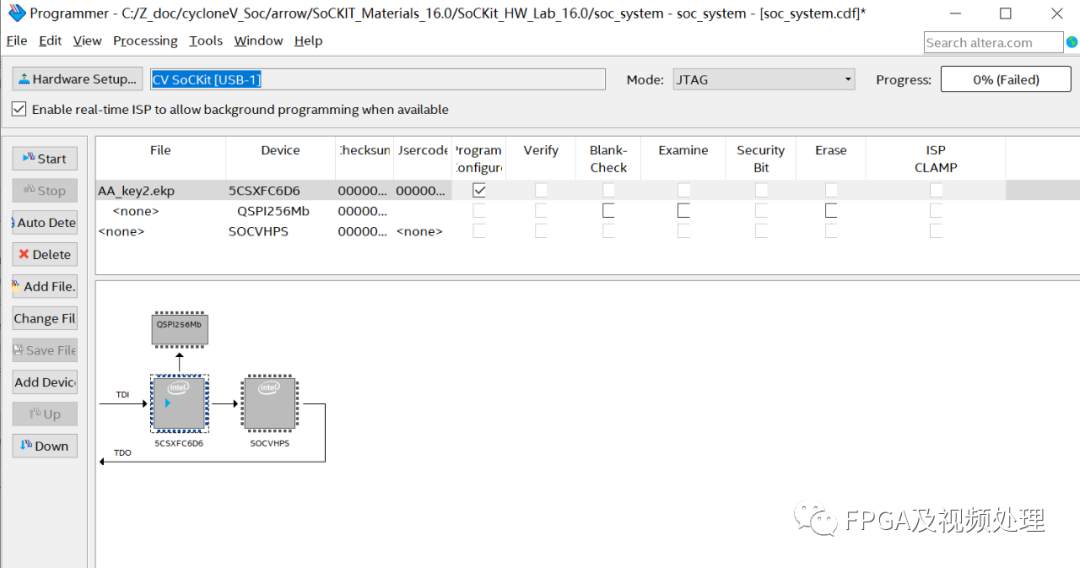

mode模式选择JTAG.先烧写.ekp文件到密钥寄存器,再烧写jic文件配置器件。

下图是烧写时可能遇到的错误。

3、配置FPGA 器件。

FPGA 内嵌一个专用的解密模块,通过运用AES 算法对采用用户定义的256-bit 密钥的配置数据进行解密。FPGA上电之后会把配置芯片的数据加载到FPGA通过密钥和解密模块对加密的数据进行解密,再把解密后的配置数据加载到SRAM中去。

要说明的是成功地将易失性密钥编程到FPGA 器件中后,该器件既能够接受加密的配置数据,也能够接受未加密的配置数据。如果用带有使用错误的密钥进行加密的配置文件对FPGA 进行配置,都将导致配置的失败。如果这种情况发生,那么来自FPGA 的nSTATUS 信号将变低。

另外FPGA还可以设置篡改保护位,对FPGA的烧写应用会也有很大的影响。详细的文档说明请看an556,an556_cn.

文章出处:【微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

编辑:jq

- 相关推荐

- 热点推荐

- FPAG

-

深入分析LED电源损坏原因2016-04-20 10152

-

深入分析运放的作用2024-01-15 5698

-

Xilinx_FPGA_内部结构深入分析2012-08-02 2777

-

uCOS任务堆栈的深入分析(转)2012-08-24 4694

-

PSoC 3/5 数字设计优秀应用笔记推荐!2012-11-21 5122

-

FIFO中文应用笔记2009-07-28 535

-

深入分析Windows和Linux动态库应用异同2008-10-22 1457

-

笔记本的结构深入分析2010-01-21 4791

-

如何深入分析电源电路技巧(二):驾驭噪声电源2012-06-08 3144

-

深入分析MCU堆栈的作用 以及该如何设置堆栈大小2020-03-01 6456

-

SmartMesh IP应用笔记2021-04-21 1299

-

AN-761应用笔记2021-05-24 971

-

(转)深入分析STM32单片机的RAM和FLASH2021-12-02 1025

-

ADI应用笔记合集2022-02-18 1397

-

深入分析:大带宽竞争形势下同轴接入网的价值2023-11-10 492

全部0条评论

快来发表一下你的评论吧 !