你们会设计CPU取指执行电路吗?

描述

【前言】

最近手上写了一个练手的小项目,项目的大致要求是实现一个取指,执行电路。取指的指令预存在,从ROM中读取指令后,根据预定的解码规则,对指令进行解码,并执行相对应的操作。发出来和大家共同分享。

该工程的设计要求如下:

在ram模块中,储存有初始化的指令数据。我们要设计一个取指电路,并能根据不同的指令执行不同的操作。指令数据为16bit.

指令编码定义如下:

如果指令代码为0,则下一个状态为空闲。如果指令的低位8位为0,高位8位非0,则读取指定高位8位的存储器,并将其写入obuf0。如果指令的低8位非0,且高8位也不是0,则将下8位作为数据,写入地址为上8位的存储器中。

List4显示了指令获取电路。它实例化了五个模块:PC0(程序计数器、8位计数器)、Ir0(指令寄存器、16位计数器)、OBUF0(输出缓冲器、16位计数器)、STATE0(状态机)和RAM0(存储器,8位256字块RAM)。模块pc0用于指定要读取的地址,以便从ram0获取(提取)指令代码。指令代码存储在IR0中。

此指令获取操作在两种状态下执行:fetcha和fetchb。fetcha用于取地址操作,该地址作为读取ram中指令的地址,fetchb用于指令寄存操作,将指令寄存到指令寄存器中。

在execa和execb状态下,执行表1中的操作。如果存储在IR0中的指令代码为0,则下一个状态为空闲。如果指令的低位8位为0,高位8位非0,则读取指定高位8位的存储器,并将其写入obuf0。如果指令的下8位非0,则将下8位写入地址为上8位的存储器。

指令解码列在table1中

顶层代码如图所示:

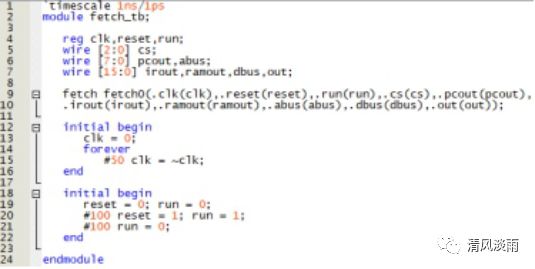

下面是该工程的测试模块:

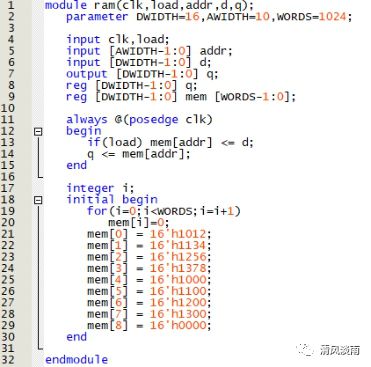

下面的ram模块的代码:

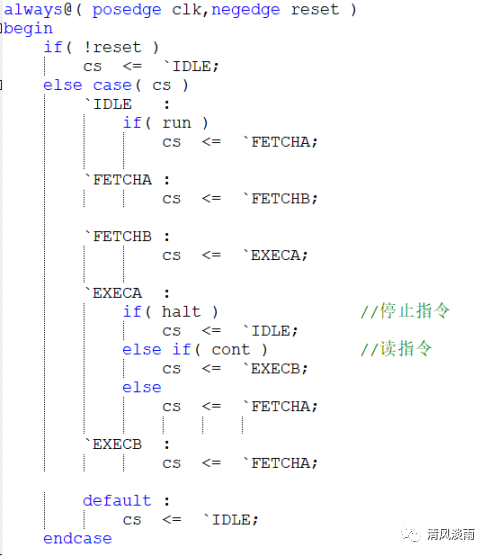

状态控制模块的代码:

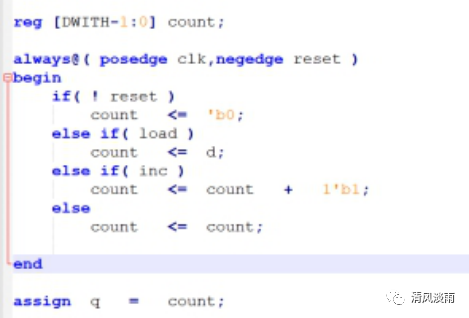

计数器模块的代码:

设计说明

该工程有以下模块组成:

PC0(程序计数器、8位计数器)、

Ir0(指令寄存器、16位计数器)、

OBUF0(输出缓冲器、16位计数器)、

STATE0(状态机)、

RAM0(存储器,8位256字块RAM)。

其中,PC0,IR0,OBUF0是例化计数器模块得到的,该计数器模块拥有计数和寄存数据两个功能,分别由端口 inc 和 端口 load 控制。

当 inc有效时,在下一个时钟,会将计数器内部的计数器自增1,并在q端输出。

当load信号有效时,在下一个时钟会将D端 的数据寄存到该计数器的寄存器中,并在Q端输出。

PC0利用的是计数器的计数功能,用于产生取指令的地址信息。

IR0利用的是计数器的寄存功能,用于将ram中取出的指令暂时寄存。

OBUF0利用的是计数器的寄存功能,用于将输出中暂时寄存。

在状态机控制模块中,设置了以下五个状态:

IDLE:空闲态。

FETCHA:取地址状态。同时将程序计数器的内部计数值加一。

FETCHB:取指令,指令寄存状态。将从ram中读出的指令写入到指令寄存器模块中。

EXECA:指令解码模块,判断指令的停止,读,写控制信号。如果为写信号,将指令的低8位作为数据写到高8位对应的地址中。如果为读指令,跳转到EXECB状态,将指令的低8位输出。如果停止信号为真3,跳转到空闲状态。

EXECB:执行状态。用于将指令的低8位输出。

在ram模块中,储存有初始化的指令数据。

编辑:jq

- 相关推荐

- 热点推荐

- c

-

做***点阵LED你们用取模软件吗2013-11-01 5664

-

cpu执行指令的过程详解2018-03-09 106999

-

单片机执行指令过程详解2019-02-15 20451

-

80C51单片机指令的取指和执行时序详细说明2019-09-27 2896

-

鸿蒙系统内核中CPU空闲时间都在干嘛2021-03-15 2941

-

CPU指令的执行过程 CPU指令流水线2022-05-09 22400

-

证明CPU指令是乱序执行的2023-03-15 1535

-

CPU是怎么实现加速的?2023-04-06 2623

-

secondary cpu执行流程介绍2023-12-05 1879

-

CPU的各种指令和执行流程2025-04-18 2905

全部0条评论

快来发表一下你的评论吧 !