凭借多代 PCIe 打造高效能互连系统

接口/总线/驱动

描述

作者:Diodes 公司资深营销主管 Kay Annamalai

已经从 1.0 版发展到 5.0 版的 PCI Express (PCIe),预计将在 2021 年发表 6.0 版,每个版本都维持向后兼容性,能与过往产品共存。现有规格并未指定失效日期,设备设计人员需要芯片供货商支持每一代产品。

PCI Express 与带宽需求

PCI Express® (PCIe®) 当成一种连接运算、嵌入式及自定义主机处理器,以及以太网络端口、USB 端口、视频卡及储存装置等「终端」周边装置的方式,已经成为高效能互连技术的参考基准。PCIe 利用高速串行通讯技术,提供高效率的点对点连接,还提高信道数量和讯号速率,提供具扩充能力的接口带宽。

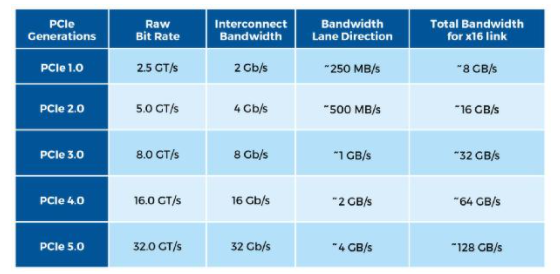

2002 年发布的 PCIe 1.0 规格,运作速度为每秒 2.5 GT/s,提供 8GByte/s 的总 x16 接口带宽。2006 年发布第二代 PCIe 2.0 规格后,带宽成长一倍;2010 年推出的 PCIe 3.0 规格将带宽提高到 32GByte/s,以满足现代各项重要产品应用项目不断成长的需求,包括高阶个人计算机、游戏、企业运算及网络。

近期社群媒体及视讯串流等云端服务迅速普及,对大规模数据中心内的高速连接技术提出更高的全新要求。

如今物联网时代的到来,安装在整个智慧城市及基础设施、智慧工厂和其他工业资产、商业和住宅建筑物,还有用于健身和医疗追踪之穿戴式装置上的连网传感器,将产生海量数据,供超大规模的数据中心撷取、储存、处理与分析。这些力量正在推动对新一代 PCIe 的需求,以高效率的方式将数据中心服务器连接到高速以太网络、网络附加储存装置和人工智能加速器。

联网车将进一步提升数据负载量、增加实时处理的压力,以提高自动驾驶能力水平,最终实现全自驾车的目标。在数据中心的背后,训练神经网络进行人工智能推理作业,要用到极为大量的运算作业,严重暴露出与周边装置进行通讯的瓶颈。

这些因素开始发挥作用,PCIe 该继续向前发展。2017 年发布 PCIe 4.0,不久后在 2019 年发布了 PCIe 5.0。图 1 显示 PCIe 各版本提供的聚合速度。

各大数据中心纷纷舍弃 100Gb 以太网络,改用最新的 400Gb 规格,有望推动广泛采用 PCIe 5.0。在实务上增加 PCIe 带宽一事,或多或少有跟上以太网络速度加快的脚步,最理想的情况是在两种标准之间保持平衡,有助于避免效能方面的瓶颈。

图 1:PCIe 各版本提供的聚合速度 (数据源:Diodes 公司)

如今仍在使用「老旧」的 PCI 标准

PCIe 5.0 产品开始进入市场,加上日前 PCI 特殊兴趣小组 (PCI-SIG) 宣布已展开研发新一代 PCIe 6.0,将于 2021 年完成,在可预见的未来,PCIe 将会是要求高效能周边装置通讯协议的首选。

与此同时,向后兼容性成为 PCIe 系列的一大优势。PCIe 规格没有失效日期,多代产品可以共存于市场,甚至共存于同一个产品应用项目中。这对系统设计人员来说是一项优点:新一代 PCIe 产品不断出现,以满足日益成长的带宽需求,早期产品仍能在众多情景中贡献其价值,像是个人运算装置、游戏及部分企业运算和网络产品应用项目。

解决实行上的挑战

每一代 PCIe 之间的向后兼容性,使得系统能够受益于新芯片推出时更高的传输速度,又无需大幅变更设计。另一方面,提高讯号速度对讯号边限带来额外压力,并可增加设计的复杂性。再者,显然得解决跟 PCIe 桥接的问题,不仅是在老旧界面之间,还有在 USB 或图形端口等其他接口之间。

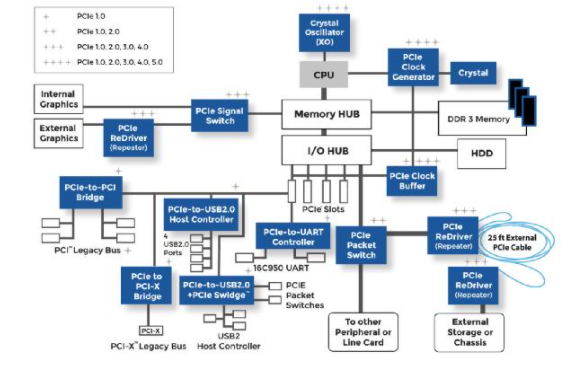

设计人员需要存取支持各代 PCIe 的装置,如图 2 所示的时钟产生器、时钟缓冲器、控制器、封包切换器/网桥、ReDriver™ 芯片及高速多路复用器,以因应这些挑战。

图 2:Diodes 推出之 PCIe 解决方案的范例。(数据源:Diodes 公司)

ReDriver 芯片能够为提高高速系统的讯号完整性,提供一种实惠又便利的解决方案。ReDriver 使用等化及预强化等技术,输出驱动器有着最低延迟性,补偿传输线的损失情况,以恢复讯号边限并将抖动情况降至最低,确保接收器有着低位错误率。与整合包括频率及数据恢复等额外功能的重定时器相比,ReDriver 具备低延迟的特性,且成本较低、易于实行。图 2 显示如何在需要驱动讯号穿过较长 PCB 轨道处使用 PCIe ReDriver 的情况,例如到外部显示适配器或透过缆线到外部储存装置。这些 ReDriver 具有完全向后兼容性,支持所有旧款 PCIe。

网桥与切换器满足各类主机和端点装置之间的接口要求。封包网桥通常会在 OSI 参考模型中的两层之间,或是两个通讯协议之间提供一个接口。图 2 还显示如何使用网桥在 PCIe 与包括 PCI-X 在内的老旧 PCI 标准之间进行连接,或连接到 USB 端口或 UART 总线接口。封包切换器这项多端口/多信道装置,通常用于将单一根复合体扩展到具有多通道的多个端口,以存取周边装置或线路卡等其他对等系统。

除了提供有着多种端口配置及转换功能的封包网桥和切换器,Diodes 公司还结合了 PCIe 封包切换器与 PCIe-to-USB2.0 网桥的功能,打造出 PI7C9X442SL PCI Express-to-USB 2.0「切换网桥」。这种多功能装置可以从一个 PCIe x1 上游端口扇出到两个 x1 下游和四个 USB 2.0 端口,使得系统主机处理器同时存取多个 PCIe 和 USB 装置。

Diodes 公司等企业可以提供多款无源双向 PCIe 1.0、PCIe 2.0 或 PCIe 3.0 讯号多路复用器/解复用器,将单一 PCIe 信道连接到多个信道,为图形或运算作业扩大带宽。也能将这些装置用于从单一多通讯协议接口连接。

时钟缓冲器通常可以将单一参考讯号当成输入,并且产生多个输出,以便更广泛地分布在 PCB 上。时钟缓冲器 IC 有多种配置,Diodes 提供专有的 PLL 设计,确保抖动保持在 PCIe 要求的范围内。时钟产生器可以产生输出抖动极低的特定频率讯号,适用于 PCIe 及其他系统频率。Diodes 的产品组合有 1.8V PI6CG18xxx 和 1.5V PI6CG15xxx PCIe 4.0 时钟产生器及缓冲器,有 2、4 和 8 信道配置,符合各旧款 PCIe 的要求。整合芯片内的端点,这些装置为每个输出省下 4 个外部电阻器,在物料清单中减少多达 32 个组件。

结论

从嵌入式和桌面运算,再到高带宽数据中心联机及神经网络训练等应用项目,PCIe 都是首选的高效能互连技术。设计人员可以利用早期 PCIe 标准一直沿用至今的优点,加上向下兼容新旧不同规格的特性,以具成本效益的方式满足各种系统要求。设计人员使用有着网桥、缓冲器、ReDriver、切换器及多路复用/解复用 IC 等功能的装置组合,高效率地解决产品应用项目的严苛要求。

-

两种高效能电源设计及拓扑分析2011-11-24 2211

-

从 M0 到 M3丨笙泉32 位 MCU:高效能、安全性与多元应用兼具2026-03-10 424

-

高效能石英振荡器的选择2009-10-05 3145

-

安森美高效能LED驱动方案全攻略2012-08-18 2814

-

请问有高效能稳压电源原理图吗?2019-10-16 1644

-

怎样利用热处理去实现高效能LED?2021-04-23 1690

-

求AMD R系列与AMD SOC系列嵌入式高效能解决方案2021-05-10 2111

-

高效能稳压电源原理图2009-05-11 1067

-

符合新兴高效能电源要求的设计2010-01-04 1042

-

Wolfson推出高效能多信道音频方案2010-01-21 1063

-

使用多代 PCIe 构建高性能互连2022-07-21 2700

-

DCAC电源模块:为新能源汽车充电系统提供高效能源转换2024-06-25 2559

-

DS1008JN:精准与高效能的完美结合2024-07-24 1246

-

环旭电子如何解决高效能运算系统挑战2025-02-11 1321

-

Amphenol HD Express®:满足PCIe® Gen 6需求的高性能互连系统2025-12-11 493

全部0条评论

快来发表一下你的评论吧 !