全数字环路滤波器,什么是全数字环路滤波器

半导体器件

122人已加入

描述

全数字环路滤波器,什么是全数字环路滤波器

环路滤波器的性能优劣会直接影响到跟踪环路的性能。而采用数字化的环路滤波器便于调试参数和提高系统可靠性。环路滤波器的输出要直接控制频率合成器产生相应频率,使本地伪码能够准确跟踪发端信息。

基本原理:

数字环中使用的数字环路滤波器与模拟环中使用的环路滤波器作用一样,都对噪声及高频分量起抑制作用,并且控制着环路相位校正的速度与精度。适当选择滤波器的参数,可以改善环路的性能。数字环路滤波器的设计原理是建立在模拟环路滤波器的基础上的。模拟的环路滤波器可以采用RC积分滤波器、无源比例积分滤波器或有源比例积分滤波器等。而数字环路滤波器与其相对应,甚至有参数上的对应关系。

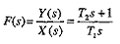

对模拟二阶环路滤波器,其传递函数为:

其中T1, T2为时间常数,决定环路的响应能力。

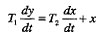

上式的时域表示为:

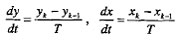

对其进行数字处理:

以上即为二阶数字环路滤波器的数学模型推导,上式可用下图来表示:

如图,即可作为实现数字环路滤波器的算法框图和理论依据。在图中两个参数T2/T1 和T/T1的选择是整个设计的关键,它们的取值将直接影响整个环路的跟踪性能。在设计中,要根据扩频系统的具体指标对两个参数进行调整。

现状和发展

在这里 ,我们只给出这种数字延迟锁定环的设计方案,而系统的参数和技术指标以及数字环路滤波器的FPGA具体实现将不予说明。尽管该方案的实现能够具有精度高和便于调试等特点,但是该方案中也存在模拟延迟锁定环中的一些缺点,如两条支路不能精确对称、电路复杂等。但由于伪码速率高使得全数字方案的实现很困难,随着ASIC技术的飞速发展,这一问题将最终获得解决。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 滤波器

-

环路滤波器参数如何设置?如何设置滤波器的截止频率呢?2023-10-30 2680

-

数字滤波器是什么 数字滤波器的性能指标2023-02-24 6598

-

FIR数字滤波器设计2022-04-05 6512

-

实现三阶环路滤波器的设计方法详细介绍2020-09-17 2025

-

基于芯片测试的外围环路滤波器设计2019-07-05 2873

-

数字低通滤波器的设计2018-01-14 19611

-

一种高频自冷的全数字控制有源电力滤波器_孙运杰2017-01-08 875

-

频率合成器环路滤波器的设计2016-12-16 863

-

基于FPGA的全数字锁相环路的设计2010-09-19 782

-

环路滤波器,什么是环路滤波器2010-03-23 13990

-

用于减小定时抖动的数字预滤波器设计2009-02-22 467

-

数字滤波器的设计实验2008-10-30 6152

-

pll环路滤波器是什么意思2008-04-21 7816

全部0条评论

快来发表一下你的评论吧 !