burn-in有无规范 一般是按什么条件做

描述

Q1:

为啥制造标称值和电路设计推荐值不一样?

Answer:

制造标称值和电路设计推荐值不一致,可以参照下图,“操作空间”在你的问题上可以理解为“制造空间”。

Q2:

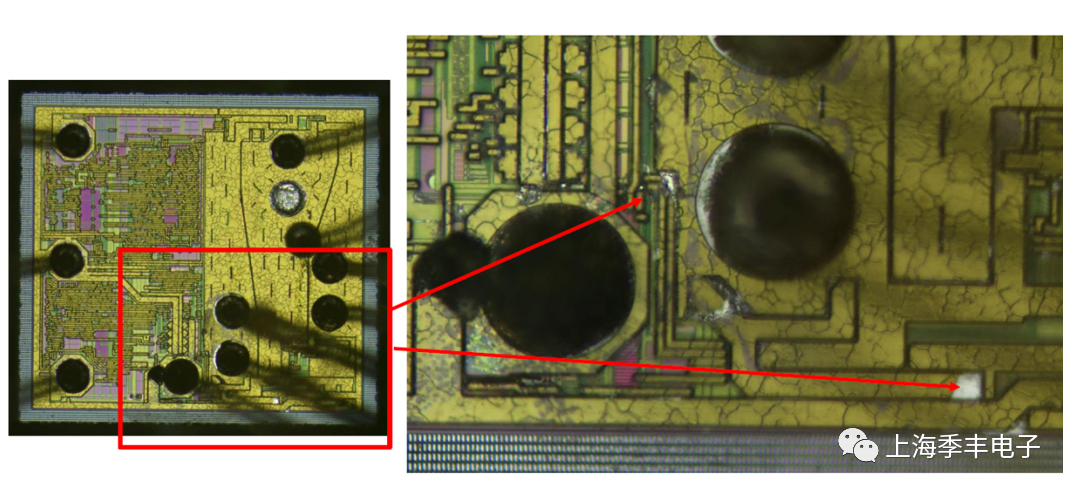

这个图中,引起EOS的原因大概率是什么?EOS会导致打线脱落吗?图中标记的银色部分是烧伤后导致的吗?放大图左边PAD打线的左侧是明显的一个EOS痕迹吗?去层的目的是定位是哪层metal的损伤位置吗,来判定是哪个器件导致了电流过大或者电压过大的损伤?

Answer:

导致EOS的可能原因:过电了,metal层烧伤了。EOS不会打线脱落。可以做下FIB和去层,找出失效点的位置。左边PAD打线的左侧,那个黑点应该是EOS点。

一般不会,剧烈的爆炸是有可能的,当然首先要排除封装的问题。封装问题需要借助SAT 和X-RAY来确认。另外,从图片来看PAD上脱线跟开盖清洗也有一定关系。

Q3:

burn-in有无规范?一般是按什么条件做呢?

Answer:

可以参考MIL-STD-883 METHOD 1015.11 BURN-IN TEST和JESD22-A108。

Q4:

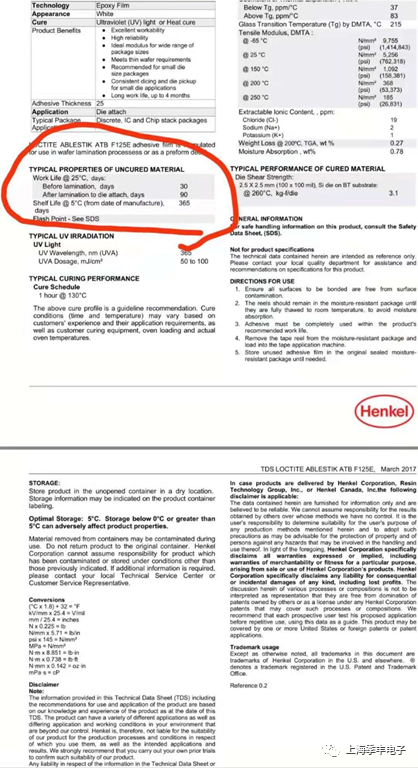

一般的UV膜的在真空包装和氮气柜的lifetime分别是多少?会用什么材料?

Answer:

DAF的life time仅供参考,详细参考下图。这是epoxy film,下面粘的是UV膜。DAF是代替非导电胶,CDAF是代替导电胶的,没有bleed,主要用于叠die或者单芯片尺寸相对基岛比较紧凑,可以使用。

Q5:

WLCSP封装一般推荐哪些可靠性?目前有关于WLCSP可靠性验证相关的行业标准吗?有具体的条件吗?

Answer:

WLCSP最容易出现的两个情况:1、应力把球给蹦掉了;2、球熔在一起短路了。

推荐做:precon, UHAST,HTSL,TC,详细的标准和测试条件见下表。

Q6:

SWIO通讯口管脚损伤,能通过FA分析出来是过压还是静电导致吗?

Answer:

过压和静电都会发生的。可能的原因是:芯片管脚静电保护没做好,而且该管脚容易和外界接触,比如天线,那么就容易被静电打坏。大概率可以通过FA手段判断damage来源。

Q7:

有没有可以看wafer map的软件啊?wafer map txt打开乱码怎么办?

Answer:

UltraEdit好用,方便修改。文件可能不是txt的格式,UE有一个转码功能,把码转一下。要确认下文件用什么编码,如果解码错了就会乱码。

Q8:

多芯片版本芯片 mapping上都是bin1,怎么可以把mapping中某一种芯片改成bin1?

Answer:

上面大佬提及的UltraEdit 就可以改,操作和Excel类似,全部替换即可,但是map里面有map说明等信息,注意要还原回来。

Q9:

CUP的pad打线出现crack,但是os和function测试都ok,能量产出货吗 ?后续会有什么可靠性问题吗?顶层Al厚度1.2um,用了两层metal,按理说pad设计没问题,是封装厂品控不行?

Answer:

肯定不能出货,Crack会随着时间恶化,最终器件早期失效。Pad打线出现的crack是在pad上,需要在pad上看下设计,有一种是底层为铝做衬底,上层用Ti-Ni做导电传导的,这种是可以的,我们做过可靠性,可以等效十年无异常。

Q10:

一般的device和CP测试的prober,对接地是否有特殊的要求。有没有是直接接入办公大楼接地极的,还是需要打独立接地桩进行接地?

Answer:

双线,ESD一根,接地一根,都打桩。

Q11:

很多设备的电源地和机壳地一般都设备内部短接了,这个接一根地线连接外部接地桩;ESD一根地线 是指设备提供作业员插静电手环的孔吗?

Answer:

双线是大多数设备的基本方法,不管是prober还是别的设备,很多设备会有ESD口留着。

Q12:

SAT发现有严重分层,分层的原因可以根据SAT成像分析出来吗?比如是水汽,EOS?

Answer:

一般SAT机台是无法确认delamination形成的缘由的。这个是要后续的FA来界定的。

Q13:

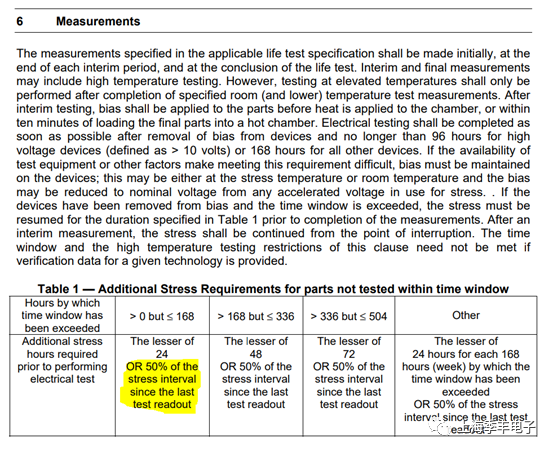

黄色的这部分怎么理解呢?

Answer:

样品停止老化后,没有能够及时测试,那就要重新加应力(温度+电压)一段时间后再测试确认,测试前重新老化的时长参照表1. 第一列中,未及时测试时间小于168小时,则需重新老化24小时或者未完成测试的时间的一半,如耽搁了100小时,那应该再做50小时老化。

Q14:

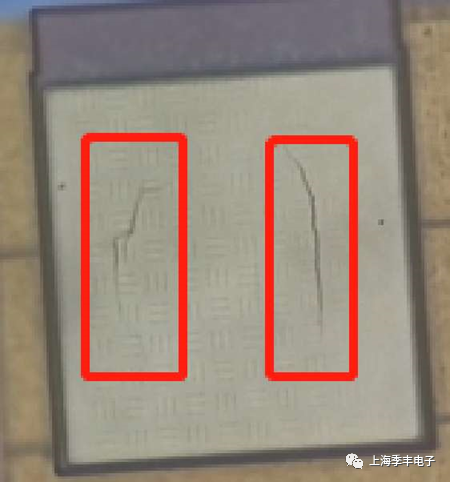

这个图片是Al剥离以后的吧?下面有个标准图。

Answer:

结构上没啥问题,如果是Al层去除后发现的crack,风险很大,想出货的话建议做3x reflow,测试后有管控的出货。如果发生在打线后,也需要看下弹坑,看看下面结构上是不是也有问题,如果弹坑fail,处理方式同上。

引起crack问题很多,从你的图片来看,需要确认测试od,次数及重叠状况,针卡类型及清针方式,打线参数等。这个风险较大,reflow后降级报废最好。另外,3xreflow后还有新的fail,基本上不能用了,还是让封装厂去调参数吧。

Q15:

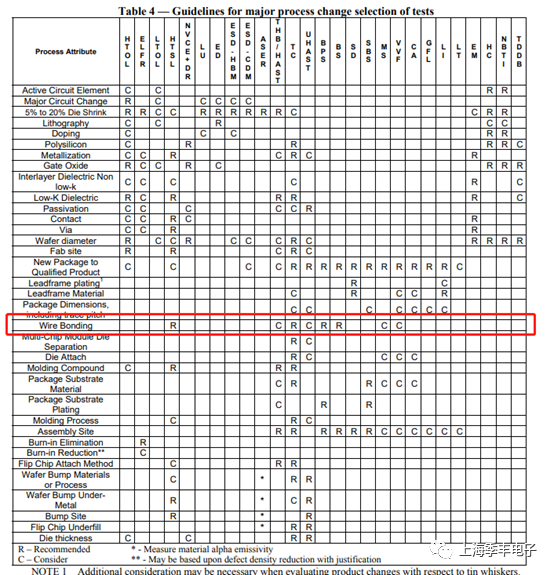

键合丝线材的更换一般需要对芯片做哪些可靠性试验呢?那个键合力的试验BPS需不需要做呢?

Answer:

可靠性试验:TC,HAST, HTS, HTOL, PCT。另外,键合力的试验BPS也需要做。具体实验可参考下图。

Q16:

芯片上SMT前如果开封时间长的话要进行烘干,请问做烘干是为了去除芯片外表面的水汽还是为了去除芯片内部的水汽,内部的水汽可以通过烘干去除吗?

Answer:

通常对新封装类型是需要通过soaking/drying实验来得到准确的baking condition: 取一定数量的fail 芯片先做soaking充分吸潮同时定期称重量,至到吸潮饱和,芯片总重量不再增加;然后再对这些芯片在某一高温下做烘烤,定期称重量直到重量不会再减少。画出芯片重量随时间的变化曲线,就能定下来baking condition。

可以将烘烤的实验,想象成一个水果,如果被烘成水果干,是不是内部和外部的水汽都被烘干。也可以找OSAT要一次这类package的baking推荐温度/时间条件。芯片内部的水汽,应该主要是导电胶吸湿吧,DB烘烤125度2H就够了。

Q17:

我们有时发现热点在某个电阻部位,但设计公司认为是同一回路上其它地方器件损坏,而不是该电阻损坏。一般分析发现热点的地方就一定是器件损坏的地方吗?

Answer:

不一定。看你用的什么定位设备,OBIRCH和THERMOS的话,热点和缺陷位置重合的概率高,尤其是Thermos。用EMMI的话,很多时候热点和失效位置不重合,有时候还有假hotspots, 需要做layout tracing分析电路来进一步定位。

Q18:

55nm LOW-K工艺一定要用激光划片吗?激光划片成本比刀具划片成本一般会高出多少?

Answer:

Low k建议用激光开槽,否则chipping会很严重。成本增加主要是激光保护液增加的成本,具体看chip size即划片道长度。或者可以直接blade saw,但是为了减少crack,需要feeding特别慢,不适合量产。

Q19:

一般哪些产品需要做EMC,MCU是否需要做这项?做MCU消费类应用需要达到什么等级,有什么标准可以参考?

Answer:

基本所有的电子产品都要做EMC,国内的CCC,欧洲的CE,美国的FCC,澳洲的RCM都要做的。还有车规也要做EMC,季丰有条件自己做车规EMC。

编辑:jq

-

IC测试座/老化座(IC Test & Burn-In sockets)2009-08-10 7361

-

ic验证 检测 失效分析芯片Burn-in Socket、Test Socket 老化座2016-12-02 10871

-

小弟第一次做板子,请问大家一般在哪做,一般多少钱2017-02-27 5968

-

VNA规范一般问题理解2019-07-24 1704

-

PCB焊盘与孔径设计一般规范(仅参考)2023-06-09 3120

-

电机在一般环境条件下使用的湿热试验要求GB 12665902008-09-14 694

-

生鲜商品品质管理的一般规范2010-02-02 1398

-

Agilent Burn-in Testing Techni2010-07-29 599

-

电池一般材料有哪些?2009-10-21 4590

-

Power Burn2009-12-26 820

-

传感器的一般要求2010-05-24 2705

-

一般基板总体设计布局规范资料免费下载2019-05-13 944

-

MOS管当开关控制时为什么一般用PMOS做上管NMOS做下管2020-12-11 3302

-

为什么PCB设计一般为50欧姆阻抗?2023-07-03 2308

-

Burn-In测试你又明白多少呢?2024-01-12 13271

全部0条评论

快来发表一下你的评论吧 !