FPGA的硬件架构和工作原理

描述

一、FPGA的硬件架构和工作原理

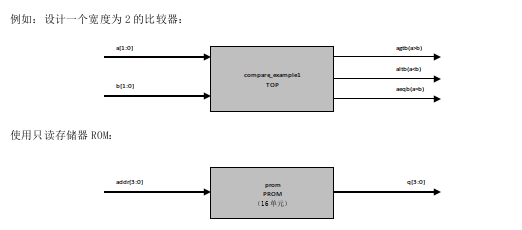

1.1早期的PROM技术实现

在上世纪60年代以后,小规模集成电路出现,需要实现一个组合逻辑的方法,是一种基于PROM(Programable ROM Based)的技术,其原理是将组合电路的真值表写入ROM中,用PROM设备实现定制逻辑的真值表,等效于实现定制逻辑。

这里控制信号从略 。

首先,将比较器的真值表填写:

| 索引号 | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

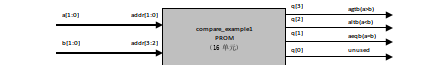

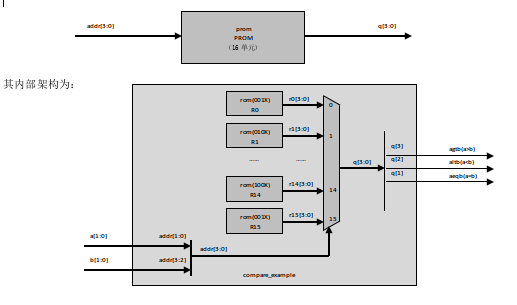

将真值表写入PROM中,使用PROM设备实现比较器:

等效的实现定制逻辑。

为了进一步了解PROM技术的本质,需要知道ROM设备的架构和原理:

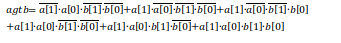

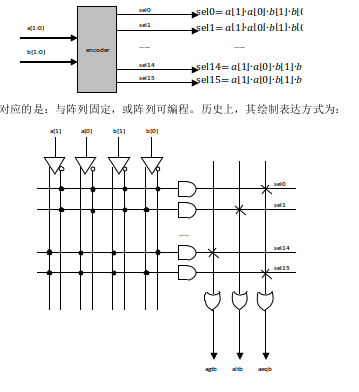

1.2基于PROM技术的SOP(积之和最小项)

数字电路中,将真值表用逻辑门实现的常用方法为SOP(Sum Of Products):

| 索引号 | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

PROM设备中,多路器的选择信号对应地址的译码逻辑

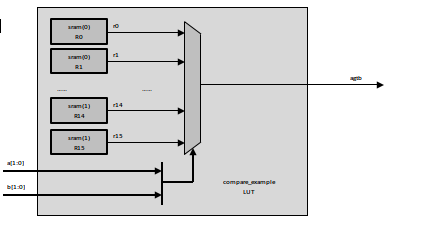

1.3基于查找表技术的定制逻辑

上世纪80年代,CPLD的出现,以及之后的FPGA,为了解决输入端和存储单元的2的n次方问题,出现了查找表LUT技术。查找表LUT其原理同样是用固定的(硬核)多路器,基于SRAM技术,实现定制逻辑的真值表,从而等效的实现定制逻辑。其中一个重要的变化,是将真值表项写入SRAM(静态存储器)中,而不是用反溶丝技术(OTP),从而实现在线编程(沿用至今)。同样用上面的二输入比较器为例:

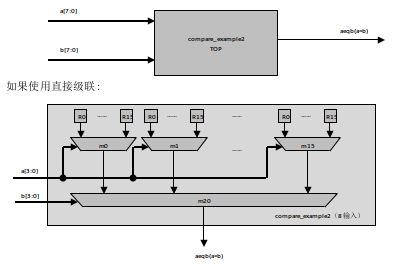

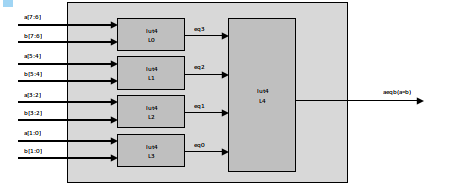

以上例子中,所需要的存储器单元仍然是16个单元,为2的4次方。为了清楚LUT的减输入法过程,我们将输入端增加到16(与或阵列,需要65536单元):

这里使用的存储器为:16*16=65536。并没有解决存储器数量增加的问题。但使用四输入LUT的实际架构(含减输入法)为:

这里,仅仅使用了5*16=80个存储器单元。

1.4在线编程技术

CPLD出现之前,PLD设备大多采用反熔丝技术(Anti-Fuse),交叉编程位置在编程前为高阻抗,编程后为很低的阻抗,为导通态。反熔丝技术为一次性编程(OTP),实际使用并不方便,但其好处是便于保护知识产权。在LUT技术出现以后,设计者的定制逻辑真值表和整个设计的网表(含路由),是写入静态存储器SRAM中,具有速度快,支持在线编程(可反复擦除),但其缺点是挥发性(掉电即失),FPGA每次上电以后,需要重新装入(有一个比较复杂的配置过程)。

责任编辑:haq

-

fpga的工作原理2008-05-20 9334

-

xilinx_fpga结构及工作原理介绍2012-08-02 6132

-

例说FPGA连载15:硬件整体架构设计2016-08-01 4408

-

【实例】FPGA硬件基础篇:FPGA硬件架构及原理2021-04-01 1177

-

FPGA的基础知识点及工作原理是什么2021-04-30 1414

-

Gnutella文件共享体系架构的工作原理2009-07-30 3635

-

FPGA,FPGA工作原理是什么?2010-03-26 4006

-

FPGA的工作原理及其基本特点2012-05-12 3533

-

MCS-51单片机的硬件结构与工作原理2017-06-21 2190

-

CC2640R2F的架构及工作原理2018-08-23 9864

-

FPGA工作流和程架构框图资料免费下载2020-04-13 951

-

GPU和FPGA的工作原理及其区别2023-08-06 3303

-

fpga芯片工作原理 fpga芯片有哪些型号2024-03-14 3025

-

FPGA芯片的工作原理和使用2024-03-27 2107

-

ADC的五大架构及其工作原理2025-04-03 3546

全部0条评论

快来发表一下你的评论吧 !