可编程逻辑器件随着半导体集成电路的4个阶段

电子说

描述

发展历史

可编程逻辑器件伴随着半导体集成电路的发展而不断发展,其发展可以划分为以下4个阶段:

1.第一阶段

20世纪70年代,可编程器件只有简单的可编程只读存储器(PROM)、紫外线可擦除只读存储器(EPROM)和电可擦除只读存储器(EEPROM)3种,由于结构的限制,它们只能完成简单的数字逻辑功能。

2.第二阶段

20世纪80年代,出现了结构上稍微复杂的可编程阵列逻辑(PAL)和通用阵列逻辑(GAL)器件,正式被称为PLD,它们能够完成各种逻辑运算功能。典型的PLD由“与”、“非”阵列组成,用“与或”表达式来实现任意组合逻辑,所以PLD能以乘积和形式完成大量的逻辑组合。PAL器件只能实现可编程,在编程以后无法修改;如需要修改,则需要更换新的PAL器件。但GAL器件不需要进行更换,只要在原器件上再次编程即可。

3.第三阶段

20世纪90年代,众多可编程逻辑器件厂商推出了与标准门阵列类似的FPGA和类似于PAL结构的扩展性CPLD提高了逻辑运算的速度,具有体系结构和逻辑单元灵活、集成度高和适用着围宽等特点,兼容了PLD和通用门阵列的优点,能够实现超太规模的电路,编程方式也很灵活,成为产品原型设计和中小规模(一般小于10000)产品生产的首选。

4.第四阶段

21世纪初,现场可编程门阵列和CPU相融合,并且集成到了单个的FPGA器件中。典型的,Xilinx推岀了两种基于FPGA的嵌人式解决方案:

(1)FPGA器件内嵌了时钟频率高达500MHz的PowerPC硬核微处理器和1GHZ的ARM Cortex-A9双核硬核嵌入式处理器。

(2)提供了低成本的嵌入式软核处理器,如:MicroBlaze、PicoBlaze。

通过这些嵌人式解决方案,实现了软件需求和硬件设计的完美结合,使FPGA的应用范围从数字逻辑扩展到了嵌人式系统领域。

可编程逻辑器件工艺

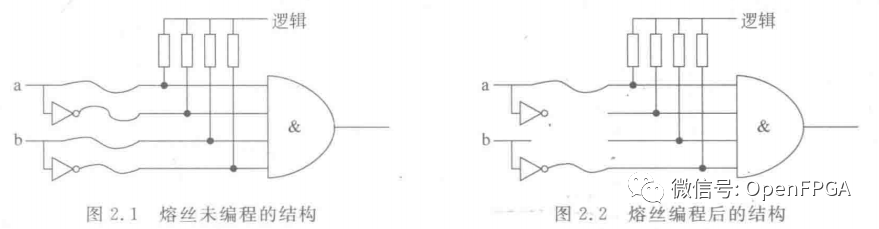

1.熔丝连接工艺

最早允许对器件进行编程的技术是熔丝连接技术。在釆用这种技术的器件中,所有逻辑靠熔丝连接。熔丝器件只可编程一次,一旦编程,永久不能改变。

熔丝的编程原理如图2.1所示。进行编程时,需要将熔丝烧断;编程完成后,相应的熔丝被烧断,如图2.2所示。

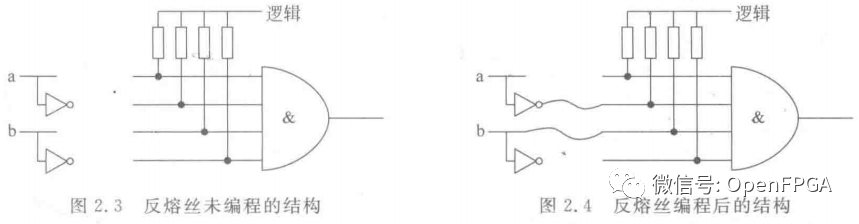

2.反熔丝连接工艺

反熔丝技术和熔丝技术相反,在未编程时,熔丝没有连接;编程后,熔丝将和逻辑单元连接。反熔丝开始是连接两个金属的微型非晶硅柱,未编程时,呈高阻状态;编程结束后,形成连接。反熔丝器件只可编程一次,一旦编程,永久不能改变。

反熔丝的编程原理如图2.3所示。进行编程时,需要将熔丝连接;编程完成后,相应的熔丝被连接,如图2.4所示。

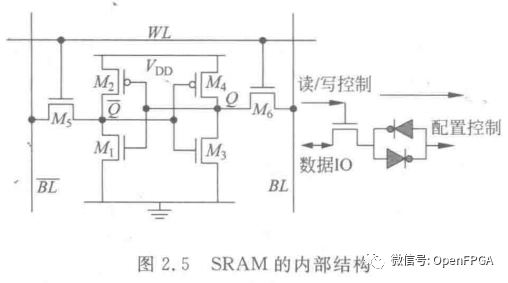

3.SRAM工艺

SRAM的结构如图2.5所示。基于静态存储器SRAM的可编程器件,值被保存在SRAM中时,只要系统正常供电,信息就不会丢失,否则信息将丢失。SRAM存储数据需要消耗大量的硅面积,且断电后数据丢失,但是这种器件可以反复地编程和修改。

绝大多数的FPGA都采用这种工艺,这就是FPGA外部都需要有一个PROM芯片来保存设计代码的原因。

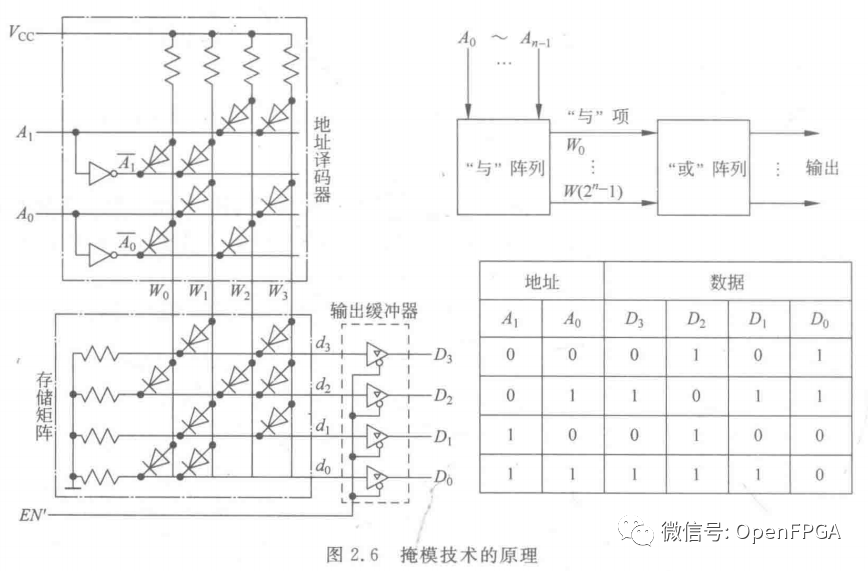

4.掩膜工艺

ROM是非易失性的器件,系统断电后,将信息保留在存储单元中。掩膜器件可以读出信息,但是不能写入信息。ROM单元保存了行粕列数据,形成一个阵列,每一列有负载电阻使其保持逻辑1,每个行列的交叉有一个关联晶体管和一个掩膜连接,如图2.6所示。

注:这种技术代价比较高,基本上很少使用。

下面对其工作原理进行推导,以帮助读者理解上图所实现的功能。

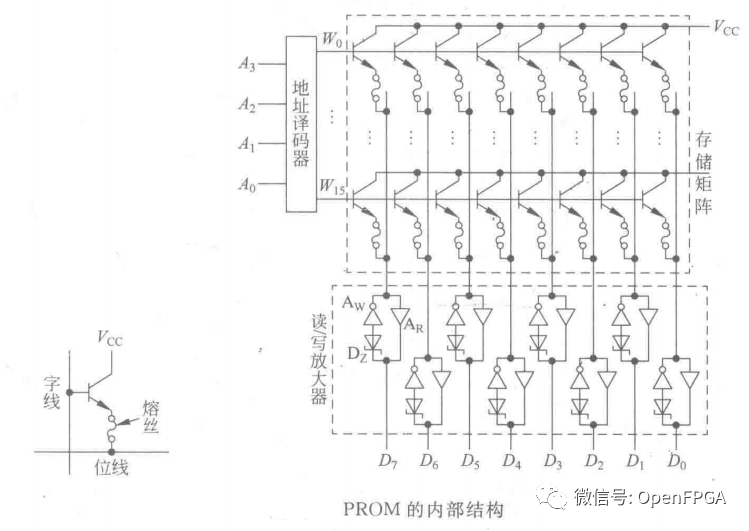

PROM工艺

PROM是非易失性器件,系统断电后,信息被保留在存储单元中。PROM器件可以编程一次,以后只能读数据而不能写入新的数据。PROM单元保存了行和列数据,形成一个阵列,每一列有负载电阻使其保持逻辑1,每个行列的交叉有一个关联晶体管和一个掩模连接,如下图所示。

如果可以多次编程,就称为EPROM和EEPROM技术。

6.FLASH工艺

釆用FLASH技术的芯片的擦除速度比采用PROM技术的芯片要快得多。FLASH技术可采用多种结构,与EPROM单元类似,具有一个浮置栅晶体管单元和EEPROM器件的薄氧化层特性。

编辑:hfy

-

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介2024-03-28 1782

-

可编程逻辑器件2014-04-15 3674

-

可编程逻辑器件和ASIC,两者有什么不同区别?2021-07-13 5070

-

PLD可编程逻辑器件2021-07-22 2319

-

FPGA零基础学习:半导体存储器和可编程逻辑器件简介2023-02-23 1244

-

可编程逻辑器件基础及应用实验指导书2010-03-24 784

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1162

-

可编程逻辑器件(书皮)2022-07-10 782

-

可编程逻辑器件向什么目标前进2019-11-21 991

-

什么是可编程逻辑器件2020-06-04 10399

-

可编程逻辑器件和ASIC对比介绍2020-09-04 3420

-

基于可编程逻辑器件和VHDL语言实现算术逻辑单元的设计2021-01-04 2748

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4568

-

可编程逻辑器件的特征及优势科普2024-02-26 2156

全部0条评论

快来发表一下你的评论吧 !