向量扩展将定稿,RISC-V机器学习的崛起

描述

向量扩展将定稿,RISC-V机器学习的崛起

RISC-V作为一个与x86和Arm相比仍算年轻的架构,自然需要不少扩展模块来完善其指令集架构,尤其是对标x86与Arm的SIMD指令集。然而SIMD指令集随着时间的发展变得越来越臃肿,让架构变得愈发复杂,David Patterson也在几年前的一篇文章中写道,实现数据级并行性更优雅的方式就是向量架构,RISC-V的向量扩展(RVV)也应运而生。

在机器学习算法中,向量被广泛用于处理数据集和数组。而RVV为基础指令集新增了多个向量寄存器和向量指令,可以让基于RISC-V架构的处理器核心处理数组,与传统的标量运算一起来加速大数据集的指令运算。

RISC-V向量扩展指令于2018年推出,在经过了多个版本的迭代后,终于在几天前进入了1.0 PB状态。RVV工作组认同了1.0版本的稳定性,已经可以在上游软件项目中开发相关的工具链、功能模拟器与实现了。而前段时间的RISC-V论坛,也展示了RISC-V在向量与机器学习上的进展。

RISC-V机器学习用于太空应用

相信不少人都注意到近期逐渐增加的各项太空探索任务,比如祝融号火星车与中国空间站建设等,这些任务中AI与机器学习的应用也开始出现。然而将AI与机器学习加入太空任务依旧面临着诸多挑战,比如已有的太空处理器已经无法跟上AI与ML的计算需求,但现成的商用设备既无法满足辐射要求,也没有太空认证的软件栈支持。

来自加泰罗尼亚理工大学和巴塞罗那超算中心的两位研究员Leonidas Kosmidis和Marc Solé Bonet给出了他们的创新方案,实现了在功率有限的RISC-V处理器上加速ML运算。与采用额外大面积向量寄存器文件的传统方式不同,他们采用了一个开源的短SIMD模块通过重复利用整数寄存器文件来减小面积。这一方案以2个未使用的RISC-V操作码实现了17个高度可配置的定制指令,可以用于实现ML应用中200多种组合运算。

他们成功将该模块移植到了Cobham Gaisler开发的开源RISC-V太空处理器NOEL-V上,在最小的NOEL-V处理器的配置下进行通用ML程序的测试,得出的结果相当可观。只需多用到25%的面积,就能实现3到7倍的性能提升,还不会影响到处理器的频率。

两位研究员也实现了Gaisler另一个太空处理器LEON3的版本,该处理器采用的是SPARC V8的架构。未来他们还计划引入TensorFlow和编译器代码生成等一系列软件支持,并在欧洲航天局OPS-SAT实验卫星上的FPGA上进行测试。

RISC-V向量处理器的真正挑战

90年代可以说是DSP、CISC与DSP三家争霸的状态,然而到了21世纪,DSP已经越来越难突破GHz,而高频CPU中乘积累加运算单元的流行使得DSP在性能上败下阵来。而RISC与CISC相比的优势在于其简单化的特性,更容易实现高频率。然而在向量处理器(VPU)上,必须要解决数据传输的问题。

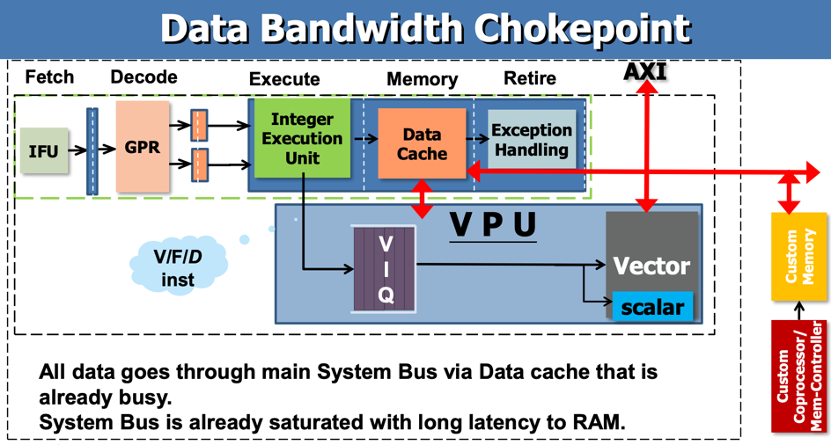

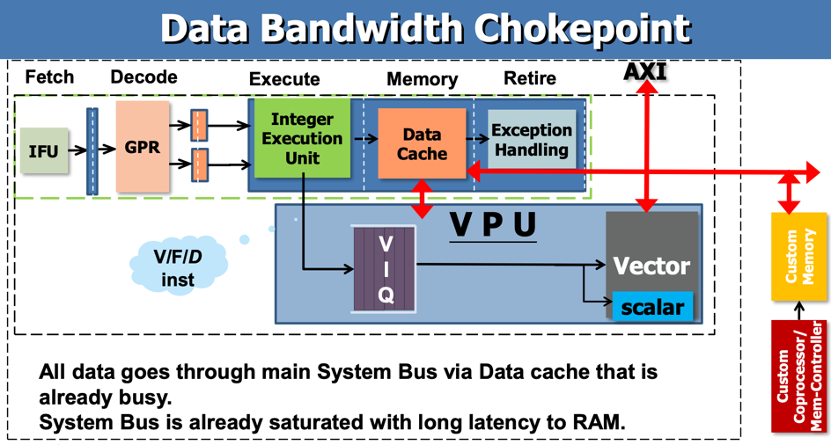

传统VPU在带宽上的瓶颈 / 晶心科技

从数据传输的流程来看,系统总线已经被处理器占用处于繁忙状态,而所有数据都通过缓存走向总线,现在又多出了向量指令和向量数据,致使总线到内存的延迟增加,整体性能下降。因此,提高总线带宽的同时保持高频率,又不会增加额外的功耗也就成了一大设计挑战。传统的解决方案有预读取和更大的独立内存与缓存等,但往往需要牺牲功耗和尺寸。

晶心科技为了解决这一挑战,推出了晶心自定义扩展(Andes Custom Extension,ACE),这一RISC-V扩展可以创造新的指令、新的协处理器和新的内存位置。ACE引入了全新的Streaming Port,为外部硬件引擎创造了自定义数据接口和自定义数据内存,以很小的功率代价解决了数据传输问题。除此之外,ACE还可以用于数据预处理与后处理,比如格式转换等,进一步提升VPU的性能,更好地控制和管理外部加速器。

结语

RISC-V在向量扩展与处理器上的进展已经相当惊人,要知道苹果在前段时间招募RISC-V开发者的工作描述中,不仅要求掌握RISC-V的开发知识,还要求了解Arm NEON SIMD微架构的向量编程。随着RVV的定稿,向量寄存器与指令也将全部确定下来,届时相关的编译器等工具链也能够及时做到兼容。

打开APP阅读更多精彩内容

RISC-V作为一个与x86和Arm相比仍算年轻的架构,自然需要不少扩展模块来完善其指令集架构,尤其是对标x86与Arm的SIMD指令集。然而SIMD指令集随着时间的发展变得越来越臃肿,让架构变得愈发复杂,David Patterson也在几年前的一篇文章中写道,实现数据级并行性更优雅的方式就是向量架构,RISC-V的向量扩展(RVV)也应运而生。

在机器学习算法中,向量被广泛用于处理数据集和数组。而RVV为基础指令集新增了多个向量寄存器和向量指令,可以让基于RISC-V架构的处理器核心处理数组,与传统的标量运算一起来加速大数据集的指令运算。

RISC-V向量扩展指令于2018年推出,在经过了多个版本的迭代后,终于在几天前进入了1.0 PB状态。RVV工作组认同了1.0版本的稳定性,已经可以在上游软件项目中开发相关的工具链、功能模拟器与实现了。而前段时间的RISC-V论坛,也展示了RISC-V在向量与机器学习上的进展。

RISC-V机器学习用于太空应用

相信不少人都注意到近期逐渐增加的各项太空探索任务,比如祝融号火星车与中国空间站建设等,这些任务中AI与机器学习的应用也开始出现。然而将AI与机器学习加入太空任务依旧面临着诸多挑战,比如已有的太空处理器已经无法跟上AI与ML的计算需求,但现成的商用设备既无法满足辐射要求,也没有太空认证的软件栈支持。

来自加泰罗尼亚理工大学和巴塞罗那超算中心的两位研究员Leonidas Kosmidis和Marc Solé Bonet给出了他们的创新方案,实现了在功率有限的RISC-V处理器上加速ML运算。与采用额外大面积向量寄存器文件的传统方式不同,他们采用了一个开源的短SIMD模块通过重复利用整数寄存器文件来减小面积。这一方案以2个未使用的RISC-V操作码实现了17个高度可配置的定制指令,可以用于实现ML应用中200多种组合运算。

他们成功将该模块移植到了Cobham Gaisler开发的开源RISC-V太空处理器NOEL-V上,在最小的NOEL-V处理器的配置下进行通用ML程序的测试,得出的结果相当可观。只需多用到25%的面积,就能实现3到7倍的性能提升,还不会影响到处理器的频率。

两位研究员也实现了Gaisler另一个太空处理器LEON3的版本,该处理器采用的是SPARC V8的架构。未来他们还计划引入TensorFlow和编译器代码生成等一系列软件支持,并在欧洲航天局OPS-SAT实验卫星上的FPGA上进行测试。

RISC-V向量处理器的真正挑战

90年代可以说是DSP、CISC与DSP三家争霸的状态,然而到了21世纪,DSP已经越来越难突破GHz,而高频CPU中乘积累加运算单元的流行使得DSP在性能上败下阵来。而RISC与CISC相比的优势在于其简单化的特性,更容易实现高频率。然而在向量处理器(VPU)上,必须要解决数据传输的问题。

传统VPU在带宽上的瓶颈 / 晶心科技

从数据传输的流程来看,系统总线已经被处理器占用处于繁忙状态,而所有数据都通过缓存走向总线,现在又多出了向量指令和向量数据,致使总线到内存的延迟增加,整体性能下降。因此,提高总线带宽的同时保持高频率,又不会增加额外的功耗也就成了一大设计挑战。传统的解决方案有预读取和更大的独立内存与缓存等,但往往需要牺牲功耗和尺寸。

晶心科技为了解决这一挑战,推出了晶心自定义扩展(Andes Custom Extension,ACE),这一RISC-V扩展可以创造新的指令、新的协处理器和新的内存位置。ACE引入了全新的Streaming Port,为外部硬件引擎创造了自定义数据接口和自定义数据内存,以很小的功率代价解决了数据传输问题。除此之外,ACE还可以用于数据预处理与后处理,比如格式转换等,进一步提升VPU的性能,更好地控制和管理外部加速器。

结语

RISC-V在向量扩展与处理器上的进展已经相当惊人,要知道苹果在前段时间招募RISC-V开发者的工作描述中,不仅要求掌握RISC-V的开发知识,还要求了解Arm NEON SIMD微架构的向量编程。随着RVV的定稿,向量寄存器与指令也将全部确定下来,届时相关的编译器等工具链也能够及时做到兼容。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

risc-v的发展历史2024-07-29 1649

-

RISC-V如何支持不同的AI和机器学习框架和库?2024-10-10 8682

-

关于RISC-V学习路线图推荐2024-11-30 1845

-

关于RISC-V芯片的应用学习总结2025-01-29 1864

-

RISC-V B扩展介绍及实现2025-10-21 717

-

探索RISC-V在机器人领域的潜力2025-12-03 958

-

RISC-V是什么2021-07-23 2254

-

RISC-V的相关资料分享2022-02-11 1550

-

RISC-V 发展2023-04-14 1071

-

晶心科技推出突破性的RISC-V 27系列处理器及向量扩展指令处理器2020-01-03 3706

-

晶心科技RISC-V向量处理器NX27V升级至RVV 1.02021-04-12 3416

-

向量扩展将定稿 RISC-V机器学习的崛起2021-10-08 2533

-

RISC-V批准的新规范意味着什么?2021-12-07 3784

-

RISC-V学习笔记【1】RISC-V概述2022-11-24 3432

-

RISC-V架构下的编译器自动向量化2025-06-06 1439

全部0条评论

快来发表一下你的评论吧 !