基于RGMII+phy的典型应用快速入门

电子说

描述

Zynq&ZU+ Mpsoc的以太网使用普遍,从功能大致分为2类应用:调试管理、数据传输。本文主要集中在PS端的Ethernet RGMII外接phy设计和调试,该部分客户用的最多也最容易出问题,希望通过本文对基于RGMII+phy的典型应用快速入门,解决问题。

1. 以太网接口介绍

以太网接口包含管理、数据通信接口,管理接口也就是我们常说的MDC/MDIO,用来访问phy寄存器,配置工作模式、检测工作状态。数据接口:常见的有MII, GMII, RGMII,SGMII, QSGMII等,我们本次专注在RGMII。

2. MDC/MDIO接口

帧格式: CL22(GE), CL45(XE); Phy地址: 访问外部哪颗phy; MDC clock频率: 不超过2.5 MHz (defined by the IEEE802.3);

|

Preamble (32bits) |

Start (2bits) |

OP Code (2bits) |

PHYAD (5bits) |

REGAD (5bits) |

Turn Around (2bits) |

Data (16bits) |

Idle | |

| Read | 1.......1 | 01 | 10 | A4A3A2A1A0 | R4R3R2R1R0 | Z0 | D15.......D0 | Z* |

| Write | 1.......1 | 01 | 01 | A4A3A2A1A0 | R4R3R2R1R0 | 10 | D15.......D0 | Z* |

硬件设计Tips:MDIO为OD门,需1.5K电阻上拉。

3. RGMII接口

硬件设计Tips:RGMII规范中约定data和clock之间需要有2ns延迟,实现方式:

A. PCB板上绕线实现 (不推荐);

B. PCB(data/clock等长处理)+PHY芯片上分别设置TX/RX delay(现在phy基本上均支持,使用前请查看phy手册确认);

4. 软件开发Tips

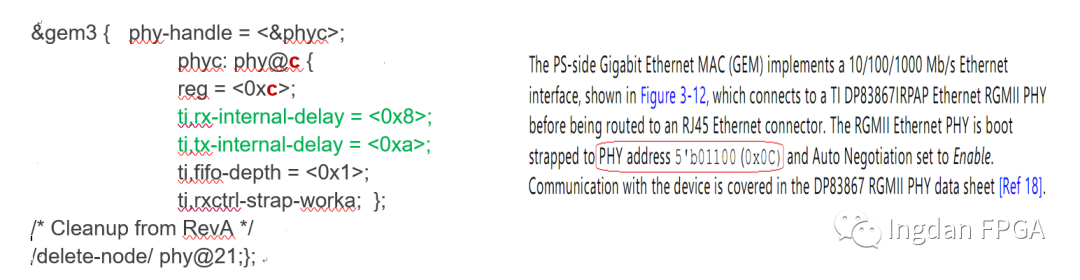

Linux如何配置phy地址&phy delay,以ZCU102为例,GEM3 phy address=0xC,采用phy internal tx/rx delay,在设备树system-usr.dsti中添加phy地址和delay(有的phy硬件配置好,无需额外添加)。

5. 调试Tips

在uboot下通过mii命令查看phy的link/AN/Speed状态,或者配置loopback测试。

常用命令有mii info、mii dump、miiwrite等等。

通过mii info可以查看MDC/MDIO总线下挂载了哪些phy address。ZynqMP> mii infoPHY0x07: OUI = 0x5043, Model = 0x21, Rev = 0x00, 1000baseX, FDX PHY0x0C: OUI = 0x5043, Model = 0x21, Rev = 0x00, 1000baseX, FDX ZynqMP> ZynqMP>mii device MIIdevices: 'eth0' Currentdevice: 'eth0' 通过mii dump可以查看phy的状态,可读性好。ZynqMP>mii dump 7 0 0. (1140) -- PHY control register --

(8000:0000) 0.15 = 0 reset

(4000:0000) 0.14 = 0 loopback (2040:0040) 0. 6,13 = b10 speed selection = 1000 Mbps (1000:1000) 0.12 = 1 A/N enable (0800:0000) 0.11 = 0 power-down (0400:0000) 0.10 = 0 isolate (0200:0000) 0. 9 = 0 restart A/N (0100:0100) 0. 8 = 1 duplex = full (0080:0000) 0. 7 = 0 collision test enable (003f:0000) 0. 5- 0 = 0 (reserved)

6. 常见问题及解决方法

Q1:PHY无法访问? A1:查看原理图MDIO是否有上拉、phy address是否正确、降低MDC clock测试。 Q2:能link但是ping不通? A2:PC防火墙是否关闭,包含windows自带的防火墙?设备ip和pcip地址是否配置正确?如果以上均已操作正确,重点检查RGMII PHY的TX/RX delay配置。 责任编辑:haq

-

请问DP83822IRHB该PHY要配成RGMII时,到底还需要哪些配置?2024-12-16 633

-

通过磁珠解决RGMII延时不够案例2024-01-05 5402

-

RGMII接口案例:二个设备共享一个PHY2023-11-27 10283

-

FPGA 控制 RGMII 接口 PHY芯片基础2023-06-06 2003

-

LS1046A RGMII MAC转MAC,无法成功链接是怎么回事?2023-06-01 1183

-

RK3288 RGMII如何连接百兆PHY DP83822?2022-03-03 1744

-

SGMII网络与RGMII网络不能独立启动工作吗2022-01-05 1793

-

典型的PHY包括哪些2021-08-05 853

-

GMII和RGMII主要的接口2021-07-29 2256

-

FPGA控制RGMII接口PHY芯片88E1512网络通信2020-10-15 26328

-

RGMII接口信号和帧格式_RGMII接口应用框图2020-09-30 33528

-

Xilinx的RGMII 的PHY层逻辑设计详解2018-07-02 17644

-

RGMII总线上挂两片PHY是否可行2012-04-25 5081

全部0条评论

快来发表一下你的评论吧 !