模拟锁相环NE564在FM解调电路中的应用

通信设计应用

描述

模拟锁相环NE564在FM解调电路中的应用

摘要:介绍了锁相鉴频电路的工作原理和模拟锁相环芯片NE564的结构与特点,并用该芯片设计了一款41.4MHz的FM解调电路,具有较强的实用性。

0 引言

调频波(FM)解调称为频率检波,简称鉴频。实现调频波解调的方法有很多,常见的方法有:a.斜率鉴频、相位鉴频、比例鉴频,这些鉴频器电路需要大量的电阻电容等元件,电路形式比较复杂不易于集成;b.移相乘积鉴频、脉冲均值鉴频,这些鉴频器易于集成,但移相乘积鉴频器内部噪声较大,脉冲均值鉴频器线性好、频带宽,但中心频率范围较低;c.锁相环鉴频,它是利用现代锁相技术来实现鉴频的方法,具有工作稳定、失真小、信噪比高等优点,所以被广泛应用在通信电路系统中。

1 锁相鉴频器的工作原理

锁相鉴频器原理框图如图1所示。当输入为调频波时,如果环路滤波器的带宽足够宽,使鉴相器的输出电压可以顺利通过,则VCO(压控振荡器)就能跟踪输入调频波中反映调制规律变化的瞬时频率,即VCO的输出就是一个具有相同调制规律的调频波。这时环路滤波器输出的控制电压就是所需的调频波解调电压。模拟锁相环NE564芯片就可用来设计FM解调电路。

2 模拟锁相环NE564的结构与特点

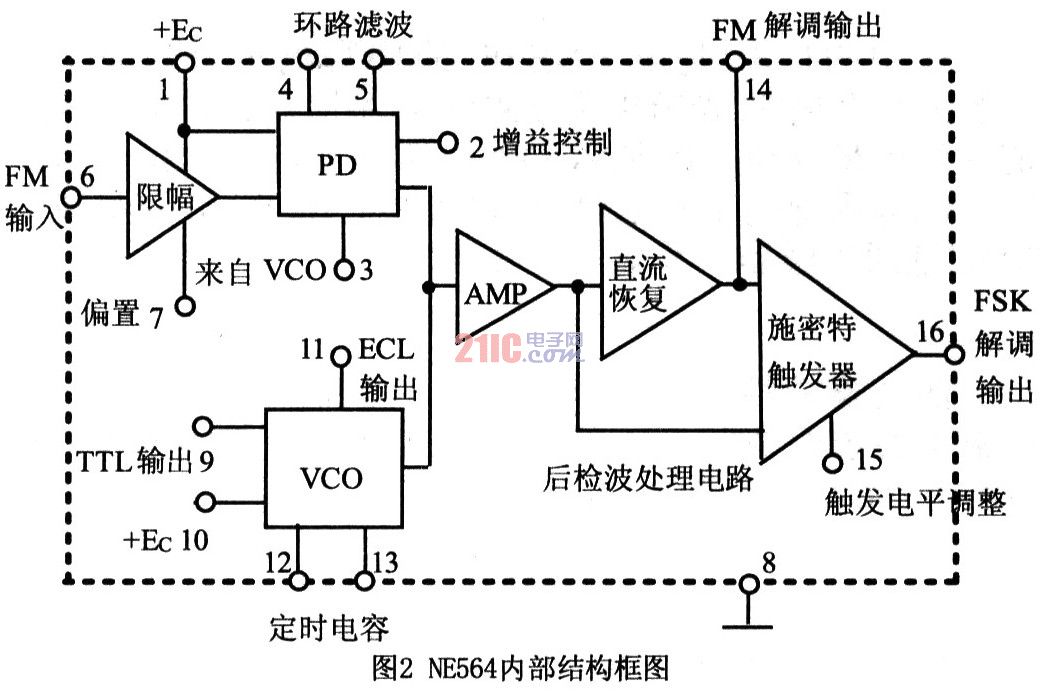

模拟锁相环SE564芯片的最高工作频率可达50MHz,采用+5V单电源供电,电路设计所使用的元件不多,关键步骤是设置中心频率和如何滤波两个方面。特别适用于高速数字通信中FM信号和FSK(移频键控)信号的调制和解调,且不需外接复杂的滤波器。芯片采用双极性工艺,电路由限幅器、鉴相器、压控振荡器、放大器、直流恢复电路和施密特触发器等六部分组成,内部结构如图2所示。

图2中,限幅器由差分电路组成,可抑制FM信号的寄生调幅;鉴相器(PD)的内部含有限幅放大器,以提高对AM信号的抗干扰能力:4、5脚外接电容组成环路滤波器,用来滤除比较器输出的直流误差电压中的纹波;2脚用来改变环路的增益;3脚为VCO的反馈输入端;VCO是改进型的射极耦合多谐振荡器,有两个电压输出端,9脚输出TTL电平,11脚输出ECL电平。VCO内部接有固定电阻,只需外接一个定时电容就可产生振荡;施密特触发器的回差电压可通过15脚外接直流电压进行调整, 以消除16脚输出信号的相位抖动。SE564的封装图如图3所示。

3 FM解调电路设计

用NE564组成41.4MHz的FM电路,如图4所示。FM输入信号的电压Vi≥100mV,调制信号的频率fΩ=1KHz,该电路的元件参数设计如下:

图中Dl、D2为限幅二极管。C1是输入耦合电容,Rl、C2组成限幅放大器的输入偏置滤波,滤除FM信号中的杂波。R3和RP对2脚提供输入电流I2,用来控制环路增益和VCO的锁定范围,总电阻R与电流12的关系为:

式中的1.3V是由于NE564的13脚电压为1.3V,I2一般为几百毫安,调节电位器RP使环路增益和VCO的锁定范围达到最佳值。R4是VCO输出端必须接的上拉电阻。C3、C4与内部两个对应电阻(阻值R=1.3kΩ)分别组成一阶RC低通滤波器。其截止角频率为:

滤波器的性能对环路入锁时间的快慢有一定影响,可根据要求改变C3、C4的值。VCO的固有振荡频率fv与定时电容Ct的关系为:

工作频率为41.4MHz时,由式(3)或振荡频率fv与Ct的关系曲线图5,得出Ct≈11pF,可用6pF和3/20pF电容并联使用。C5和C6用来滤除电源中的高低频交流分量。C7、C8和R5组成π型滤波器,用来滤除输出信号中的谐波分量。

该电路通过调试,中心频率工作在41.4MHz,频偏可达1MHz以上,输出电压在O.4V以上。

更多锁相环知识请访问 http://www.elecfans.com/zhuanti/PLL.html

-

模拟锁相环和数字锁相环区别2023-02-15 6963

-

模拟锁相环NE564在FM解调电路中的应用是什么?2021-05-31 2969

-

基于模拟锁相环NE564的FM解调电路应用2019-07-15 4217

-

利用锁相环芯片NE564和CD4046实现FSK信号的调制与解调电路的设计2017-10-30 49532

-

NE564做FSK解调电路输入信号的灵敏度是多少2017-02-10 4523

-

利用锁相环提取调幅信号的载波的一些疑问 ?2016-11-09 7338

-

集成电路模拟锁相环原理及NE564在实验电路中的应用2016-01-20 1671

-

求助啊,关于寻找合适的FM解调芯片的问题2015-01-20 5428

-

关于ne564的FSK调制电路的问题2013-03-19 12359

-

关于NE564的使用2012-08-01 3284

-

集成锁相环芯片应用 PPT培训资料2011-03-15 1720

-

数字锁相环(DPLL),数字锁相环(DPLL)是什么?2010-03-23 6210

-

NE564的应用电路描述2009-05-19 1994

-

模拟锁相环应用实验2009-03-22 1284

全部0条评论

快来发表一下你的评论吧 !