Intel FPGA系列产品介绍

描述

概述

自从Altera被Intel收购后,似乎放弃了整个中国市场,Altera市场占有率被其他FPGA厂家所侵蚀,国内目前还有一些公司用Altera的FPGA(CPLD居多),所以今天我们再去了解一下Intel FPGA系列产品。

PS:目前国内Xilinx ZYNQ系列使用比例非常高,其实Altera当年对标ZYNQ产品Clcyone V及Arria V系列SoC FPGA设计的架构要比ZYNQ更加合理,但是时事造英雄,当年Altera忙着“被”收购,导致SoC FPGA系列FPGA推广被自己“扼杀”,所以国内应用Altera SoC FPGA的很少,相应 的文档很少。当年我使用的第一款SOC FPGA就是Cyclone V(DE1-Soc),所有的问题都需要自己解决,当时的技术支持也只有TB上 的商家,很多问题都不能解决,跑个系统都花费了一个月时间,后面就转投Xilinx的怀抱了,诶!真香!

目前,Intel FPGA主要有5个系列,分别为:Agilex、Stratix、Arria、MAX、Cyclone系列,每个系列又根据不同应用场合有不同的小系列(我们称为二级系列),因为一些二级系列芯片早已停产,我们介绍时会从二级系列最新开始介绍,向前介绍,介绍到常用系列结束为止。

从上面可以简单分两个系列Agilex系列是收购Altera后推出的系列FPGA,其他系列基本都是Altera没被收购时的系列FPGA。这样区分其实没太大意义,只是想说的是。。。从Agilex系列之后Altera基本从国内消失了。

Agilex系列FPGA

英特尔 Agilex FPGA 家族从战略地位可以看做是Xilinx Ultrascale+系列对标产品。

英特尔 Agilex FPGA 家族融合了英特尔 10 纳米 SuperFin 制程技术、与英特尔专有嵌入式多管芯互联桥接(EMIB)集成的 3D 异构系统级封装(SiP),以及基于芯片的创新架构,可为各种应用提供定制的连接和加速功能。

这种全新架构支持 FPGA 结构与专用逻辑块结合,比如收发器、处理器接口、优化的I/O、自定义计算、英特尔 eASIC 器件和许多其他功能,从而创建面向每种应用实现独特优化的解决方案。英特尔 Agilex SoC FPGA 还集成了四核 Arm* Cortex-A53 处理器,可提供高系统集成水平。

英特尔 Agilex FPGA分为下面主要的三个系列,主要如下:

Agilex F系列FPGA

英特尔 Agilex F 系列 FPGA 和 SoC FPGA 集成了带宽高达 58 Gbps 的收发器、增强的 DSP 功能、高系统集成度和第二代英特尔 Hyperflex 架构,适用于数据中心、网络和边缘的各种应用。英特尔 Agilex F 系列 FPGA 和 SoC 家族还提供集成四核 Arm* Cortex-A53 处理器的选项,以提供高系统集成度。

Agilex I系列FPGA

英特尔 Agilex I 系列 SoC FPGA 针对高性能处理器接口和带宽密集型应用进行了优化。通过 Compute Express Link 提供面向英特尔 至强 处理器的一致性连接、增强型 PCIe* Gen 5 支持和带宽高达 112 Gbps 的收发器,使得英特尔 Agilex I 系列 SoC FPGA 成为需要大量接口带宽和高性能的应用的理想选择。

产品简表如下:

Agilex M系列FPGA

英特尔 Agilex M 系列 SoC FPGA 针对计算密集型和内存密集型应用进行了优化。英特尔 Agilex M 系列 SoC FPGA 提供面向英特尔 至强 处理器的一致性连接、HBM 集成、增强型 DDR5 控制器和英特尔 傲腾 DC 持久内存支持,针对需要大量内存和高带宽的数据密集型应用进行了优化。该产品家族即将上市(目前官网还没上市)。

Stratix系列FPGA

这一系列部分人还是很熟悉的,从战略上讲对标Xilinx V系列FPGA。

| 设备产品家族 | Stratix 10 | Stratix V | Stratix IV | Stratix III | Stratix II GX | Stratix II | Stratix GX | Stratix |

|---|---|---|---|---|---|---|---|---|

| 推出年份 | 2013 年 | 2010 年 | 2008 年 | 2006 | 2005 | 2004 年 | 2003 年 | 2002 年 |

| 制程技术 | 14 纳米 三栅极 | 28 纳米 | 40 纳米 | 65 纳米 | 90 纳米 | 90 纳米 | 130 纳米 | 130 纳米 |

目前在售产品

Stratix 10 FPGA 和 SoC

Stratix 10 FPGA又分为以下几个系列:

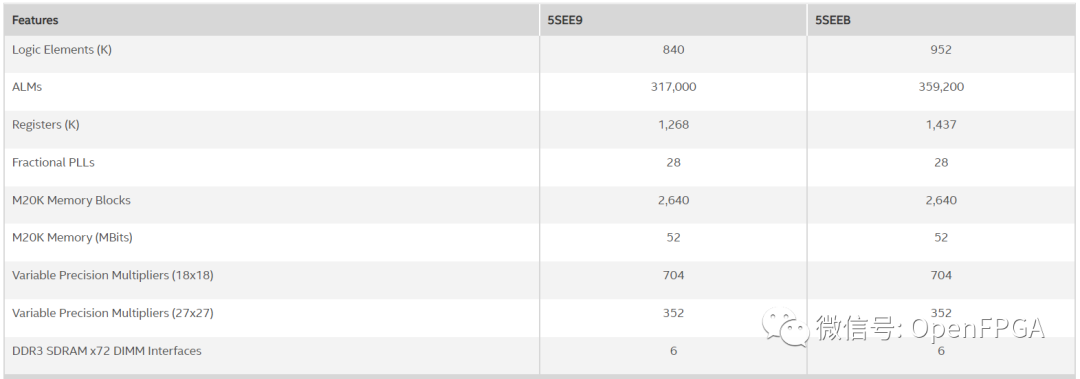

选型参考

Stratix 10 FPGA 和 SoC 硬核处理器系统(HPS)

Intel Stratix 10 SoC硬核处理器系统(HPS)是Intel业界领先的第三代HPS。通过采用Intel的14-nm三栅极 技术性能, Intel Stratix 10 SoC器件采用集成四核64-bit ARM Cortex-A53,实现了高于上一代SoC两倍的性能。HPS通过增添一个系统存储器管理单元也实现了全系统硬件虚拟化功能。这些在体系结构上的改进确保了 Intel Stratix 10 SoC将满足当前和未来嵌入式市场的要求,包括:无线和有线通信,数据中心加速以及众多军事应用。

Stratix 10 FPGA命名规则

Stratix 10 (GX, SX, TX) Devices

Stratix 10 (MX) Devices

Stratix 10 (DX) Devices

Stratix V系列FPGA

英特尔的 28 纳米 Stratix V FPGA 在高端应用中实现了高带宽、高系统集成度,不但非常灵活,而且降低了成本和总功耗。

分为三个系列,具体如下:

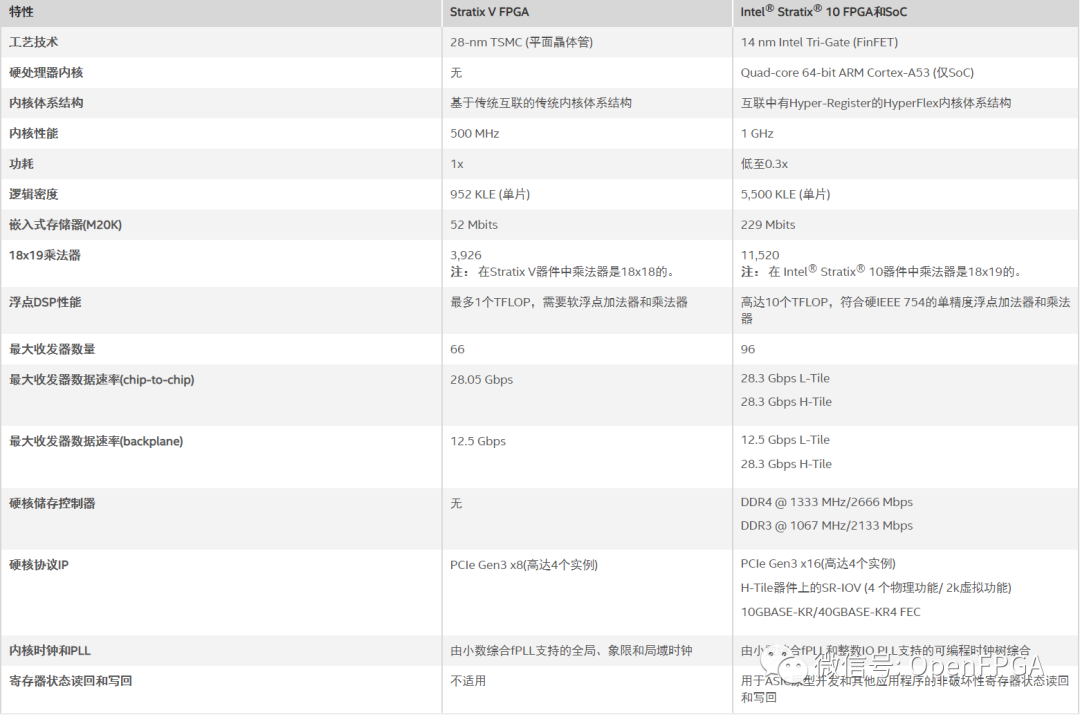

与Stratix 10对比如下

Stratix V系列FPGA选型参考

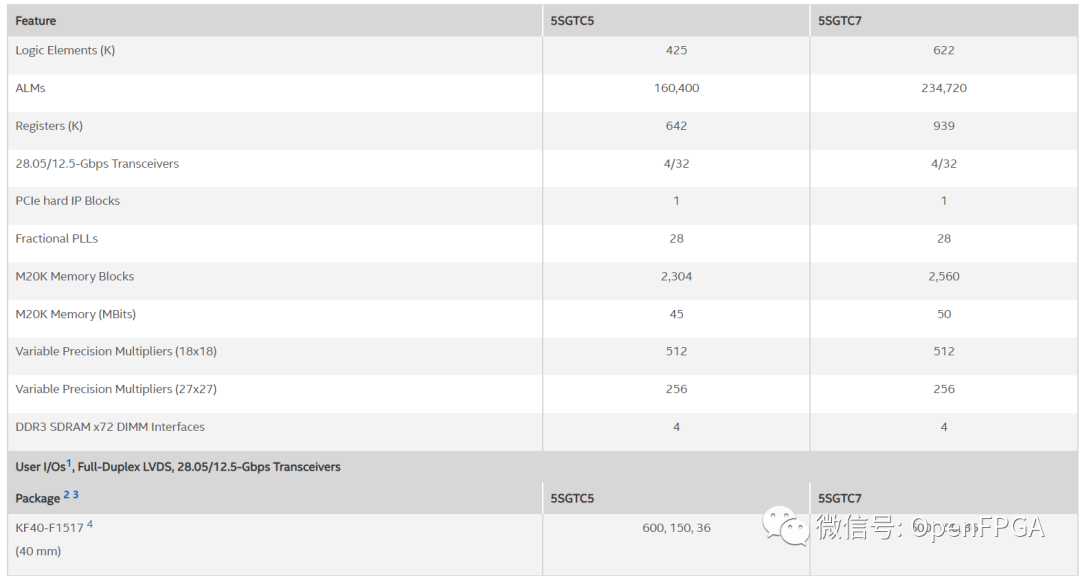

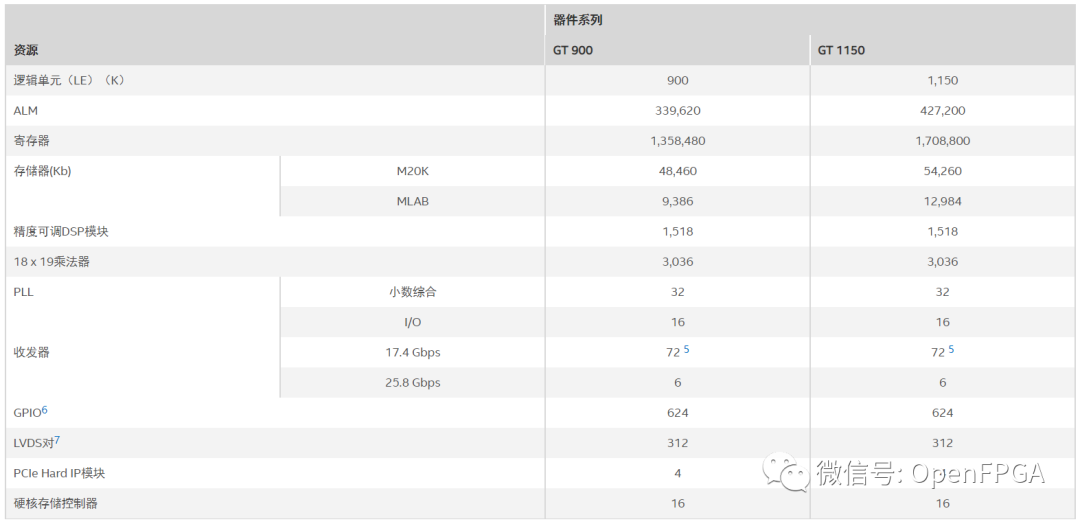

Stratix V GT Device

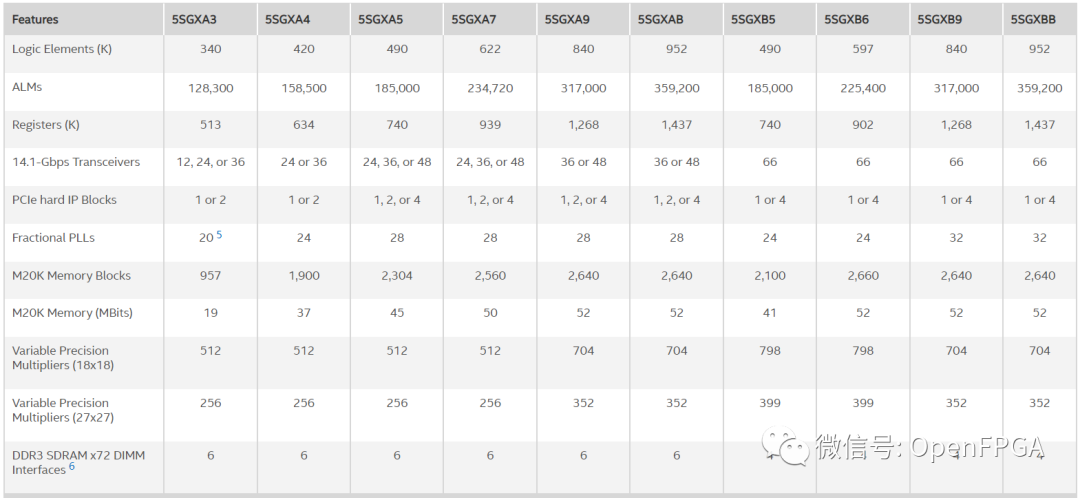

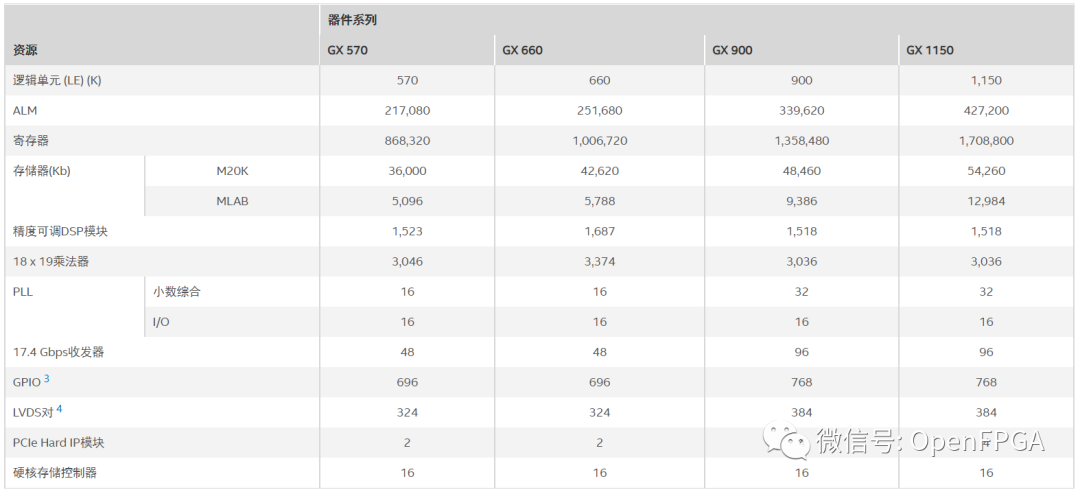

Stratix V GX Device

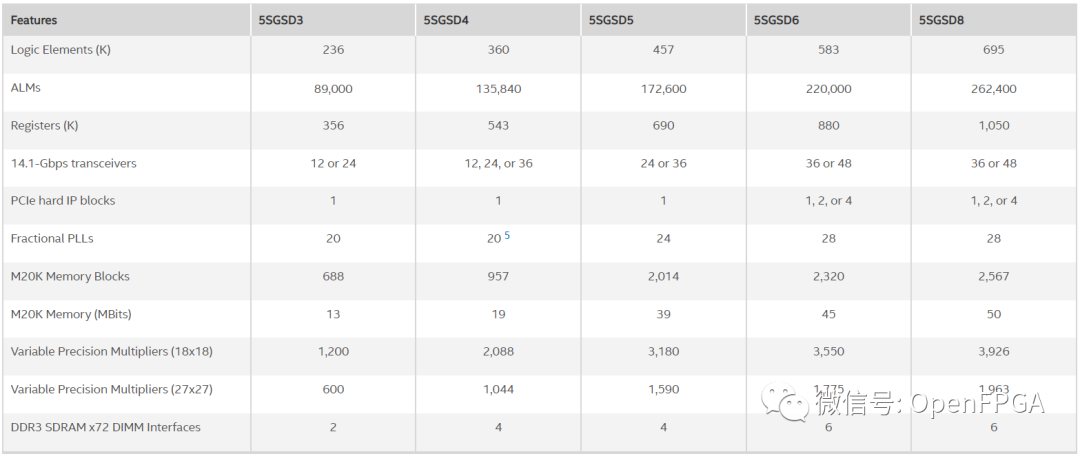

Stratix V GS Device

Stratix V E Device

Stratix V系列FPGA命名规则

Stratix IV系列虽然现在应用也很多,这里就不过多介绍了,有兴趣的请移步:https://www.intel.cn/content/www/cn/zh/products/details/fpga/stratix/iv.html?wapkw=stratix%20iv

Arria系列FPGA

Arria系列从战略角度讲对标的是Xilinx K系列FPGA。

英特尔 Arria 设备家族可提供中端市场中的最佳性能和能效。英特尔 Arria 设备家族拥有丰富的内存、逻辑和数字信号处理 (DSP) 模块特性集,以及高达 25.78 Gbps 收发器的卓越信号完整性,支持您集成更多功能并最大限度地提高系统带宽。此外,Arria V 和英特尔 Arria 设备家族的 SoC 产品可提供基于 ARM 的硬核处理器系统 (HPS),从而进一步提高集成度和节省更多成本。

各代Arria FPGA

| 家族 | Arria GX | Arria II GX | Arria II GZ | Arria V GX, GT, SX | Arria V GZ | Arria 10 |

|---|---|---|---|---|---|---|

| 推出年份 | 2007 | 2009 | 2010 年 | 2011 | 2012 | 2013 年 |

| 制程技术 | 90 纳米 | 40 纳米 | 40 纳米 | 28 纳米 | 28 纳米 | 20 纳米 |

Arria 10 FPGA 和 SoC

借助公开可用的 OpenCores 设计,英特尔 Arria 10 FPGA 的内核性能不仅显著高于竞争产品,并且还提供了高达 20% 的 Fmax 优势。此外,英特尔 Arria 10 家族提供可编程逻辑行业唯一基于 20 纳米 ARM* 的 SoC,可提供高达 1.5 GHz 的时钟频率。英特尔 Arria 10 家族还首次在 FPGA 中提供了对浮点运算的强化支持,从而将 DSP 性能提升到新的水平。

架构如下:

主要分为以下三个系列:

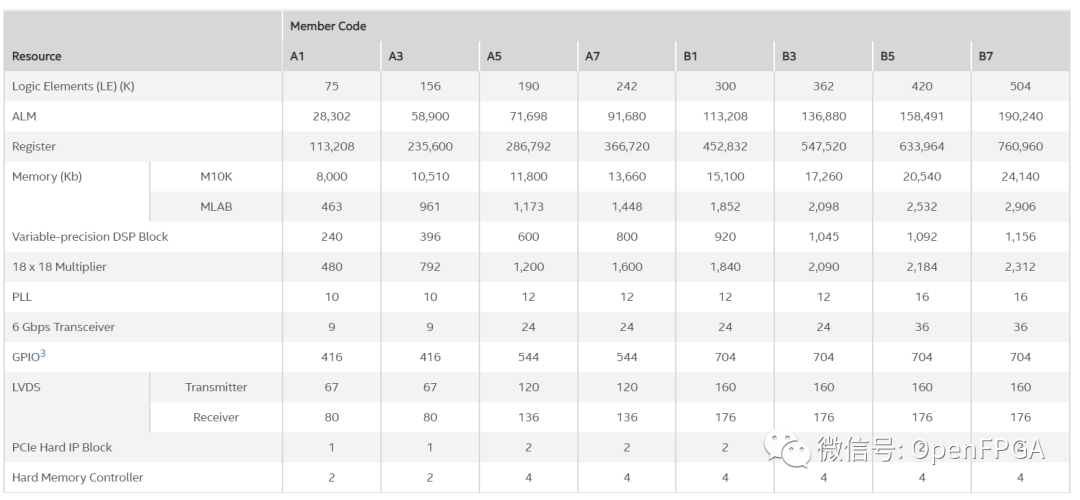

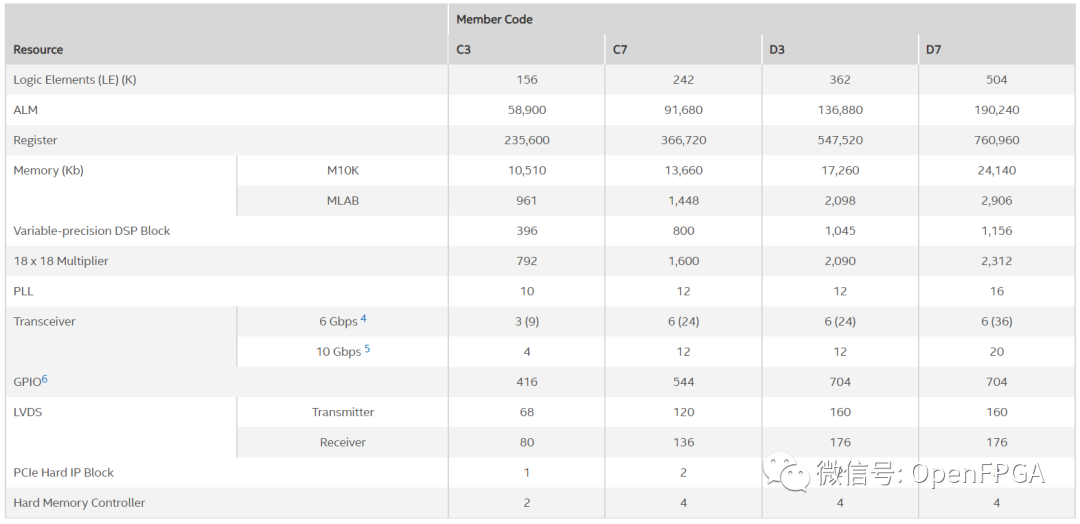

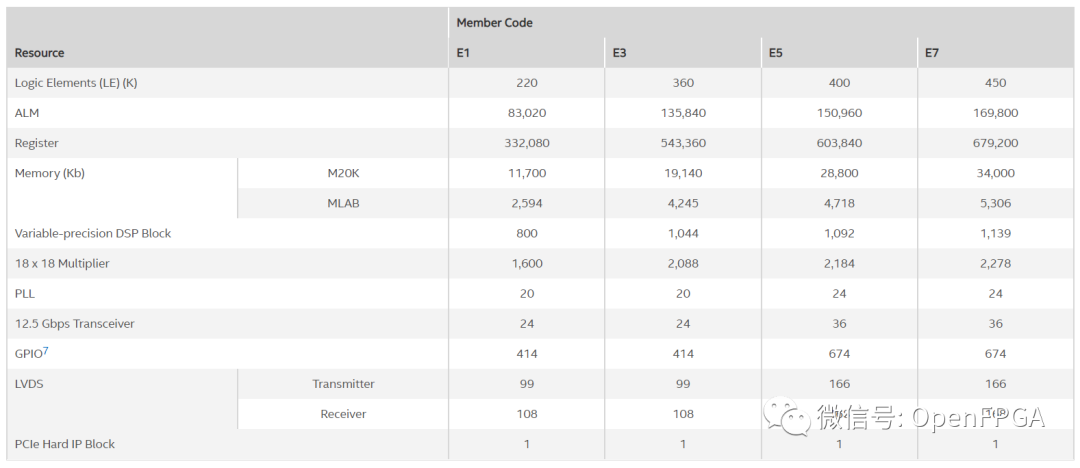

Arria 10 FPGA 和 SoC选型参考

Arria 10 GX器件

Arria 10 GT

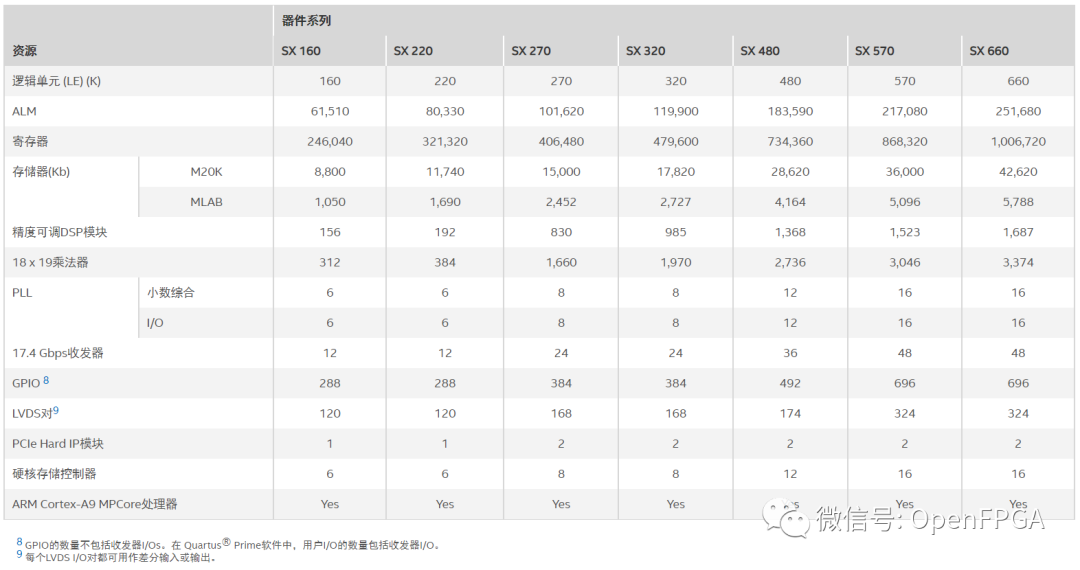

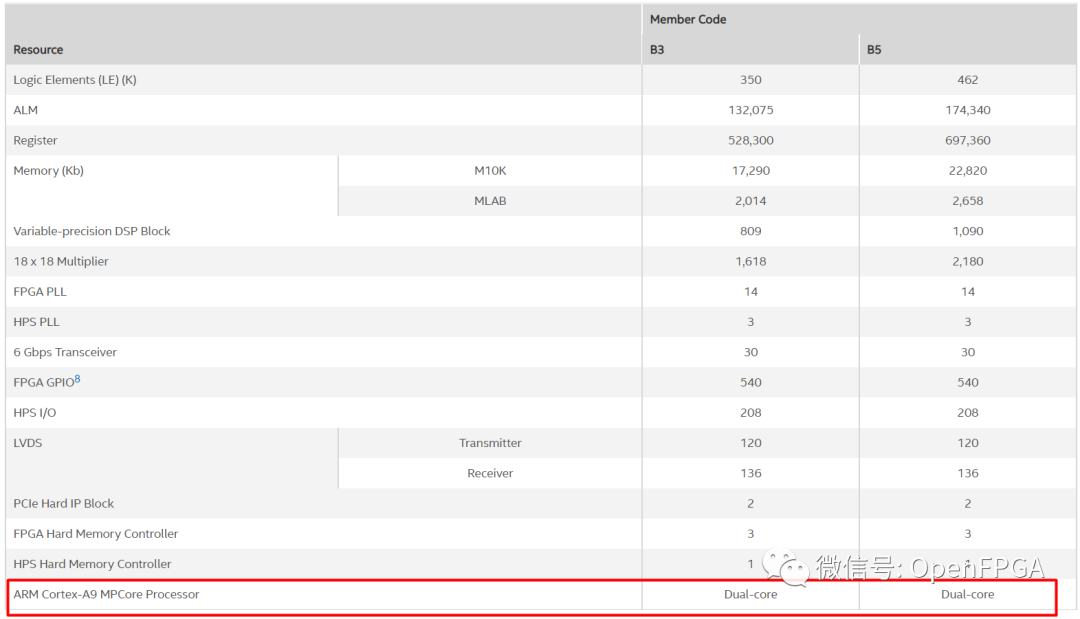

Arria 10 SX

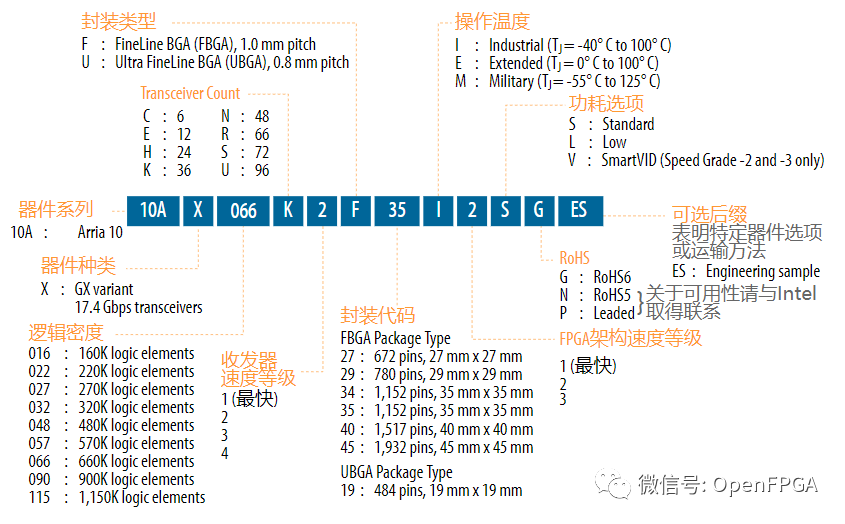

Arria 10 FPGA 和 SoC命名规则

Arria 10 GX器件

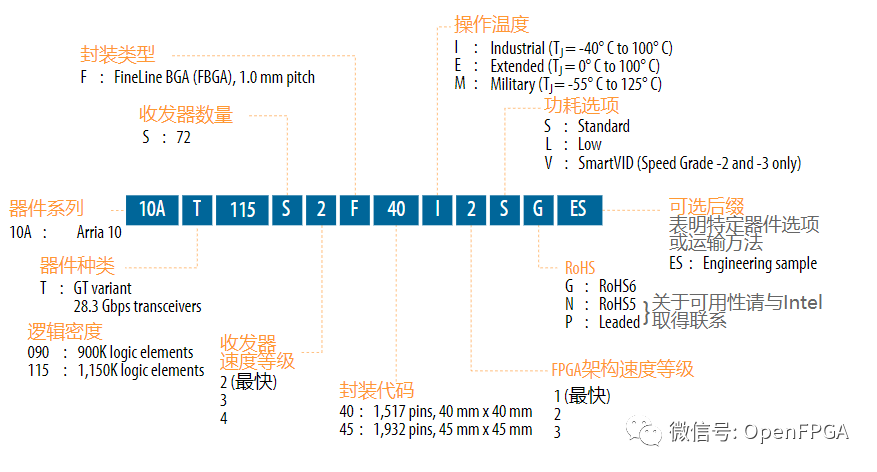

Arria 10 GT

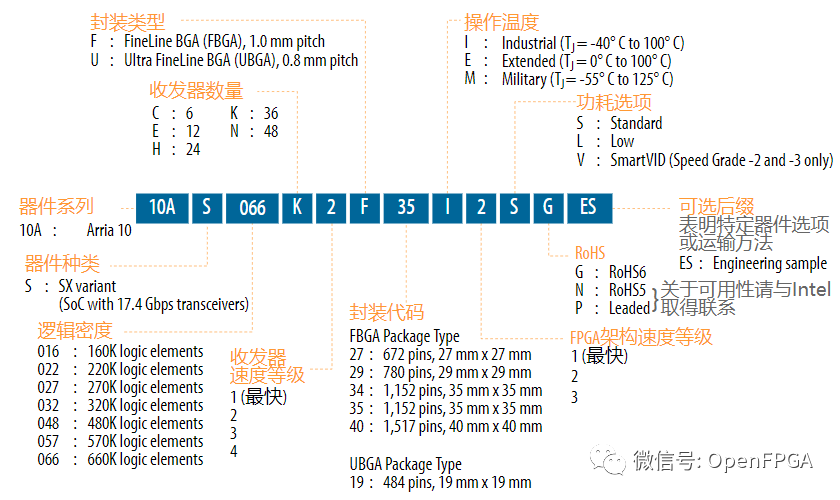

Arria 10 SX

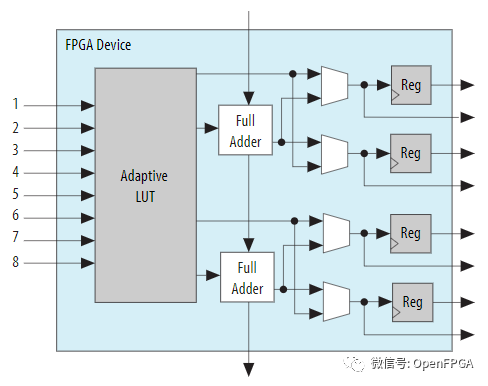

自适应逻辑模块-ALM

如图 1 所示,增强的 ALM 具有 8 个输入,包括一个可拆分查找表 (LUT)、两个专用嵌入式加法器和 4 个专用寄存器。

实施基于 7 - 输入 LUT 的选定函数、所有 6 - 输入逻辑函数和两个独立函数(由更小的 LUT 组成,如两个独立的 4 输入 LUT),以优化内核利用率。为每个 8 - 输入可拆分 LUT 提供 4 个寄存器。这支持 器件最大限度提升核心性能和核心逻辑利用率,并为寄存器密集型和高度管道化设计提供更轻松的时序收敛。

ALM 特性与优势

| 每 ALM 的可用资源 | 优势 | 优势 |

|---|---|---|

| 8-输入可拆分LUT | 可实施任何 6 - 输入逻辑函数和特定 7 - 输入函数,可拆分为更小的独立 LUT,如两个独立的 4 - 输入 LUT | 英特尔 Quartus 设计软件具有可拆分性,并针对性能、效率、功耗和面积进行了优化 |

| 两个嵌入式加法器 | 支持两个两位加法或两个三位加法,无需任何额外的资源 | 可以从相同的 ALM 中生成操作数,无需任何额外的逻辑 |

| 4 个寄存器 | 最佳寄存器逻辑比率,以确保器件不受寄存器限制 | 丰富的寄存器,以提升寄存器密集型应用或管道设计的性能 |

| 4 个输出 | 可以在两个输出函数之间分配单个 ALM 的输入,支持快速运行广泛的输入函数,以及窄输入函数高效利用剩余资源 | |

| MLAB | 英特尔 Stratix 系列 FPGA 的核心包括一个逻辑阵列模块,该模块由普通的 ALM 组成,或被配置为简单的 640 位双端口 SRAM 模块(被称作 MLAB) | MLAB 可以被配置为 64 x 10 或 32 x 20 简单双端口 SRAM 模块。MLAB 经过优化,可以 600-MHz 时钟速度的最大性能来实施过滤器延迟线、小型 FIFO 缓冲器和移位寄存器 |

Arria V FPGA 和 SoC

架构

可以分为如下几个系列:

主要有以下产品

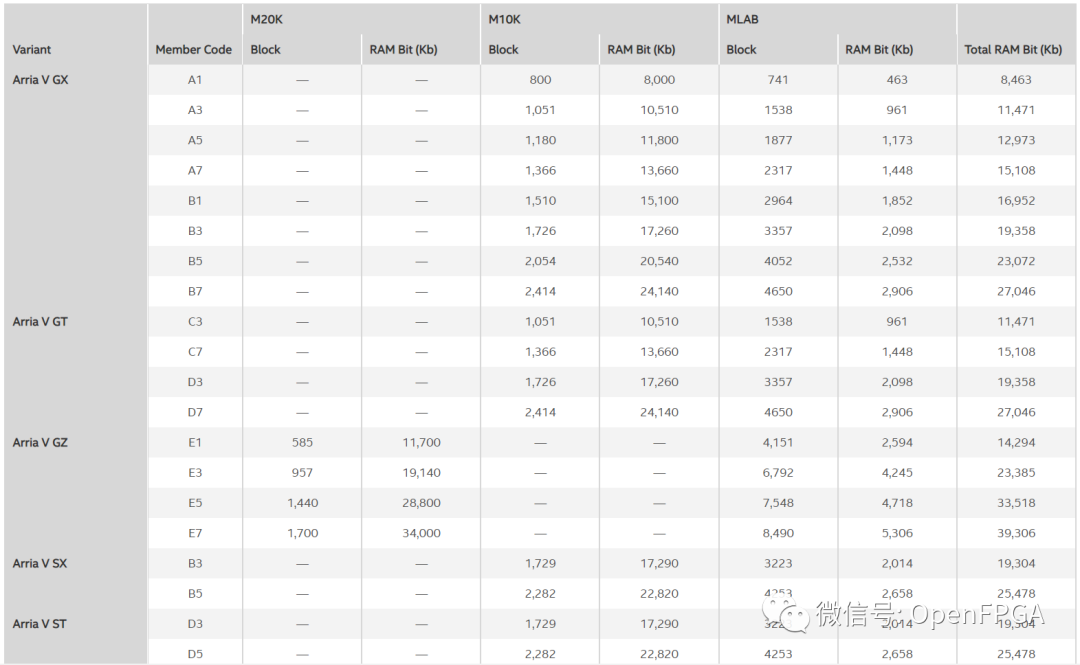

Arria V FPGA 和 SoC选型参考

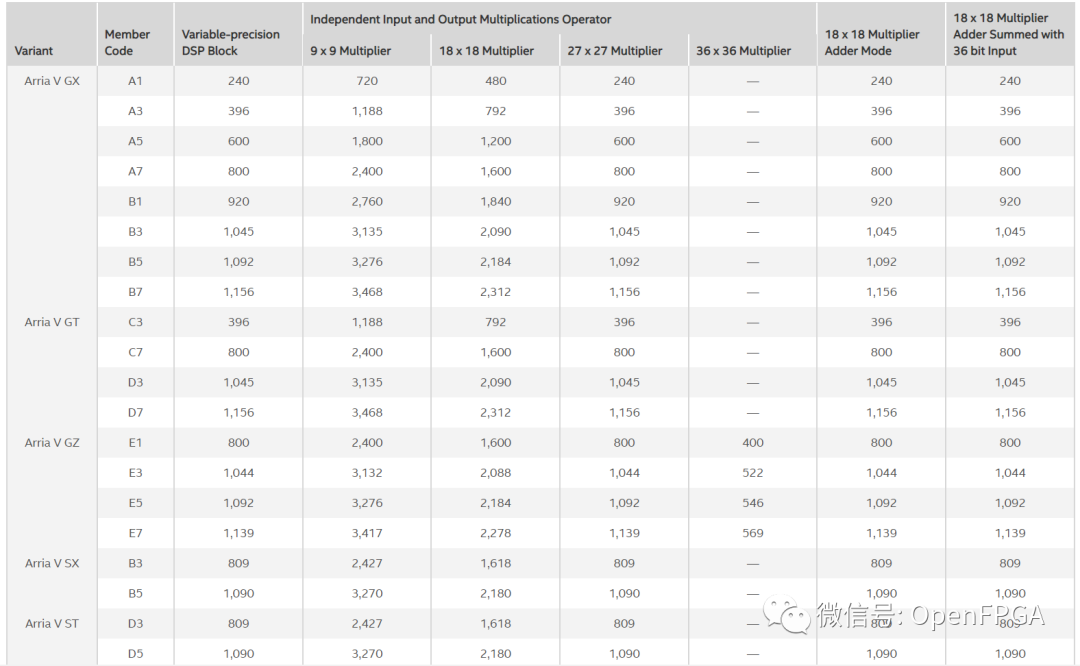

Arria V GX

Arria V GT

Arria V GZ

Arria V SX

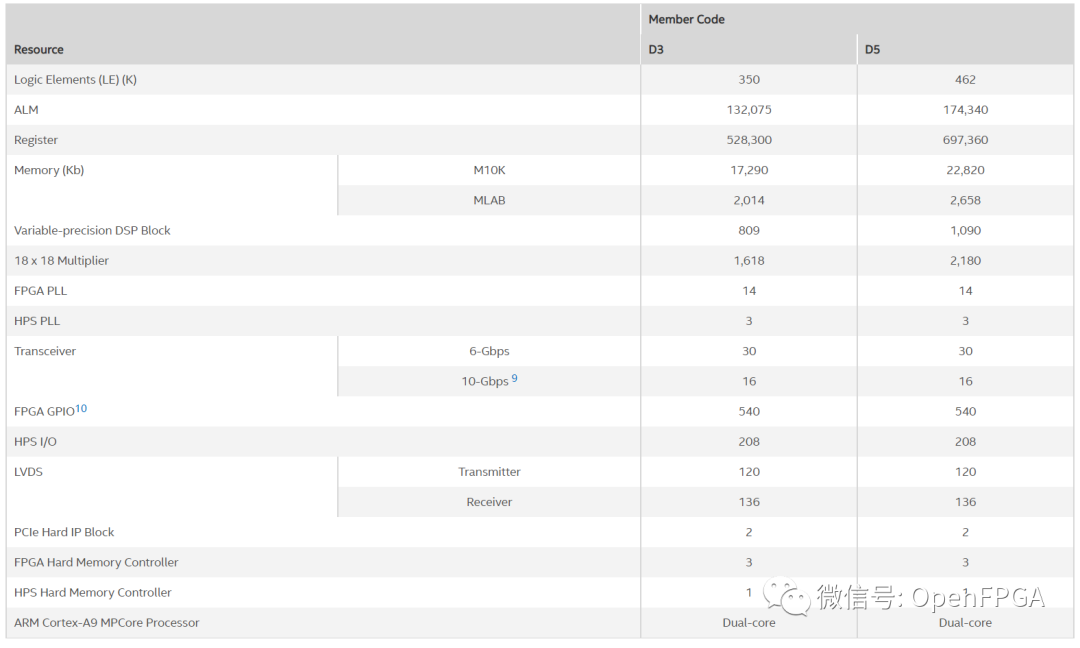

Arria V ST

Arria V FPGA 和 SoC命名规则

Arria V GX

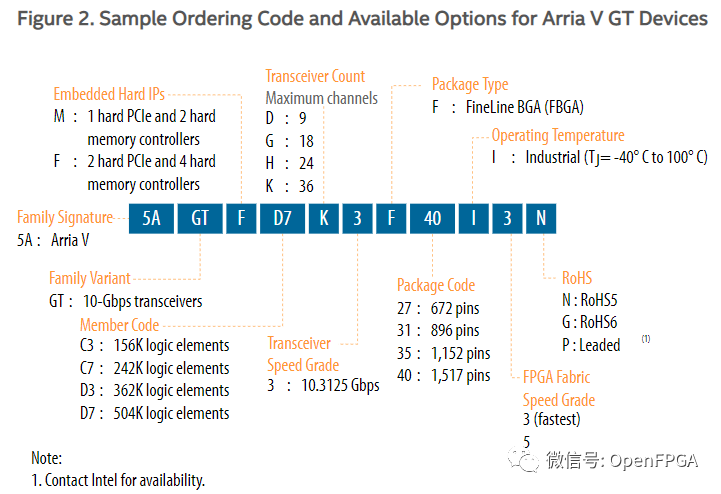

Arria V GT

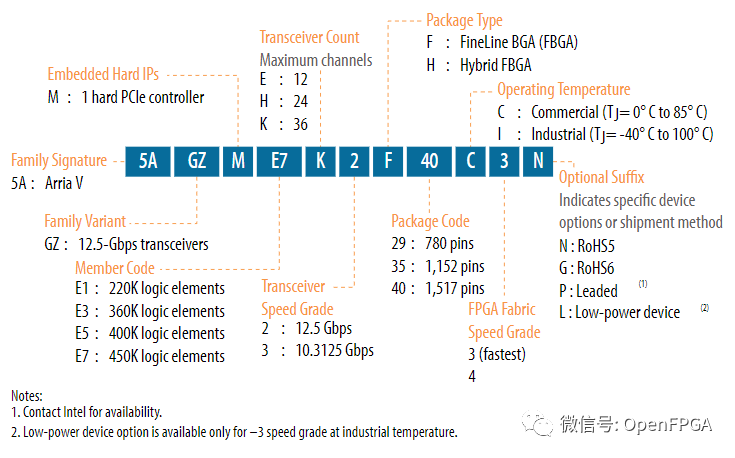

Arria V GZ

Arria V SX

Arria V ST

Arria V FPGA 和 SoC汇总

Intel MAX 系列FPGA/CPLD

Intel MAX 系列FPGA/FPGA 战略上对标的是Xilinx的CPLD系列。

这个系列本来是Altera系列CPLD,但是后续Intel将这一些更改,将CPLD更改为FPGA(小型),这一更改或许代表着未来CPLD的发展(后续市场上或将不再有CPLD)。

这一系列改变主要架构还是CPLD,但是内部结构还是FPGA,所以不能称为CPLD,更像是CPLD+FPGA,Intel推广时还是将这一些列作为CPLD推广。

所以这里需要分为两个系列分别介绍。

| 系列 | 成熟的 CPLD 家族MAX II CPLD | MAX IIZ CPLD | MAX V CPLD | 英特尔 MAX 10 FPGA |

|---|---|---|---|---|

| 推出年份 | 1995 - 2002 | 2004 年 | 2007 | 2010 年 |

| 制程技术 | 0.50-0.30 微米 | 180 纳米 | 180 纳米 | 180 纳米 |

| 主要功能 | 5.0 V I/O | 较多的 I/O 数量 | 低静态功耗 | 低成本、低功耗 |

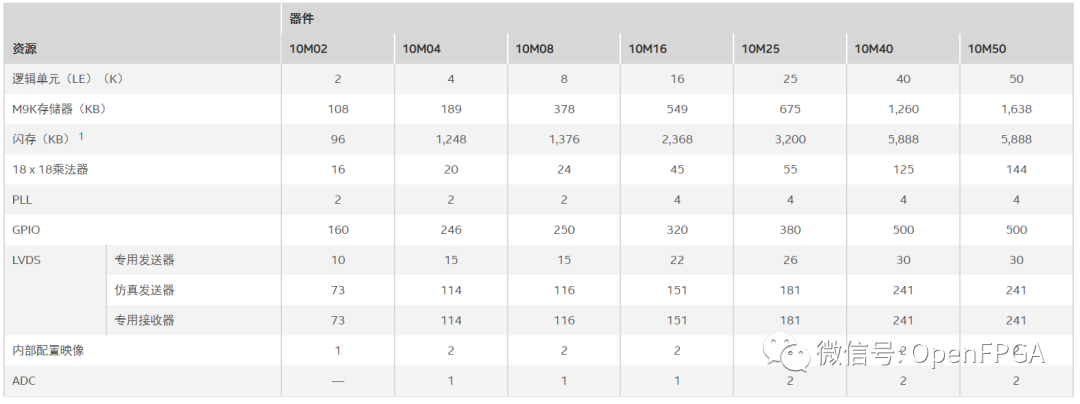

Intel MAX 10 系列FPGA

英特尔MAX 10 FPGA 提高了外部系统组件功能的集成度,从而降低了系统级成本。与 CPLD 不同,55 纳米英特尔 MAX 10 FPGA 包括 FPGA 的全部功能,例如数字信号处理 (DSP)、带有模拟到数字转换器 (ADC)和温度传感器的模拟模块、嵌入式软核处理器支持、存储控制器和双配置闪存。

大约一下几种芯片:

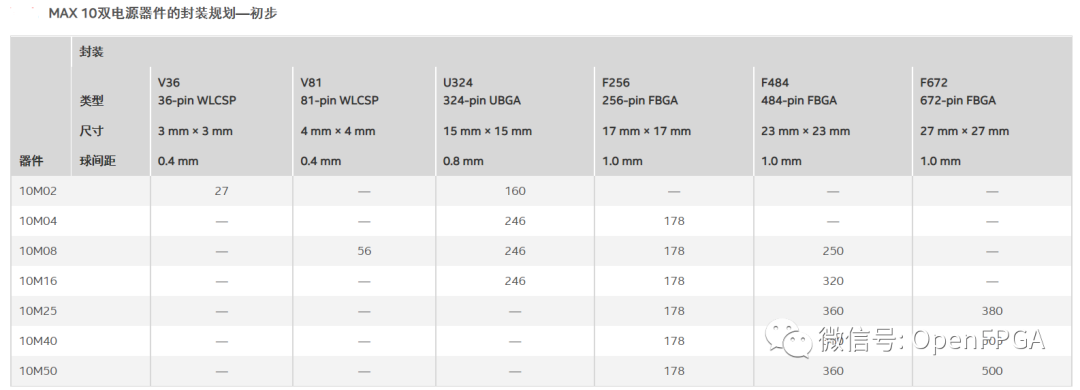

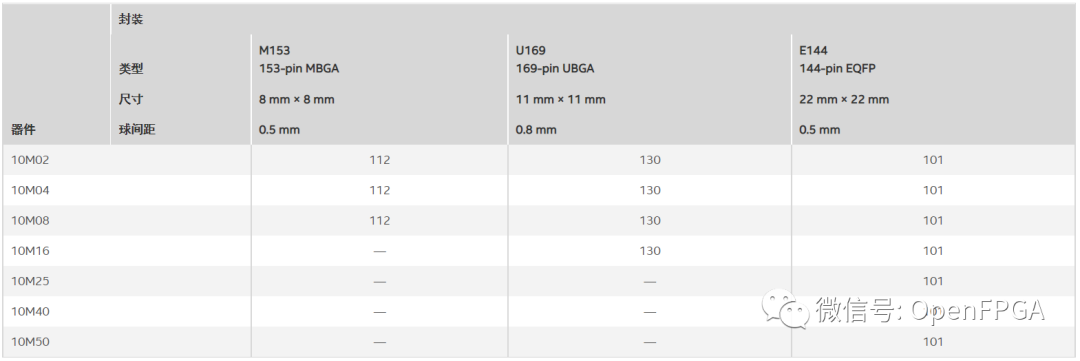

Intel MAX 10 系列FPGA选型规则

Intel MAX 10 系列FPGA命名规则

Intel MAX V 系列CPLD

实现了低成本、低功耗和片上特性,MAX V CPLD 是市场上最有价值的设备。MAX V 设备采用独特的非易失性架构,提供可靠的全新特性,总功耗比竞品 CPLD 降低多达 50%。MAX V 设备非常适合许多细分市场中的通用及功耗和空间受限设计,包括固网、无线、工业、消费类、计算机和存储,以及广播和军事等。MAX V CPLD 被利用在广泛的各种应用中,它们过去只能在上一代 ASIC、ASSP、FPGA 和分立逻辑器件中实现。

这一些列战略上应该对标的是Xilinx S系列。

这一系列FPGA应该是大家最熟知的,Altera在国内推广的系列,很多大学的课程设计使用 的FPGA应该都是Altera Cyclone系列FPGA,而且很多人的启蒙FPGA应该也是这一系列FPGA(很多开发板都是这一系列FPGA),资料就不用多说了。

这里就简单介绍一下Cyclone 10、Clcyone V 及ClCyone IV(简单介绍)。

| FPGA | Cyclone FPGA | Cyclone II FPGA | Cyclone III FPGA | Cyclone IV FPGA | Cyclone V FPGA | Cyclone 10 FPGA |

|---|---|---|---|---|---|---|

| 推出年份 | 2002 年 | 2004 年 | 2007 | 2009 | 2011 | 2017 |

| 建议新设计使用 | 否 | 否 | 否 | 是 | 是 | 是 |

Intel Cyclone 10系列FPGA

Intel Cyclone 10基本被其他系列给湮灭掉了,和Xilinx S7系列一样,只是“存在”,低端基本使用MAX 10系列了,高端也不会使用该系列。

Cyclone V FPGA 提供了行业最低的系统成本和功耗,以及全新的性能水平,使设备产品家族成为突出您的大容量应用优势的理想之选。相比前代产品,总体功耗降低了高达 40%,您还可以获得高效的逻辑集成功能、集成收发器变体和 SoC FPGA 变体(包括基于 ARM* 的硬处理器系统 (HPS))。

Intel Cyclone V系列FPGA命名规则

GX 和 E 设备架构都有非常高效的互联和低偏移时钟网络,支持时钟和数据信号的逻辑结构之间互联。

Intel/Altera 系列FPGA简介至此为止了,大部分现有的Intel的FPGA都有介绍,希望 对大家有帮助。

PS:最近翻阅Intel官网,发现浏览速度及中文支持似乎回到了N年前,比中间过渡期间好多了,或许”Intel“ YES!马上又要来了。

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思 UltraFast 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

-

深度探索:Intel RealSense D400系列产品全方位解析2026-03-30 165

-

Intel fpga芯片系列有哪些2024-03-14 2469

-

油田泥浆压力测量系列产品介绍2024-03-11 477

-

AMD推出Spartan UltraScale+ FPGA系列产品2024-03-07 1716

-

Intel和Xilinx的FPGA系列芯片命名规则2023-05-26 3089

-

FPGA产品GW1N 1系列产品Pinout手册2022-09-14 595

-

Intel FPGA系列产品详解2021-10-08 12258

-

RX系列产品分别分为哪几种?RX系列产品具备哪些功能?2021-07-01 3633

-

高云半导体推出最新安全FPGA系列产品2019-07-03 1586

-

Achronix推出Speedster7tFPGA系列产品 简化设计FPGA灵活性2019-05-27 4774

-

54600系列产品说明2019-01-21 1670

-

关于英飞凌XMC4000系列产品的介绍2018-07-11 6506

-

ARM 嵌入式发展: Kinetis L 系列产品介绍2012-07-31 2427

-

Intel Atom处理器E6x5C系列产品结构2011-11-30 3257

全部0条评论

快来发表一下你的评论吧 !