数字电路教程的组合逻辑部分介绍

描述

在数字电路教程的组合逻辑部分,最经典的示例除了加法器以外就是:

Encoder - 编码器

Decoder - 译码器

Multiplexer - 简写Mux,多路复用器,也叫数据选择器

Demultiplexer - 简写Demux,解复用器,也叫数据分配器

其实是两对概念:Encoder/Decoder是跟code(码)相关的正反两个操作,Mux/Demux是跟数据流相关的正反两个操作。

翻看各种教科书,我们很难理清楚它们之间的功能差异以及相互之间的关系,只是有一些点滴应用在书本上提及。

这两组概念其实是非常重要的,是构成我们信息组织和信息传输的重要基础,并且在我们的生活中处处都能够找到与之对应的应用:

比如我们看谍战片中神秘的电报编码(要用密码本来翻译);我们用的键盘上面有100多个按键、而几根线就可以将它跟计算机连接;我们使用的旋转拨码开关、模数转换器中通过比较器输出的比较结果到最终用于表征模拟信号大小的数据,这些都被称为Encode - 编码。

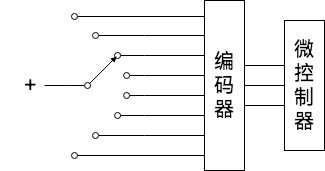

单刀八掷的旋转开关可以用3根二进制数据线来表征其状态

简而言之,编码器是一种把熟悉的数字、字符或符号转换成二进制代码的装置,它将给定的信息编码成更紧凑的形式,主要用于减少表示给定信息所需的比特数。在数字系统中,编码器用来传输或存储信息,通过编码传输链路可以使用更少的线路来传输或更少的空间来存储。将量化的音乐通过编码器转换为MP3格式,将采集到的视频流通过编码器转换为MP4的数据格式,这些过程都统称为“编码” ,当然在我们的数字电路教程中,只是通过最简单的示例来讲述其原理。

就像电报中的编码有很多中一样,用二进制来表征数字、字符或符号也有多种不同的方式,比如BCD、5421码、2421码、余3码、格雷码等,每种编码方式都有其优缺点,因此有用于不同的场景。

译码器(Decoder)是编码器的逆过程,它是把二进制表征的信息给翻译过来,或者说映射过来,我们生活中的门牌号、车牌号、邮箱、组合开关对多个灯的控制、嵌入式系统中的存储器/外设寻址,这些都是译码的过程,通过代码中的数字,找到其对应的对象。在数字计算中,代码中的数字都是用二进制(扩展为8进制、16进制等,本质上也是2进制)。数字电路教程中,在译码器部分最常用到的例子就是3:8译码器,这是因为74HC138就是这么一个IC,比较适合做各种实验,当然7段数码管的控制也是非常重要的实验项目让同学们来体会译码的过程,通过几根控制线的电平组合,可以点亮数码管上7个LED灯中的若干个,从而组合出我们需要显示的数字。

我们硬禾学堂也专门针对译码部分制作了两个视频案例,一个是2:4译码,一个是3:8译码,虽然看起来没啥大的区别,但我们还是通过这两个实例来让大家体会Verilog代码实现的不同方式,希望对学习Verilog的同学有帮助。

FPGA中的逻辑单元的基本构成就是LUT - 查找表,其理论基础就是译码,比如我们小脚丫FPGA中采用的是4输入LUTS,通过查找表的方式代替逻辑门的构成,4个输入作为RAM的地址,可以寻址16个不同的地址空间内存储的信息。

是不是感觉编码器/译码器用途很广?

那Mux/Demux呢?想象一下从四条不同路径过来的车辆要并线到一条路上,由红绿灯控制,控制部分就相当于一个分时切换的开关,根据开关的控制码来决定哪一路的车辆通行,Mux又称为多路数据选择器,Demux又被称为数据分配器。

其实MUX不仅用于数字器件中,模拟电路中也有这个概念,我们所说的模拟开关,可以切换不同的输入与输出的连接,在模拟电路中Mux和Demux是一体的,同一个电路即是Mux又是Demux。而数字的Mux和Demux需要使用不同的器件。

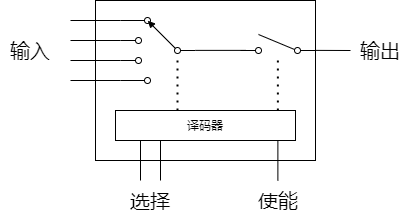

复用器的构成

从上面的图中可以看出译码器是复用器构成的重要部分。复用器的控制信号就是通过译码以后,对应到相应的控制端点,从而实现对输入信号的选择通过的。

复用器/解复用器的Verilog逻辑异常简单,有一点程序基础的同学一看就懂,比如下面的4选1多路选择器,一个case语句搞定,case的条件是2个选择数据为sel1、sel0,sel1和sel0的4种组合决定了一个LED同4个不同输入信号的连接。

很容易看懂,是因为我们任何一门编程语言中的if else、case本质上都是Mux的功能,只是我们太习以为常了而已。

module mult4 ( input wire a, //定义四位输入 input wire b, input wire c, input wire d, input wire [1:0] sel, //定义输出的选择变量 output reg led //定义选择器输出结果对应的led ); always@(sel) //根据sel结果选择输出,当sel变化时执行 begin case(sel) 2‘b00: led = a; 2’b01: led = b; 2‘b10: led = c; 2’b11: led = d; endcase end endmodule

从这几行代码看,FPGA的使用非常简单,不需要你画门与门之间的逻辑关系图,只需要用Verilog这种硬件描述语言来描述一下其因果关系就可以了。

与Encoder、Decoder、Mux、Demux相关的案例及其FPGA实现都汇总在www.stepfpga.com的网站百科中,如果您使用我们的Web IDE(不需要下载安装FPGA工具),也可以找到相关的参考案例,自己去发掘喽。

责任编辑:haq

-

组合逻辑设计原则--Combinational logic design principles-数字电路 (数字设计原理2009-09-26 6933

-

数字电路的应用介绍2018-08-28 3782

-

新编数字电路与数字逻辑2018-10-28 3392

-

数字电路与逻辑设计电路的分析和方法2021-08-06 1595

-

FPGA零基础学习:数字电路中的组合逻辑2023-02-21 1387

-

《数字电路与逻辑设计》答案2012-06-25 816

-

组合逻辑电路的设计与测试介绍2015-11-17 892

-

数字电路该怎么学_数字电路的学习方法(要点、注意事项)2018-03-23 36311

-

数字电路基础之组合逻辑电路的详细资料概述2018-10-17 1448

-

数字电路教程之组合逻辑电路课件详细资料免费下载2018-12-28 1411

-

数字电路中组合逻辑电路设计步骤详解2023-02-03 7922

-

数字电路的定义、应用及分类2023-07-31 15504

-

数字电路中的逻辑门电路分类2024-02-04 5990

-

数字电路与逻辑设计2024-03-11 590

-

组合逻辑电路逻辑功能的测试方法2024-07-30 2983

全部0条评论

快来发表一下你的评论吧 !