一文快速带你理解RTL与LUT之间的关系

描述

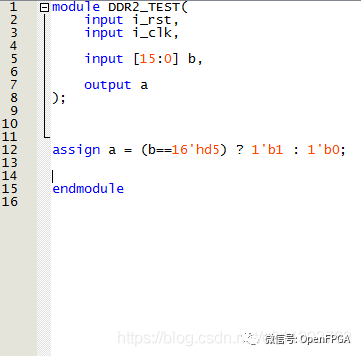

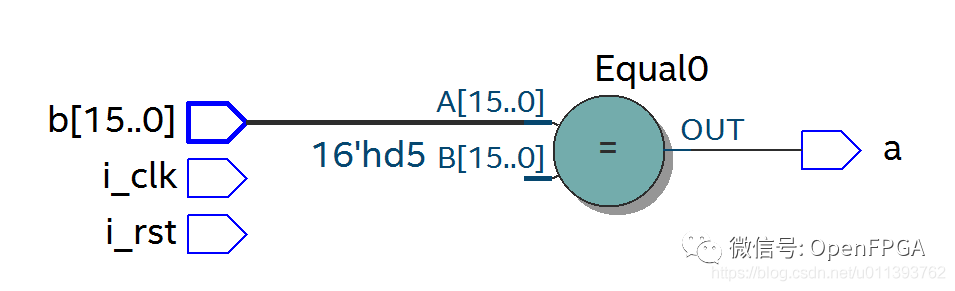

Quartus II EDA工具进行综合

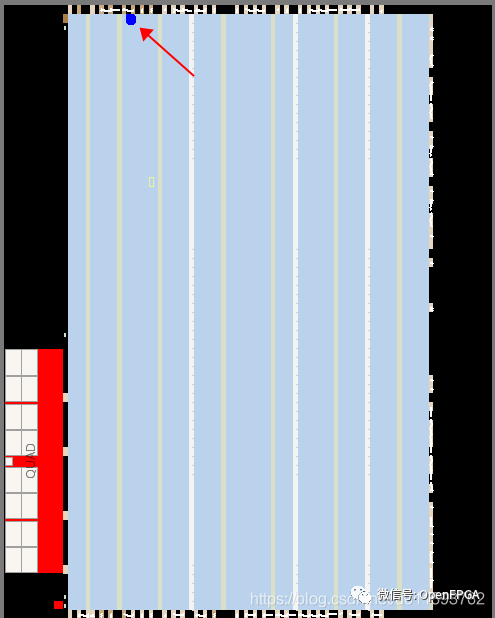

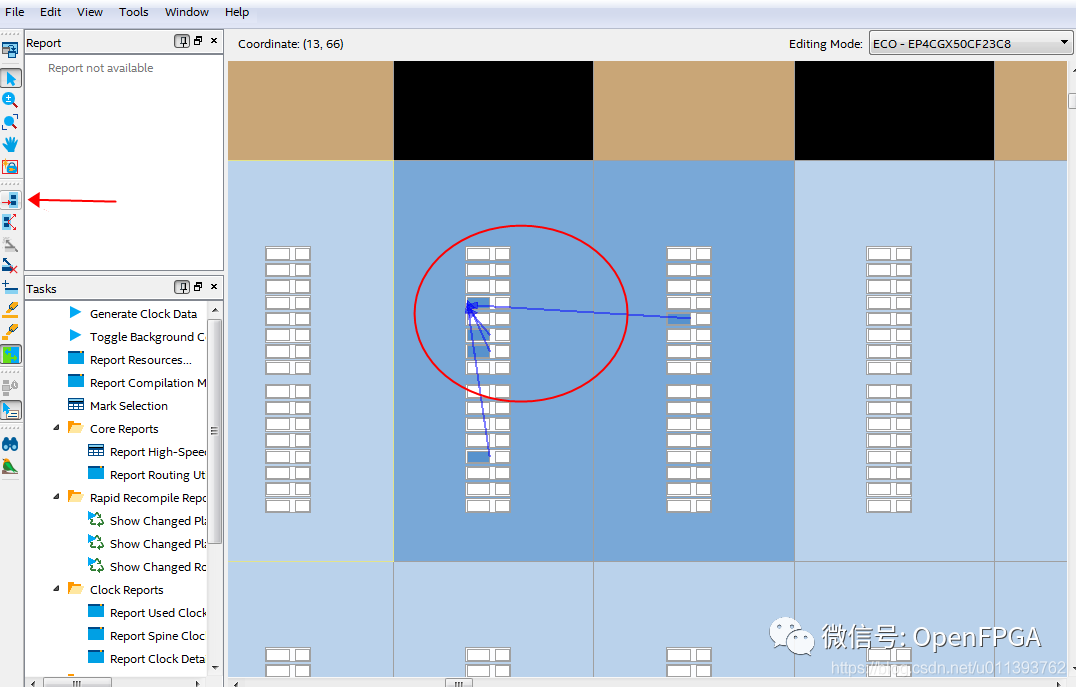

布局布线后,点击“Chip Planner”,Chip Planner打开后可以看到在版图模型中有一个块蓝色区域的颜色变深,说明有该区域的资源被占用,我们知道这是一个逻辑阵列块LAB,我们将该区域放大

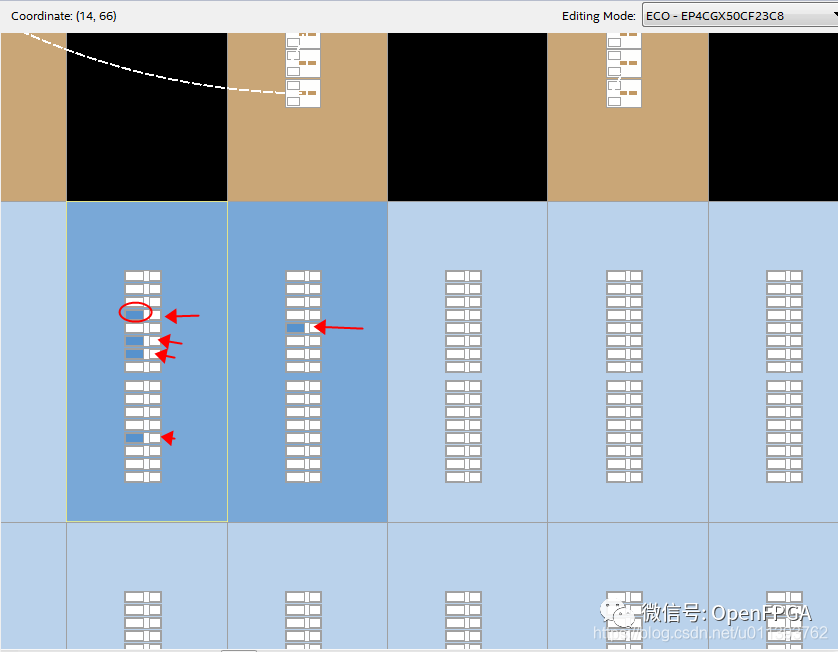

放大后可以看到蓝色变深的区域中有16个小块,这16个小块就是LE(它们的走线时延的关系如下:同一个LAB中(最快) 《 同列或者同行 《 不同行且不同列),其中只有一个LE的颜色变是蓝色的,说明该处的资源被使用了,双击蓝色的LE即可观察其内部的结构

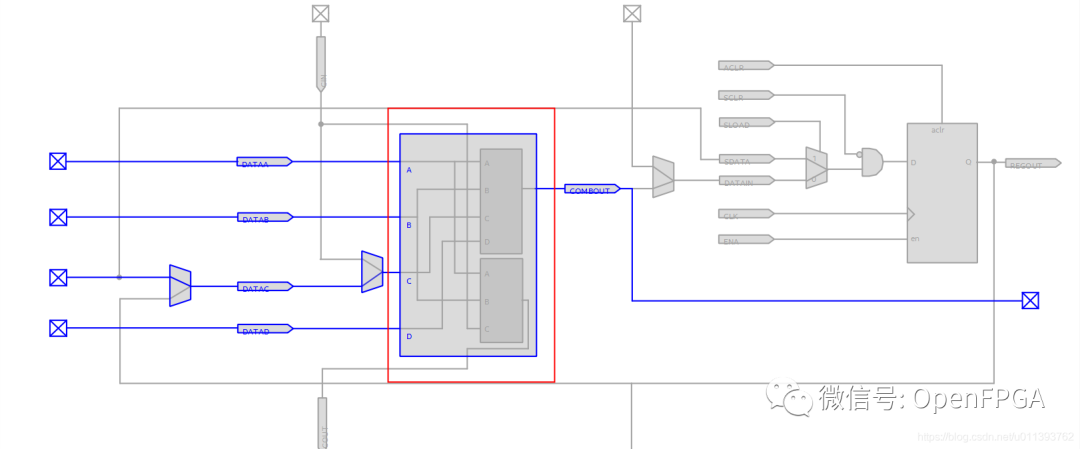

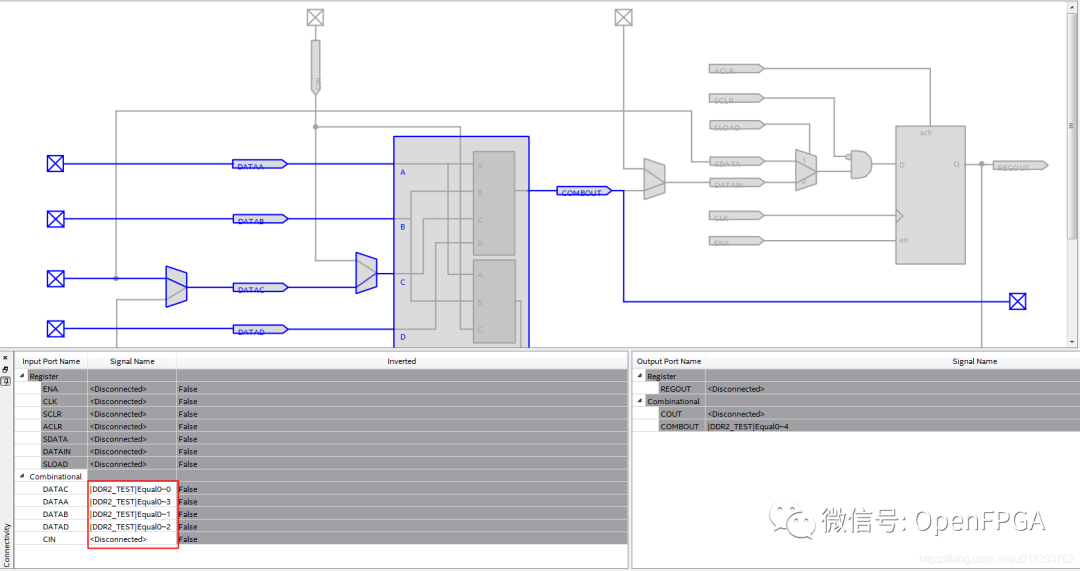

双击打开LE后内部的结构如下图所示,其中蓝色显示的是真实使用到的结构,灰色的是未使用到的结构,我们可以看到有两个输入和一个输出,与RTL代码的描述是对应的,红色框就是查找表LUT。

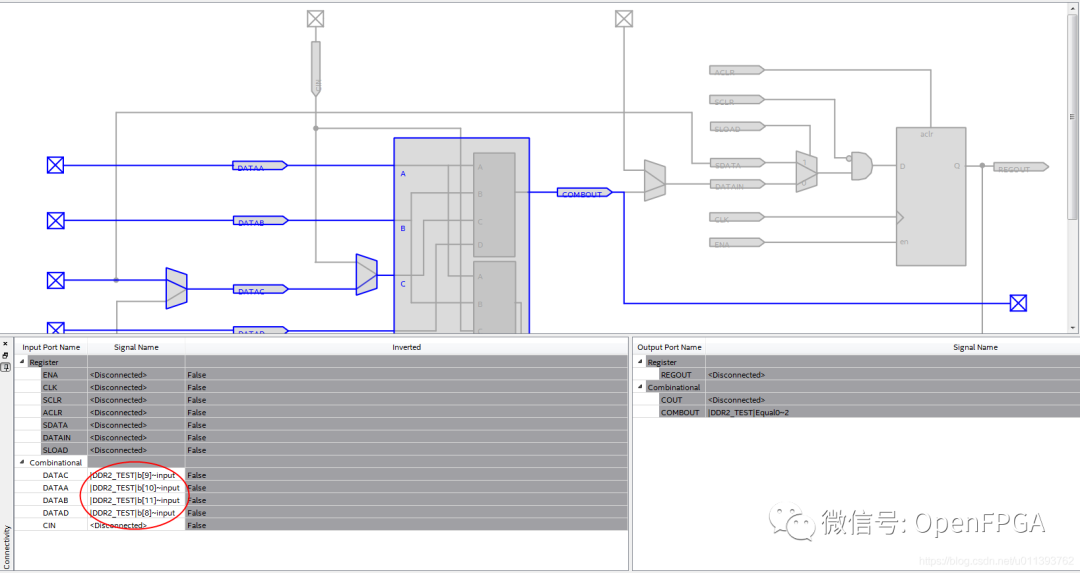

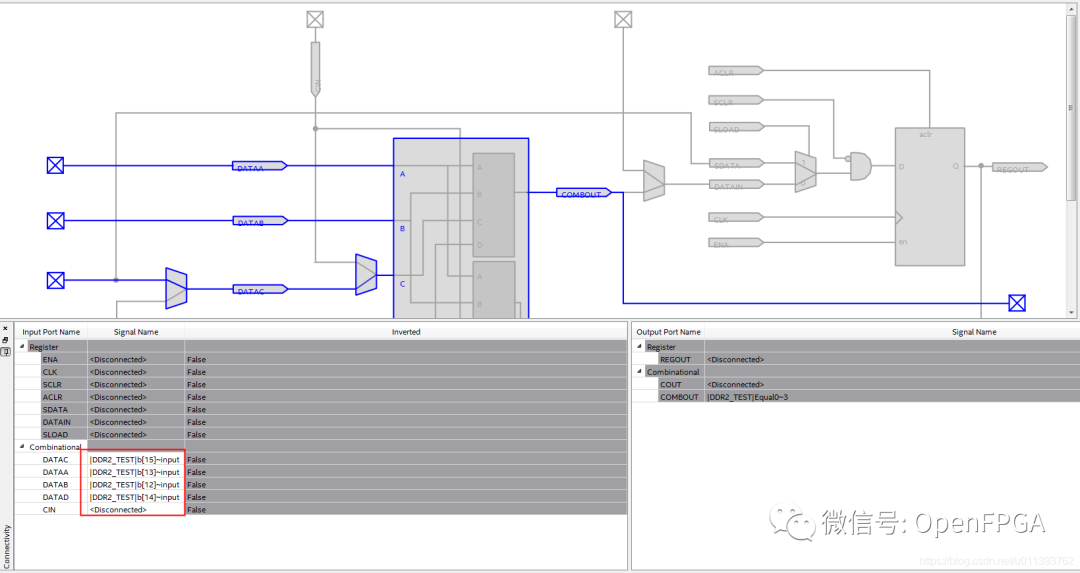

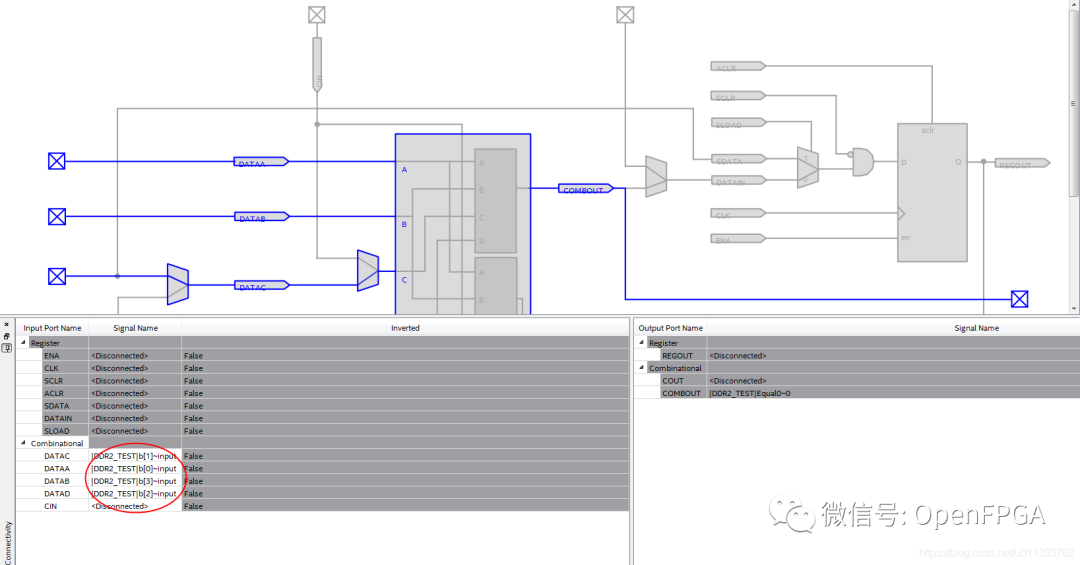

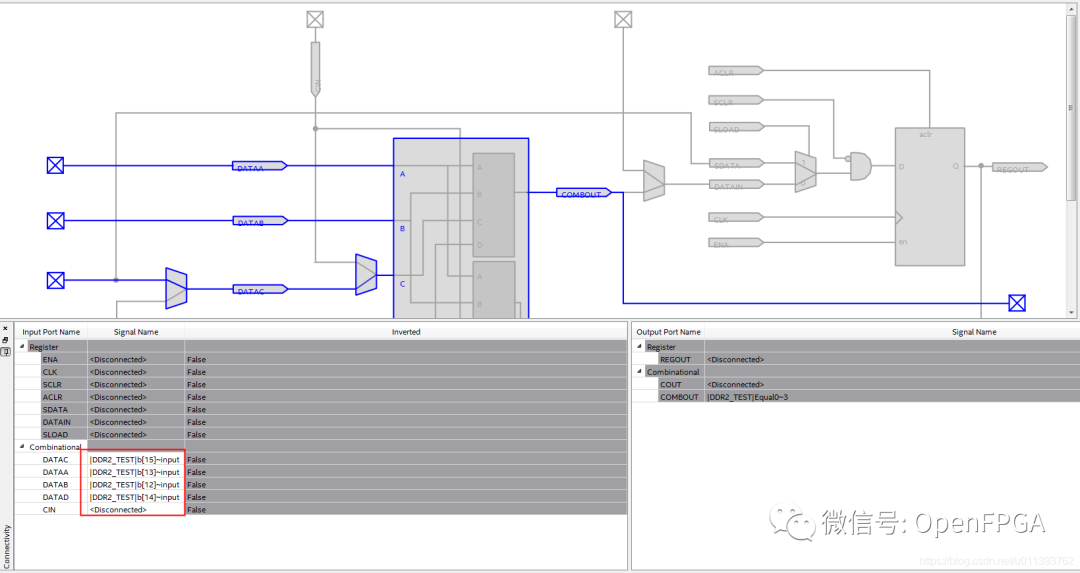

依次打开上图红色箭头标记的5个LE

可以看到前4个LUT是b[0]~b[15],第5个LUT是Equal,结合Chip Planner视图可以初步推理出,16bit的b每连续的4个输入用一个LUT,输出的结果传到第5个LUT。再结合Technology Map Viewer(Post Mapping)视图可知,前4个LUT其实是存储了0000_0000_1101_0101,也就是16’hd5这个值,然后每连续的4个一组,与输入分别比较,如果LUT的值与输入的值相等则LUT的输出为1,如果不相等输出为0,所以第5个LUT的内部输入名为“Equal”我们也就不难理解了。而第5个LUT存储了1111,当前4个LUT与输入的比较结果与第5个LUT中存储的值比较,如果相等则输出0,如果不相等则输出1。

选中第五个LE,点击Generate Fan-in Connection也可以显示出16bit的b每连续的4个输入用一个LUT,输出的结果传到第5个LUT

目前大部分FPGA都基于6输入LUT的(本例选用FPGA较老,是基-4 LUT),如果一个输出对应的判断条件大于四输入的话就要由多个LUT级联才能完成,这样就引入一级组合逻辑时延,我们要减少组合逻辑,无非就是要输入条件尽可能的少,这样就可以级联的LUT更少,从而减少了组合逻辑引起的时延。

例如:一个32位的计数器,该计数器的进位链很长(cnt《=cnt+32‘d1),必然会降低工作频率,我们可以将其分割成4位和8位的计数,每当4位的计数器计到15后触发一次8位的计数器,这样就实现了计数器的切割,也提高了工作频率。

文章来源:网络素材(侵删)

编辑:jq

-

如何理解Xilinx的RTL图2017-08-14 13014

-

使用的LUT触发器对的数量与Slice Register和Slice LUT的关系是什么?2018-10-23 12339

-

PAR报告中常用LUT-FF对的数量的较高比率是否意味着良好的设计?2018-11-01 4322

-

如何在LUT和逻辑元件之间以及逻辑元件和逻辑单元之间进行交换2019-01-08 2659

-

合成RTL时如何自由选择基于lut或mult18x18的乘法器2020-06-02 3586

-

一文带你了解步进电机的相关知识2021-07-08 2274

-

LUT与真值表有何关系2021-11-02 3702

-

一文解析sal socket与其他socket之间的关系2022-06-28 7326

-

深入剖析RTL与LUT之间的关系2022-10-14 3536

-

一文带你快速理解SPI总线系列2021-12-25 2093

-

关于FPGA四输入、六输入基本逻辑单元LUT的一点理解2023-05-25 4688

-

一文带你了解真正的PCB高可靠pdf.zip2022-12-30 474

-

一文读懂宽带、带宽、网速之间的区别与关系2024-01-31 12382

-

一文带你弄清DNS和域名之间的关系2024-08-21 1276

-

智慧公交是什么?一文带你详解智慧公交的解决方案!2024-11-05 1884

全部0条评论

快来发表一下你的评论吧 !