SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互转换过程介绍

今日头条

描述

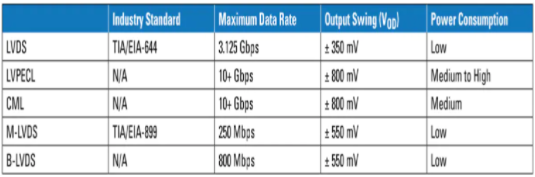

差分晶振一般用在高速数据传输场合,常见的有LVDS、LVPECL、HCSL、CML等多种模式。这些差分技术都有差分信号抗干扰性及抑制EMI的优点,但在性能、功耗和应用场景上有很大的区别。下图列举了最常用的几种差分信号技术和它们的主要参数。

下面讲一讲各信号模式之间的转换:

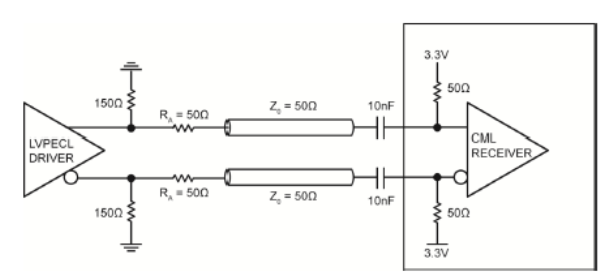

LVPECL到CML的转换

如图1所示,在LVPECL驱动器输出端向GND处放置一个150Ω的电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV LVPECL摆幅衰减到400mV的CML摆幅,需在150Ω电阻之后放置一个50Ω的衰减电阻(RA),以衰减LVPECL摆幅电平的一半。另外,必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置50Ω的端接电阻到VCC,用于CML偏置和传输线端接。

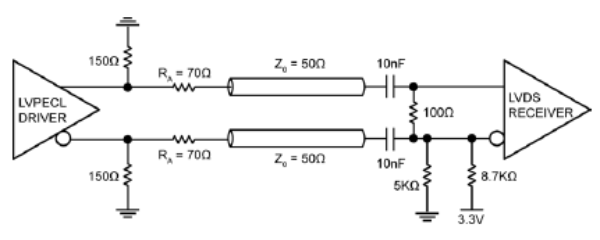

LVPECL到LVDS的转换

在LVPECL驱动器输出端向GND放置一个150Ω电阻,对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要(图2)。为了将800mV LVPECL摆幅衰减到325 mV LVDS摆幅,必须在150Ω电阻器之后放置一个70Ω的衰减电阻。应在LVDS接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。LVDS输入需要重新偏置,可以通过向GND放置8.7KΩ电阻连接到3.3V和5KΩ电阻到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

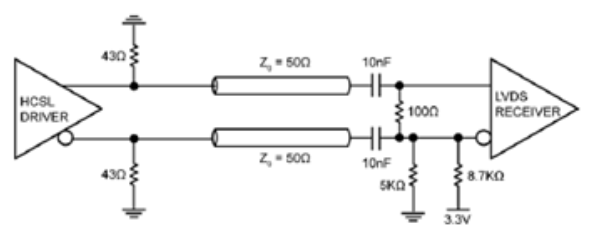

HCSL到LVDS的转换

在图4中,每个HCSL输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为48Ω,与50Ω并联,相当于23.11Ω。LVDS输入的摆幅为14mAx23.11Ω= 323mV。应在LVDS接收器前放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。放置交流耦合电容后,LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

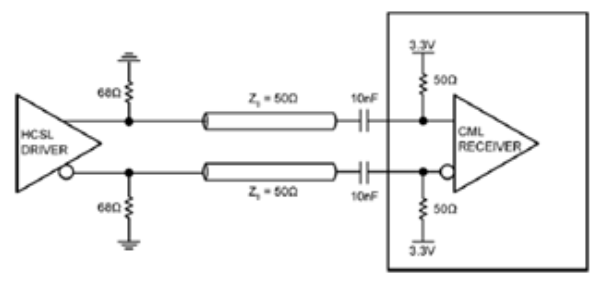

HCSL到CML的转换

在图5中,每个HCSL输出引脚在0和14mA之间切换, 当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为68Ω,与50Ω电阻并联,相当于28.81Ω。CML输入的摆幅为14mAx28.81Ω= 403mV。 应在CML接收器前面放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。另外,必须确认CML接收器输入内部的自偏置。如果没有CML输入端的自偏置,则必须在CML偏置和传输线端接的PCB上放置一个50Ω的端接电阻到VCC。

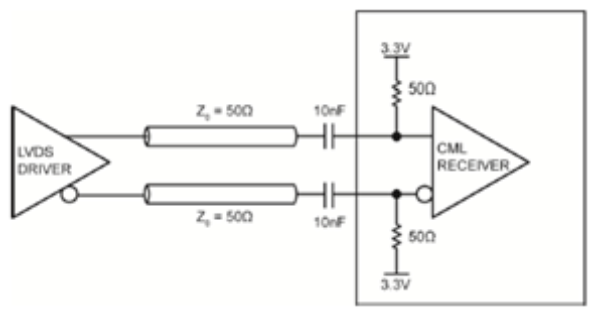

LVDS到CML的转换

LVDS输出通过100Ω电阻终端驱动±3.5mA电流,在CML接收器前面产生350mV摆幅电平(图6)。因为CML的标准摆幅是400mV,所以CML接收器能够接收350mV摆幅电平。此外,还必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置一个50Ω的电阻到VCC,用于CML偏置和传输线端接。

关于SiTime公司

SiTime 公司是全球领先的MEMS振荡器品牌,公司成立于2005年。在美国、荷兰、俄罗斯、乌克兰等全球多处设有研发中心,具有自己主知识产权的MEMS 谐振器晶圆在德国BOSCH生产,CMOS晶圆在中国台湾台积电生产。封装及测试有中国台湾日月光、马来西亚Carsem及新加坡UTAC。成立至今,已经开发具有独自专利的65种时钟产品种类,广泛应用于消费、工业、汽车、通信、航天航空等行业。

关于SiTime大中华区样品中心(简称:SiTime样品中心)

SiTime全硅MEMS振荡器已累计出货超过十亿片,越来越多的全球一流电子厂商正受益于SiTime所提供的优越价值,并一致认为SiTime是最优的时钟选择!

为更好的服务与支持越来越多的客户应用,SiTime公司与晶圆电子(Jointech)共同合作成立“SiTime样品中心”,并推出24小时急速样品服务。可提供免费样品、现货直采、替代选型、技术支持等服务!

ymf

-

差分晶振-LVPECL到LVDS的连接2025-03-12 2145

-

替代SiTime,国产差分硅振在光电转换器中的应用2024-09-11 1199

-

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换2022-11-21 1141

-

差分晶振有LVCMOS输出模式吗2022-07-07 3237

-

SiT9501:70fs超低抖动差分晶振,25-644.53125MHz,LVPECL/LVDS/HCSL2022-06-14 3301

-

SiTime差分晶振常见的信号模式解析2021-10-26 2249

-

求助LVDS电平转HCSL的转换电路2021-08-19 6823

-

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等2021-07-17 6666

-

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程2021-01-07 2143

-

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连2020-12-20 41476

-

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换2018-09-13 15312

全部0条评论

快来发表一下你的评论吧 !