Gen-3 C2000 F280025C外围电路和引脚配置详解

描述

作者:Dylan You

C2000 Gen-3对比于Gen-2的C2000,加入了三角函数运算单元来进一步提升运算能力,提供了更多的ADC模块及窗口比较器来增强采样和保护的快速性和灵活性。同时,在实时通信方面,引入了新一代快速串行通信接口Fast Serial Interface (FSI),可以支持在隔离的情况下最高200Mbps的数据传输速率。

本文主要讨论ADC通道的选择、FSI接口的应用、3.3V供电选型考量、GPIO口的配置和JTAG的连接与调试进行详细介绍。

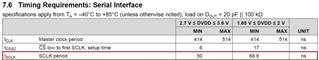

- ADC通道的输入寄生电容:

当我们在把外部信号匹配到C2000的ADC通道的时候,常常会忽略到ADC的输入模型可能会带来的潜在影响。其中最为明显的就是每个ADC通道上都会有一个输入寄生电容,而具有较大输入寄生电容的ADC通道通常是不适用于高频采样信号的。这是因为较大的输入寄生电容会带来更长的采样窗口,进而可能会影响到控制回路里的Computational power budget。如需了解更多信息,请参照 F28002X TRM的Choosing an Acquisition Window Duration 章节。

针对于Gen-3的F28002X的C2000, 我们可以在数据手册的ADC Input Model章节的表格Table 1 中查询到每一个ADC通道的内部输入寄生电容。基于Table 1,ADCINA3/ADCINC5通道不管是否启用了比较器,因为其内部输入寄生电容达到71.4pF,都是明显是不适合用于高速采样信号的。而对于ADCINA0/ADCINC15来说,如果使用了内部比较器,那么就需要慎重考虑采样窗口和外部采样电路。例如:如果我们希望使用某个ADC通道实现OVP功能的实现,而我们又只剩下了ADCINA0/ADCINC15这一个通道,那么我们可以利用软件代码在后台任务来实现OVP的功能,而无需使用内部比较器。如果我们一定要实现基于CMPSS模块的OVP功能,那么建议切换到其他到ADC通道。

Table 1: ADC 通道寄生电容

- FSI 接口介绍:

FSI接口是Gen-3的C2000引入的最新的高速可靠的快速串行接口。针对需要隔离的通信应用场景,FSI接收端模块具有一个可编程的Delay Line Control。通过对每一个线的RX_DLY_LINE_CTRL寄存器值进行修改,从而对系统元器件(例如信号缓冲器和隔离器等)引起的信号延迟和板级的(例如不均匀的布线等)引起的信号延迟进行补偿,最终保证信号的完整性,实现高速可靠通信。FSI是应用于点对点的的通信协议,例如单主/单从配置,所以FSI主要应用于以下两种场景:

- 两个MCU直接进行通信

- 板级之间的通信,例如PSFB的原边和副边的两个MCU通过隔离芯片来通信

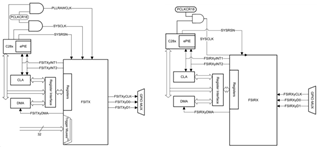

FSI接口的传输端(FSITX)和接收端(FSIRX)是完全独立的,每个端口有自己独立的寄存器、时钟和中断。而不同于IIC接口的一个重要区别是其只能作为单一方向的通信传输。基于Figure 1, FSI的每个端口有3个信号线,分别是时钟CLK,数据线D0和一个额外的数据线D1。额外的数据线D1是作为多线传输来加倍数据传输速率,也可作为GPIO口。所以,通常来说点对点的FSI需要至少4根信号线。FSI最大可支持的时钟频率为50MHz,而时钟的上升沿和下降沿也可作为数据的有效位判定。所以,理论上是可以达到最高200Mbps的传输速率。

Figure 1: FSITX/RX 模块连接图

在电机驱动和数字电源中,MCU之间进行实时通信越来越普遍,而这也对通信实时性的要求变高。FSI接口因为具有可编程的delay line control,可以确保隔离应用场景下高速通信且可靠,所以对比传统的UART、SPI和CAN等通信接口来说更具优势。

F28002X FSI 和IIC兼容GPIO口及隔离芯片:

如果我们要把F280025C 64pin作为副边的MCU和原边的MCU进行FSI通信,在工程师进行系统调试阶段,有时会希望通信接口既能作为FSI又能作为IIC通信。这个时候就会引入一些问题,例如IIC是双向通信,而FSI是单向的。针对F280025C 64pin,只有以下GPIO口既能支持FSI,又能支持IIC:

- GPIO33 >> I2CA_SCL and FSIRXA_CLK

- GPIO8 >> I2CA_SCL and FSITXA_D1

- GPIO0 >> I2CA_SDA and FSIRXA_CLK

- GPIO32 >> I2CA_SDA and FSIRXA_D0

- GPIO10 >> I2CA_SDA and FSITXA_CLK

首先,只有GPIO32是支持FSIRXA_D0的数据线。其次,只有GPIO33的FSI和IIC都是作为时钟使用。所以我们建议使用GPIO32/33作为接收端(RX)的数据和时钟线。

此外,在选择隔离器时,如果我们已经明确了通信方向,那么只要我们保持IIC和FSI的数据传输方向,那么依然可以使用单向的隔离器,例如ISO7742来传输数据。

- 3V供电电源芯片选择小细节:

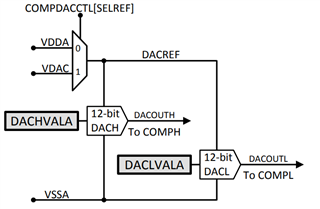

通常我们根据C2000的供电VDDA/VDDIO选择对应的前级DC/DC或者LDO时,更多会把重点放在输出电流能力、PSRR和压降等参数上,往往忽视了LDO的精度可能会带来的影响。针对C2000内部CMPSS模块的参考DAC模块,系统框图如下图。如果我们选择VDDA作为COMPDAC的参考电压,那么VDDA的任意百分比变化都会影响到COMPDAC的输出。所以通常针对峰值电流控制模式的DC/DC,推荐使用1%精度的LDO,例如TPS7A90。

Figure 2: C2000 CMPSS 模块的参考DAC部分框图

- GPIO口与外部信号的匹配:

- 三态(Tri-state)外部信号。例如外部信号Active的时候需要拉高,Sleep状态下需求拉低,IDLE模式需求Floating。那么我们有两种方式来处理,第一是通过将GPIO设置为输入,然后禁用上拉,第二种是将GPIO设置为输出和开漏,同时把GPIO电平设为低位。而这都可以通过C2000里面的GPAODR寄存器实现。

- 特定情况下,一些例如使能的数字口,如果不足以在低电平拉低,可以把其配置到模拟口。然后通过软件对模拟量的判断来实现高低电平的判断,从而实现使能和关闭使能。

数字GPIO口不够时的备选方案:

- 将原本作为风扇等其他小型设备的反馈电压(原边为数字信号)作为模拟GPIO口。然后通过软件代码基于采样电压来判断高低电平。

- Boot load的GPIO24和GPIO32如果是boot from flash,可以节省出两个GPIO口。如果是boot from SCI和CAN等的话,可以在boot结束后复用为其他GPIO口。

- JTAG接口连接及调试:

通常来说JTAG(IEEE标准 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture) 具有五个引脚:TMS/TDI/TDO/TCK/TRSTn。主要的三大功能如下:

- 下载软件到MCU的Flash

- 调试

- 边界扫描:访问芯片内部的信号逻辑状态以及芯片引脚状态等

通常针对JTAG连接出现问题的调试流程如下:

a) Power Good LED 开启:TI所有的C2000开发板都有LED来标识MCU的供电是否正常。

b) 检查Device Manager:使用JTAG仿真器和PC通信,我们首先需要安装好驱动文件。通常我们在安装CCS的时候会有具体细节。如需验证驱动是否成功安装,连接JTAG模拟器到PC并供电。然后在PC的Control Panel >> Device Manger 来定位到USB仿真器。

Figure 3: Device Manager 驱动确认

c) 检查MCU JTAG的TRSTn信号是否拉高:如果在CCS连接过程中,TRSTn没有改变状态,那么需要验证仿真器是否配置正常。

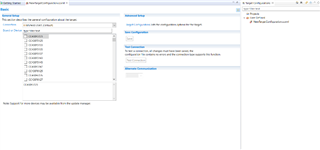

d) 检查Target Configuration:在Target Configuration File (.ccxml) 会包含连接Target device的所有相关信息以及JTAG仿真器的类型。在CCS中点击“View”,然后点击Target Configuration,找到User Defined下的 .ccxml 文件,就会显示处New Target Configuration 界面如下图。在下图中选择合适的Devices,保持配置,再点击测试连接即可测试连接是否正常。

Figure 4: Target Configuration 确认连接是否正常

e) 启动CCS调试。

f) 检查XRSn状态:如果XRSn的状态是低或者出现从低到高再到低的脉冲状态,那么可能是多种因素造成。例如如果是从低到高再到低的脉冲,那么可能是看门狗导致的重启。如果一直处于低电平,那么可能是因为供电或者PCB的其他的原因导致了Brown Out Rest (BOR)。

g) 检查Boot Mode:如果使用的是GPIO24和GPIO32默认的Bootload口,那么参照F28002X的TRM中3章节,检查GPIO24和GPIO32的引脚来确认是否在期望的Boot load 模式。

h) 检查VREG/时钟/系统时钟:测量并确认JTAG的时钟和晶振是否符合数据手册表明。测量并确认是否供电是否运行在了推荐电压值以外导致了BOR等问题。

参考文档:

-

C2000系统配置应用说明2024-09-14 457

-

使用C2000内部比较器替外部比较器2023-04-03 1705

-

Gen-3 C2000 F280025C外围电路和引脚配置详解2023-03-20 4275

-

Gen-3 C2000 F280025C外围电路和引脚配置介绍2022-11-04 853

-

基于F280025C controlCard和DRV8312-Kit的InstaSPIN FOC软硬件使用手册2022-11-03 998

-

基于F280025C controlCard和DRV8312-Kit的InstaSPIN FOC 软硬件使用指南2022-10-28 867

-

PCIe Gen-3高速前端卡参考设计2022-09-21 1465

-

C2000入门:C2000的基本知识介绍 (2)2019-04-15 5288

-

C2000入门:C2000的基本知识介绍(1)2018-08-14 14204

-

C2000的开发环境2018-08-10 4767

-

C2000入门:C2000的复位系统介绍2018-08-06 6392

-

C2000 LaunchPad原理图PDF文件32018-04-11 1300

全部0条评论

快来发表一下你的评论吧 !