运放输出钳位机理及避免办法汇总

描述

Other Parts Discussed in Post:LM358, LM358B

作者:Howard Zou

运算放大器是指一类专门通过改变外围器件可以实现不同算数运算的放大器。任何一颗运放都集成了非常多的晶体管,这些晶体管除了构成基本的工作电路,同时也会有实现输入输出电压钳位等保护功能。但是因为生产工艺的原因,在制造这些保证运放正常工作的晶体管的过程中,不可避免地会引入寄生晶体管和二极管。当运算放大器工作在规格书指定的工作范围内时,这些寄生晶体管不会对芯片的工作造成影响。然而,如果运放工作在超规格书的范围时,可能使得芯片的输出异常,进入输出钳位状态,从而影响电路的正常工作。本文以LM358为例,介绍其进入输出钳位状态的机理,同时提出避免芯片被钳位的解决办法。

一、运算放大器进入钳位状态的原理(以LM358为例)

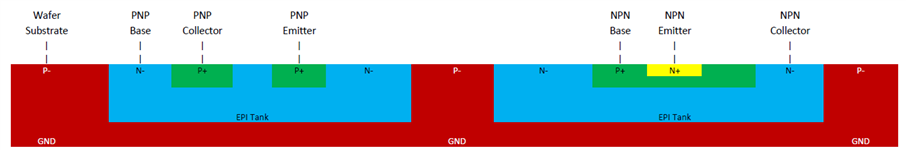

虽然各家厂商推出的运算放大器性能与规格互有差异,但是一般而言标准的运算放大器都包含下列三个部分。

1.差动输入级:以一差分放大器作为输入级,提供高输入阻抗以及低噪声放大的功能。

2.增益级:运算放大器电压增益的主要来源,将输入信号放大转为单端输出后送往下一级。

3.输出级:输出级的需求包括低输出阻抗、高驱动力、限流以及短路保护等功能。

图1. LM358内部架构图

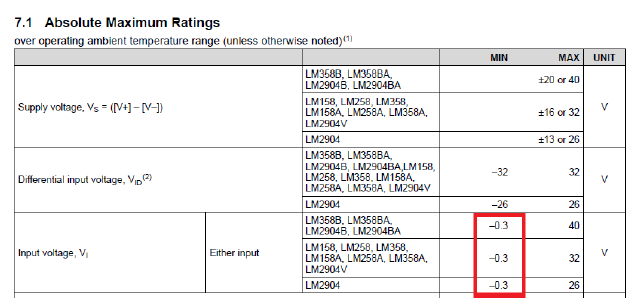

可以看到,所有电路的基本组成单元都是NPN管和PNP管,这些NPN和PNP管由连接到地的P基底隔开,如图2所示,这个基底将所有三极管隔离开。但是,如果LM358的输入端(PNP的base极)太低,低过P基底一个电压,那么这个偏置电压就会导致电流流经基底,而使得芯片无法正常工作。所以LM358的规格书会规定其输入电压的范围,比如最低不能超过-0.3V。

图2. 运放NPN和PNP管结构示意图

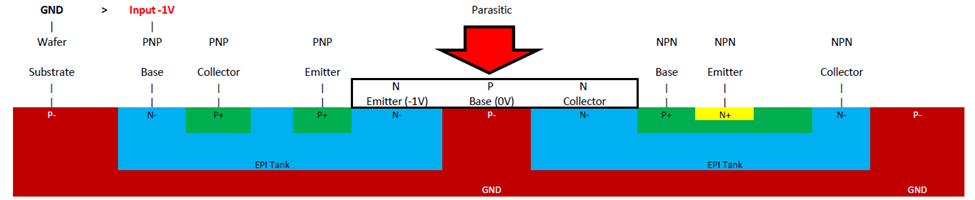

图3. LM358的最大电压范围

如图4所标注,PNP管的发射极,P基底和NPN管的集电极构成了一个寄生的NPN管,当运放的输入低于-0.3V时(比如-1V),寄生的NPN管的发射极比基极低-1V,这个电压足够使得寄生的NPN管导通,从而引起电流从集电极流向基极,这样,原本原本隔离开的两个晶体管之间就有了电气连接,同时与GND之间也有了电气连接,芯片将无法正常工作。

图4. 运放NPN和PNP管和基底构成寄生NPN管

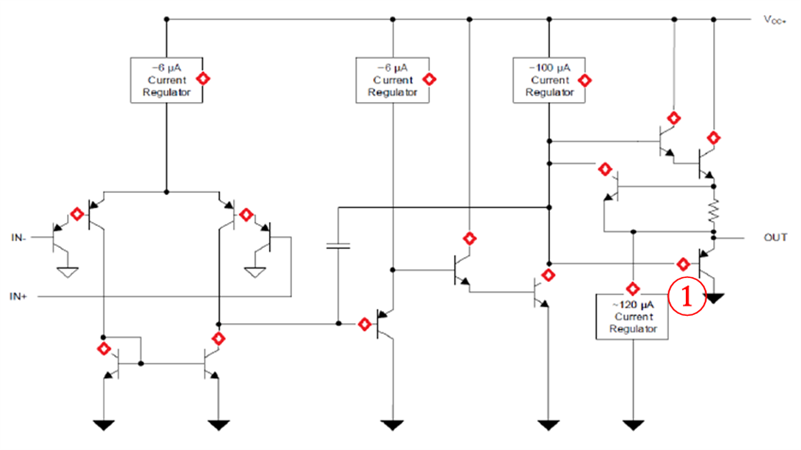

图5用红点标出了LM358所有可能有漏电流的点,以①点为例,当其对地有漏电流时,芯片输出端的PNP管将导通,从而使得芯片输出被钳位到低电平。

图5. LM358可能有漏电流的点

不同地点的漏电流会导致不同的运放输出状态,有些可能使得芯片输出为高,有些可能使得芯片输出为低。对于同样的输入,比如IN-输入为-1V,其引起的可能有漏电流的地方也随着芯片layout的不同而不同,一般离得越近的晶体管之间更容易引起漏电流,对于同一系列的芯片,比如LM358和LM358B,由于其裸片的layout不同,对于同样的输入超规格书使用,输出的钳位状态也不同。

二、钳位状态可能引起的问题及其避免方法

在实际应用过程中,绝大多数工程师都会避免输入信号的电压超过规格书规定的范围,但是,由于上电顺序的影响,运放很容易出现被测量信号比电源信号早上电的情况,从而导致芯片超规格使用从而进入钳位状态。

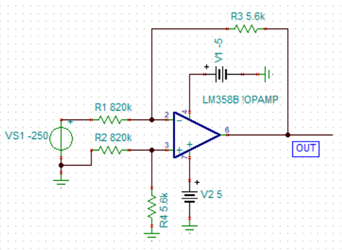

图6是一个常见的电压测量电路,LM358B由±5V供电,很容易可以推算出正常工作时Vout=VS1*(-R3/R1)=-250V*(-5.6/820)=1.71V。

图6. 电压检测电路

我们在实际电路中测量,发现实际运放的输出和芯片的上电顺序有关,如表1所示:

| LM358B | LM358 | |||

| 运放供电先于被测电压上电 | 运放供电晚于被测电压上电 | 运放供电先于被测电压上电 | 运放供电晚于被测电压上电 | |

| VOUT | 1.71V | -5.56V | 1.71V | 1.71V |

表1. LM358和LM358B输出实测值

可以看到,当运放供电先于被测电压上电时运放的输出都是正常的,这是因为在整个过程中芯片的输入电压都没有超过电源电压,从而符合规格书的应用范围。当运放供电晚于被测-250V电压上电,当被测电压上电而运放未上电时,运放的负输入端会有一个低于-0.3V的负电压,根据第一章的分析,可能会导致运放的输出钳位到正电源电压或者负电源电压。对于LM358而言,其输出被钳位到正电源电压,当供电电源上电后,+5V电源会通过输出端将LM358的输入端拉回正电压,从而使得芯片的输出恢复正常。而对于LM358B而言,其输出被钳位到负电源电压,当供电电源上电后,-5V电源通过输出端将LM358B的输入端拉到更低的电压(实测为-5.68V),这个电压比负电源低0.68V,输出始终被钳位到负电源电压附近无法恢复正常。

从上文分析可以看出,不同的钳位状态可能导致不同的输出,由于钳位状态和芯片的layout有关,我们无法预知一颗芯片的钳位状态,为了避免异常情况,针对输入电压可能先于电源电压上电的情况,我们可以:

1.人为控制上电顺序,保证在整个过程中不会出现输入电压超规格的情况。

2.在运放的输入端加对地钳位二极管,保证在任何上电顺序下运放的输入电压都不会超规格。

为了验证方法2,我们在LM358和LM358B的输入对负电源加入反向钳位二极管后实测的结果如下:

| LM358B | LM358 | |||

| 运放供电先于被测电压上电 | 运放供电晚于被测电压上电 | 运放供电先于被测电压上电 | 运放供电晚于被测电压上电 | |

| VOUT | 1.71V | 1.71V | 1.71V | 1.71V |

表2. 加入钳位二极管后LM358和LM358B输出实测值

三、结论

1.运放的输入电压超过规格书可能导致运放内部寄生晶体管产生漏电流,从而导致芯片的输出钳位到正电源或者负电源。

2. 不同的钳位状态可能导致同一电路出现不同表现,有些可以正常工作而有些不能。

3. 运放的钳位状态和芯片裸片(DIE)的layout有关,即使是同一系列的运放也可能有不同的layout从而导致不同的钳位状态,因为芯片裸片的layout是不公开信息,我们无法预知运放的钳位状态。为了避免运放因为输入超规格导致工作异常,我们可以在输入端对正负电源加钳位二极管,避免运放输入超规格,从而保证电路的正常工作。

References

[1]. LM358 DATASHEET (SLOS068X)

[2]. Latch-Up, ESD, and Other Phenomena (SLYA014A)

-

运放的噪声评估简单办法及举例2023-05-31 1418

-

如何测量运放的输出电压2023-02-01 6449

-

运算放大器输出钳位的机理及避免办法2022-11-07 942

-

运放输出钳位机理及避免办法2022-10-28 758

-

运放正反馈加二极管组成迟滞比较器(钳位运放的输出)的原理?2021-06-24 11255

-

运算放大器通俗讲解 运放LM358进入钳位状态的原理与问题避免办法2021-01-11 6925

-

运算放大器进入钳位状态的原理及引起的问题和避免方法2020-12-14 2756

-

请教关于运放输出噪声测量问题2019-07-19 4737

-

运放的参数和选择的汇总2018-02-09 16718

全部0条评论

快来发表一下你的评论吧 !