简述高性能全集成逐次逼近寄存器型模数转换器

描述

Sunny Qin

由于拥有较高的分辨率和采样率,SAR型ADC一直被众多工业和汽车客户所亲睐。但是SAR型ADC由于其特殊的特性,所以对外围电路也相应的提出很多“特殊需求”。

首先就是抗混叠电路的需求。例如当电路中的SAR型ADC采样率为fs时,根据香浓采样定律,输入信号的频率需要小于fs/2,频率超过fs/2的信号将会通过混叠效应“混入”有用信号频带中,并且无法区分。因此,为了避免混叠的问题,绝大部分SAR型ADC电路需要在前端设计专用的多阶有源滤波器,滤掉频率超过fs/2的信号。(注:Σ-Δ型ADC理论上也需要抗混叠滤波器,但是由于其过采样特性及内部数字滤波器的带外衰减特性,其对抗混叠滤波器的设计要求要低很多,多数情况下一阶RC电路能够满足抗混叠需求。)

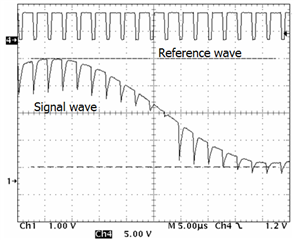

其次是模拟输入与基准输入的驱动问题。不同于大学课本上讲到的,现在市面上流行的大部分SAR型ADC不再是通过分压电阻网络来实现电压的逐次逼近,由于CMOS工艺的普及,取而代之的是通过内部电容网络实现电荷的逐次逼近,这样无论是ADC的信号输入端还是基准输入端,都是通过一个电容采样,这个电容一般为几个皮法到几十个皮法。这样带来的两个新的问题就是:1,我们能否在采样的短暂时间内将这个电容完全充满;2,这个电容在采样瞬间是否会把我们信号瞬态拉低。(具体的SAR ADC驱动设计请参考SLAA571A:Design Challenges and Improvement Techniques for SAR ADC Driver Circuit)。糟糕的驱动设计会导致无论是输入信号,还是基准信号都会被瞬态拉低,并且造成采样误差,如下图所示:

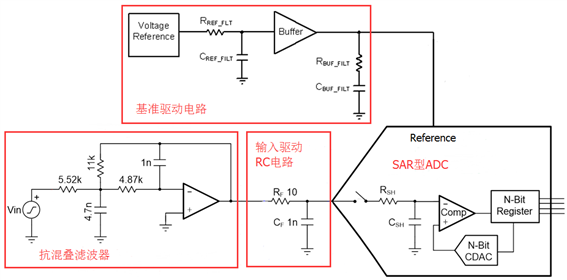

所以标准的SAR型ADC驱动电路需要基准及驱动电路,抗混叠滤波器,输入驱动电路等三个部分,其电路结构如下:

除了上述的两个关键问题以外,SAR型ADC采样电路往往还需要配备电压基准,模拟开关,输入放大及直流偏置电路(交流信号无法直接被单电源ADC采样)等,复杂的系统设计往往会另工程师们望而却步。

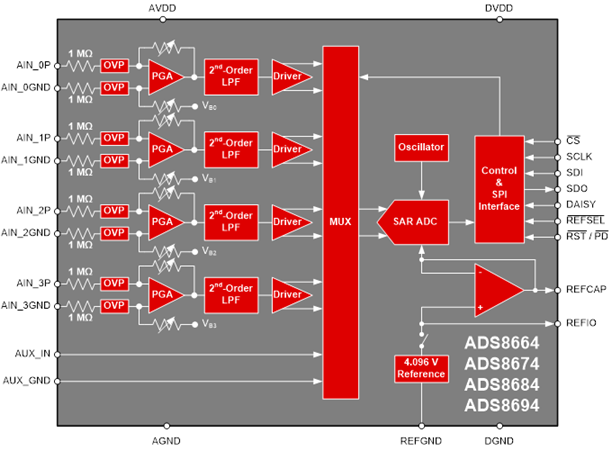

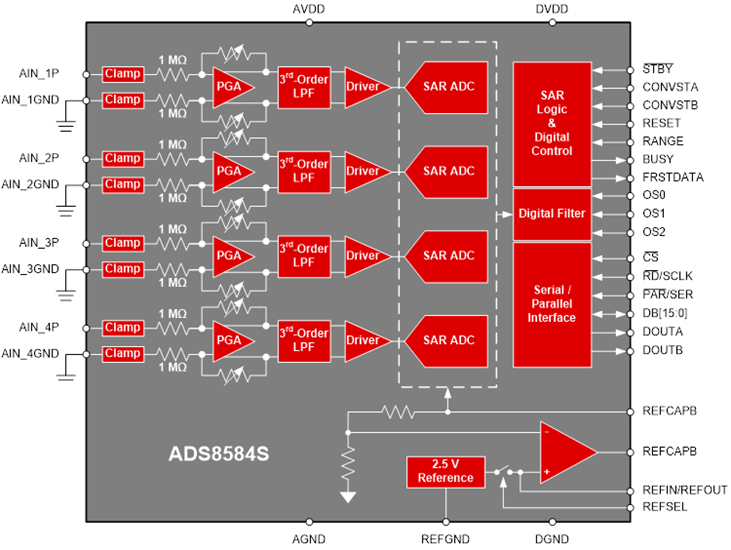

针对于这一问题,现TI开发出一系列全集成式SAR型ADC, 其集成了高阻抗输入可编程放大器,抗混叠滤波器,ADC驱动电路,模拟开关以及高精密电压基准等,并且能在单电源供电环境下提供±10V/ ±5V/ ±2.5V等可编程输入范围。高集成度的设计使得这种ADC更像一块电压采集器,大大简化采样电路的设计,同时TI提供极具竞争力的价格,以便众多工业客户选用。其结构框图如下:

非同步型全集成ADC

同步型全集成ADC

这种全集成型的ADC大大简化了电路设计,同时优化了成本。针对于这一类全集成型ADC,TI提供多种型号,涵盖不同分辨率,不同通道,同步/非同步等多种器件。下面表格中罗列了全系列高集成度SAR型ADC,以及相应的资料及参考设计TI-Design,欢迎各位工程师点击查看。

注:TI绝大部分器件都会有参考设计,我们叫做TI-Design,每一份TI-Design中都包括参考手册, 原理图,PCB,软件代码,测试结果,以及BOM表,用户可以在TI官网免费下载。

审核编辑:金巧

-

ADS9120逐次逼近寄存器(SAR)模数转换器(ADC)数据表2024-07-31 708

-

ADS8863逐次逼近寄存器(SAR)模数转换器数据表2024-07-27 410

-

逼近型模数转换器特点和应用2024-07-22 1896

-

模数转换器:并行比较型和逐次逼近型2024-01-23 5382

-

12位高速逐次逼近寄存器(SAR)模数转换器(ADC)2023-09-25 635

-

高性能全集成逐次逼近寄存器型模数转换器2022-10-31 695

-

14位逐次逼近型模数转换器ADCMAX1033资料推荐2021-03-26 1389

-

如何逐次逼近寄存器 (SAR) ADC?2021-03-11 3010

-

贸泽电子开售Analog AD7386逐次逼近寄存器模数转换器2020-03-02 1528

-

逐次逼近寄存器型模数转换器输入的注意事项2017-11-16 1573

-

逐次逼近寄存器(SAR)型模数转换器输入需要注意些什么?2017-04-18 1719

全部0条评论

快来发表一下你的评论吧 !