UCD9090A-TI电源时序控制器在5G MIMO中的应用

今日头条

描述

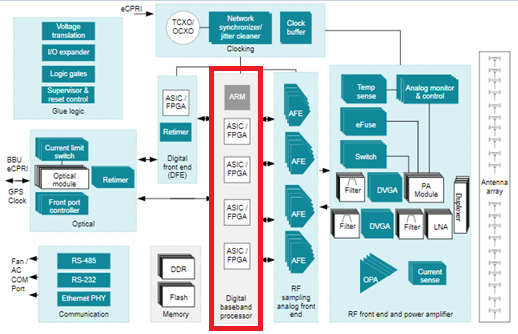

5G是目前通信设备领域的市场趋势, Massive MIMO指的是64T64R应用中常用的多输入和多输出, 更多的发送器和接收器通道需要更多的数字处理器(FPGA / ASIC)来执行数据传输,而典型的64T64R MIMO应用中通常需要4-5个数字处理器。 每个FPGA都需要自己的电源上电/下电的时序,以便FPGA能够正常工作。 在下面的图1中,是典型的64T64R Massive MIMO框图,4颗 ASIC / FPGA用于与4颗 RF采样模拟前端(AFE7799)进行通信和控制。

Figure 1: Massive MIMO 框图

TI UCD90xx系列包括多个轨道选择,从10个通道到32个通道,温度范围支持高达125C,非常适合用于通信设备领域,特别是在5G Massive MIMO应用中。

UCD90xx系列是一款数字电源时序器,无需写软件,并使用TI Fusion Digital Power Designer GUI配置时序。 硬件工程师更容易通过GUI设计电源时序列器而无需写代码。 此外,TI还提供培训视频,指导工程师如何将Fusion Digital Power Designer与UCD90x排序器配合使用,以便工程师可以快速掌握使用TI Fusion数字电源设计器的知识。

UCD90xx系列以非常小的解决方案尺寸集成了全功率监控,电源时序和故障记录,可帮助服务器和通信设备客户实现一体化芯片解决方案,同时具有设计灵活性和提高系统可靠性的优势。

如何设计以UCD9090A给Xilinx Zynq Ultrascale FPGA系列的电源轨供电时序控制

1)了解上电/掉电时序要求

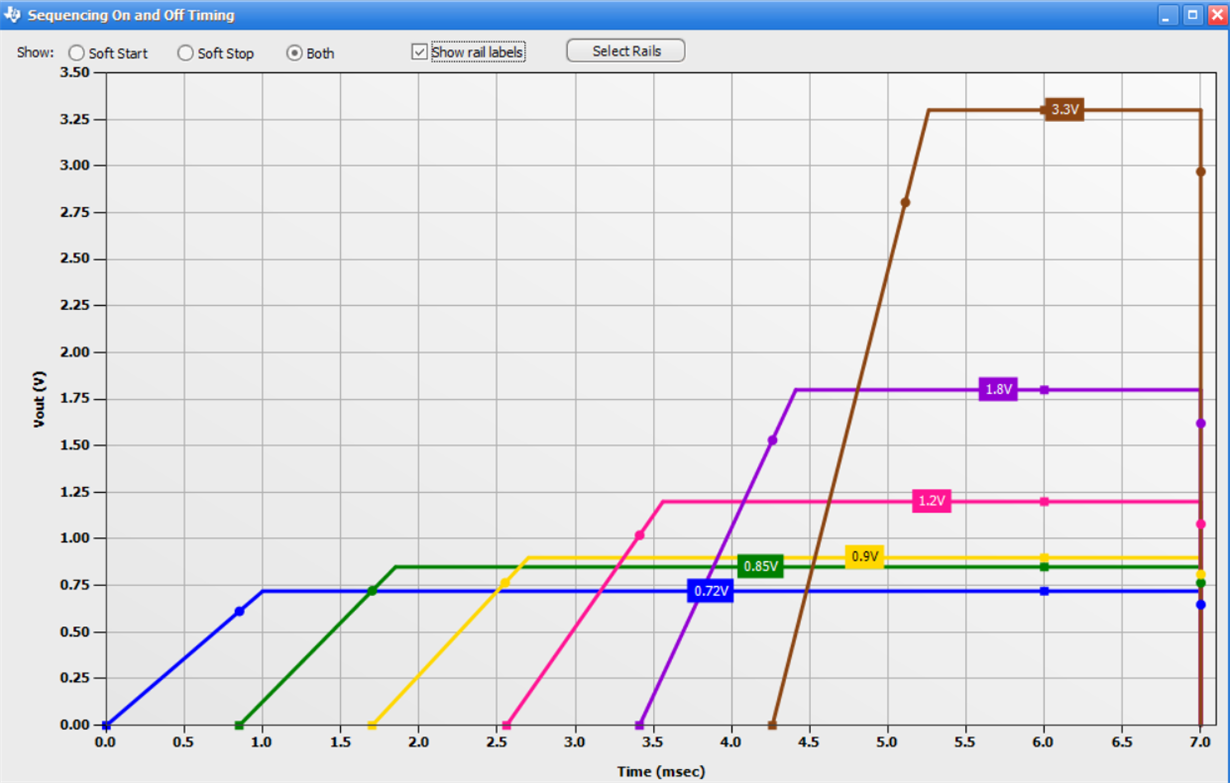

上电时序:0.72V - > 0.85V - > 0.9V - > 1.2V - > 1.8V - > 3.3V

掉电时序:3.3V - > 1.8V - > 1.2V - > 0.9V - > 0.85V - > 0.72V

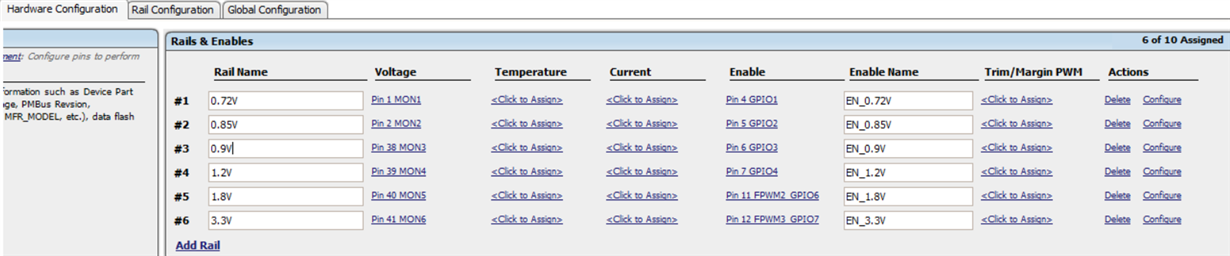

2)定义电源轨和使能名称

Figure 2: 电源轨和使能

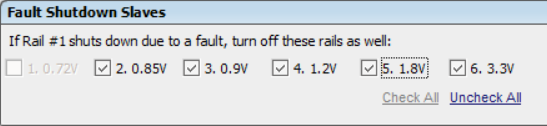

3)设计故障关闭,对每个电源轨的上电和掉电时序的依赖关系和故障响应进行时序。在电源轨配置(电源轨#1,0.72V)时序故障时的操作选项中,点击其他电源轨,这意味着如果电源轨0.72V由于故障而关闭,则关闭这些点击的电源轨。

Figure 3: 发生故障时的操作

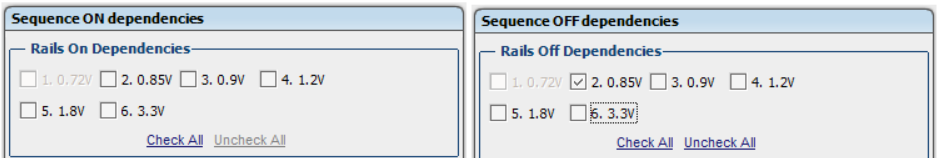

点击0.85V掉电时序依赖关系,这意味着电源轨 0.72V断电时序依赖于0.85V的Power Good的电压低于正常水平就会触发0.72V掉电时序。

Figure 4: 上电/掉电时序的依赖性

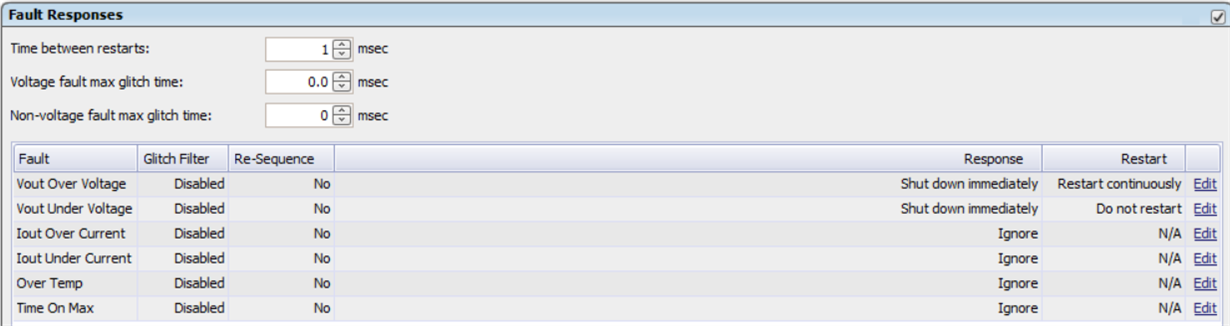

在故障响应选项中,将响应更改为“立即关闭”和重启为“不重启”,这意味着当故障发生时,它将立即关闭轨道并且不会重新启动该特定轨道。 这个基于设计要求来定义,如果需要重启可以改为“连续重启”。

Figure 5: 故障响应

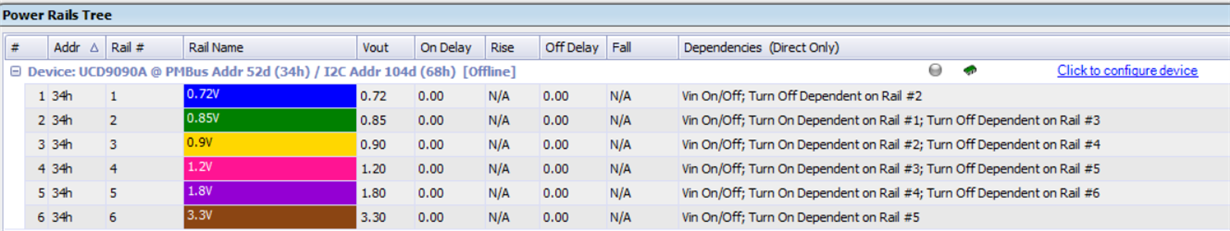

4)检查电源轨和时序图

Figure 6: 电源轨

Figure 7: 上电和掉电时序

TI UCD90xx系列是服务器和通信设备应用中的最佳解决方案,它将监控,时序和故障记录集成到一个芯片方案中。 TI Fusion数字电源设计器GUI可帮助硬件工程师节省写软件的工作并缩短设计周期。

编辑:fqj

-

德州仪器UCD9090A:10轨电源排序与监控的理想之选2026-02-26 195

-

UCD9090A 10轨电源时序器与监控器(支持ACPI)技术文档总结2025-08-19 1218

-

支持 ACPI 的 10 轨电源排序器和监视器UCD9090A数据表2024-03-29 411

-

基于UCD9090A给Xilinx ZynqUltrascale FPGA系列的电源轨供电时序控制2022-11-09 789

-

UCD9090A-如何使用TI电源时序控制器在5G MIMO的应用2022-10-31 579

-

通过TI电源时序控制器在5G MIMO应用的通信和控制2020-12-01 2848

-

5G MIMO天线的耦合减小技术2019-07-17 7315

-

UCD9090A UCD9090A 支持 ACPI 的 10 轨电源序列发生器和监视器2019-04-18 789

-

采用 UCD9090 实现 K2E 的电源排序2015-04-08 2510

全部0条评论

快来发表一下你的评论吧 !