高精度数模转换器 (DAC) 中的输出干扰源

今日头条

描述

作者:Tony Calabria 德州仪器

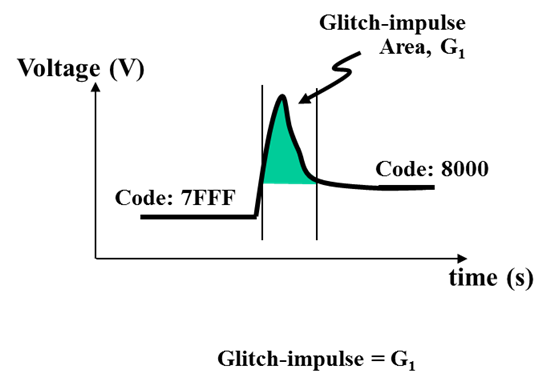

在上一篇 DAC 基础知识博文中,我们对高精度数模转换器 (DAC) 中的输出干扰源进行了探讨。若您希望在增加代码的过程中获得线性转换,那么这些输出脉冲可能会扰乱系统运行。让我们快速回顾一下我在上篇博文中介绍的干扰脉冲情况:

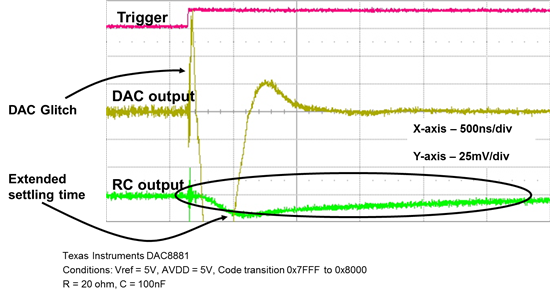

DAC 输出干扰的“能量”由脉冲(以绿色显示)的宽度和高度定义。可根据系统要求对干扰的形状进行很好的控制。在 DAC 输出的后面添加一个简单的 RC 滤波器能够减小干扰的幅度,但会增加建立时间,而干扰“能量”(曲线下面的区域)保持不变。下面以 DAC 通过主要进位转换阶段为例,展示了 RC 滤波器之前和之后的输出。

应通过观察干扰周期并提前 10 个单位左右选择截止点 (cutoff point) 来为 RC 滤波器选择适合的电阻与电容比。在选择组件值时,应使用较小的电阻值以避免电阻负载上产生较大的压降。电容值可根据所选的电阻值和所需的 RC 比率进行确定。

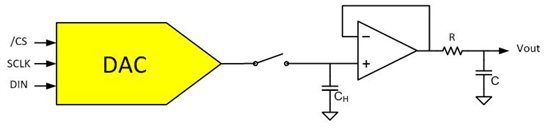

降低干扰的另一种方案是使用跟踪与保持放大器。这种方法比较麻烦,因为需要严格的开关定时和外部组件,会导致成本和板级空间增加。

通过使用外部开关、一些无源组件以及放大器,您能够完全去除 DAC 输出干扰,但同时会出现来自新 S/H 开关的小瞬态信号。可利用一阶低通滤波器级来减弱这种新的短小瞬态信号。基本原理图如下所示。

系统设计结构非常简单明了。当 DAC 通过主要进位转换阶段时,开关打开。这就是出现干扰的地方。一旦电压转换完成,开关就会闭合,并为 CH 采样电容器充电以达到所需值。当 DAC 再次更新其输出时,随着外部开关打开电容器会继续保持新的电压值。这样您在理论上就可以完全消除干扰,且不会增加建立时间。

下面是这两种解决方案的优缺点:

- 如果系统可以容许增加建立时间,并且需要降低干扰脉冲的幅度值,那么简单的 RC 滤波器就足够了。

- 如果系统需要完全消除干扰,则可采用跟踪与保持放大器解决方案。

当然,另一种选项是为了避开 R-2R DAC,而采用电阻串 DAC 解决方案进行设计则可用避免出现较大干扰。应注意,这样做可能会让您不得不对其它 DAC 规范进行权衡。

如果您是第一次阅读 DAC 基础知识系列,并对我们的博文感兴趣,那么您一定要阅读我们之前发表的博文:

阅读原文, 请参见http://e2e.ti.com/blogs_/b/analogwire/archive/2013/07/01/dac-essentials-glitch-be-gone.aspx

-

基于LTC2757的高精度数模转换器电路设计2023-11-08 336

-

数模转换器的精确度2022-11-22 581

-

介绍DAC数模转换器以及DMA的使用2021-08-12 3371

-

数模转换器是什么2021-07-26 3211

-

高精度数模转换器TQ6124芯片的性能特点、结构与应用分析2020-08-11 3266

-

3PEAK高精度数模与高速模数转换器2019-04-26 4773

-

消除干扰2018-09-14 2735

-

数模转换器的高精度2018-09-13 2372

-

用SPICE仿真高精度数模转换器2018-09-12 2107

-

数模转换器:消除干扰的两种方式及优缺点2018-07-10 5315

-

如何用SPICE来仿真高精度数模转换器?2018-04-20 10723

-

高精度数模转换器AD420及其与MSP430的接口技术2016-02-17 1057

-

选择高精度数模转换器2011-06-28 1493

全部0条评论

快来发表一下你的评论吧 !