如何优化DSP功率预算

描述

作者:Timothy Hegarty 德州仪器

鉴于内核、存储器、I/O 以及其它电轨的过多电压电流要求,多核 DSP 实施需要智能电源管理。DSP 内核电压电源的一个重要性能基准就是能够根据DSP 使用情况及环境条件实时调节 VCORE。VCORE 命令一般以数字格式提供,电源应能随时解读。VCORE 电轨一般具有最大的电流规范,而能够平衡效率与尺寸的小型电源解决方案也很重要。关键在于在 DSP 与模拟 PWM 级之间使用低成本接口来实现这一电压识别 (VID) 功能。

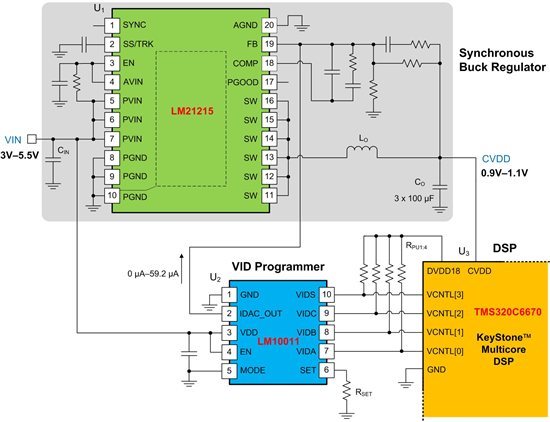

因此,下图提供了将内核电轨标示为 CVDD 的多核 DSP 加以说明。同时,我也在《EDN》杂志上发表了一篇题为《通过调节稳压器优化 DSP 功率预算》的文章,深入探讨这一主题。

一个额定电流为 15A 的 500KHz 降压转换器负责为 CVDD 供电。该设计可使用连接至 VID 编程器的 4 线数字接口实现 VID 控制,其可直接连接至任何模拟功率级或控制器。点击这里观看 VID 编程器的视频演示。

KeyStone DSP与VID功能同步降压转换器的原理图

LM10011与模拟PWM功率级

LM10011 不仅可采集出现在 DSP VCNTL 接口上的 VID 信息,而且还可设置连接至功率级电路反馈 (FB) 引脚的电流 DAC 输出。在 6 位模式下,既提供支持 940nA 分辨率的 64 种电流设置,又提供优于 1% 的误差精度。在本例中,CVDD 由 DSP 判定为一个电压介于 0.9V 至 1.1V 之间的电平,支持 6.4mV 的步进分辨率。无需电平转换器或胶合逻辑,电阻器 RSET 可决定启动时的 CVDD 电压。LM10011 可与任何具有 FB 输入的电压、电流或 DCAP 模式 PWM 调节器连接。

欢迎大家尽情讲述在您设计 DSP 电源解决方案时遇到的其它问题。

阅读原文,请参见: http://e2e.ti.com/blogs_/b/powerhouse/archive/2013/10/03/how-to-optimize-your-dsp-power-budget.aspx

编辑:jq

-

优化DSP功率预算的方法2022-11-23 501

-

如何优化 DSP 功率预算2022-11-07 655

-

如何通过调节稳压器优化DSP功率预算2021-11-22 2035

-

教你们如何优化DSP功率预算2021-03-15 2594

-

怎么优化嵌入式DSP设计中的功耗?2019-10-08 1840

-

嵌入式DSP设计中的功耗优化怎么处理2019-06-24 1612

-

如何优化DSP功率预算2018-09-20 1923

-

如何通过调节稳压器优化DSP功率预算?2018-07-18 891

-

DSP程序优化总结2017-10-23 631

-

调节稳压器优化 DSP 功率预算2017-04-18 1339

全部0条评论

快来发表一下你的评论吧 !