怎么样把总谐波失真保持在10%以下

描述

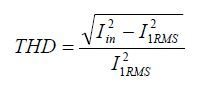

LED 照明领域普遍关注的问题一直是如何将总谐波失真 (THD) 保持在 10% 以下。电源不但可作为非线性负载,而且还可引出一条包含谐波的失真波形。这些谐波可能会对其它电子系统的工作造成干扰。因此,测量这些谐波的总体影响非常重要。总谐波失真可为我们提供信号 w.r.t. 基波分量中谐波含量的相关信息。更高的 THD 就意味着出现在输入电源端的失真越大或电源质量越低。

因此,我不得不使用 15 W 射灯(绝缘)设计来测试一个设计方法,该设计方案采用针对 7 个串联 LED 配置的 TPS92314 器件,可通过 150 ~ 265V AC 输入提供 3.1V 正向电压和 0.7A 额定电流。按照下列指示,我在 240V 的 AC 输入电压下实现了 8.7% 的 THD。

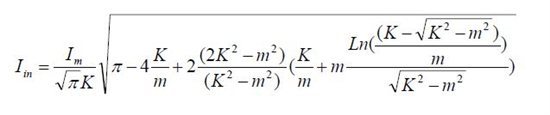

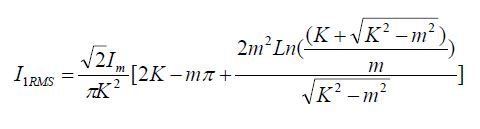

在进行实际实施之前,请查阅本应用手册,了解完成该测试所需的两个重要方程式。

在本例中,k 等于 1.68,我们可通过上述方程绘制出当 k = 1.68 时 THD 与“m”的关系曲线图。

因此,重新看一下“m”和“k”的定义,我们就会发现,增大匝数比(n = Np/Ns)及转换器延迟时间,可降低 THD。除这两个参数外,EMI 滤波器设计也可对 THD 的改善起到非常重要的作用。用来降低总谐波失真的三个设计注意事项包括:

增加变压器匝数比 (n = Np/Ns) 可增大反射电压。这会提高成本和开关 FET 的电压应力。在本特例中,我们将匝数比调成近似于 10,以保持反射电压约为 174V。FET 额定值必须高于过冲电压、(LED 最大电压+ 输出二极管压降)× 匝数比加上峰值 AC 输入电压的总和。计算结果将近 640V [= 50 V + (20 + 0.5) * 10 + 1.414 * 265]。我使用的是 700V 额定 FET 以及约为 16pF 的低漏源极电容。

增加转换器延迟时间可降低 THD。我将电阻器从计算的 5.6k 变为 6.2k。延迟时间取决于变压器的初级线圈电感以及 FET 的漏源极电容。所得延迟时间约为 280ns。

在输入端添加 EMI 滤波器。在本例中,将带有 275V AC、68nF 电容器的 80mH 共模线圈添加至输入端,并在该桥接之后添加一个包含 1mH 鼓电感器和两个 400V、33nF 电容器的 π 滤波器。这可帮助我们实现 2.15 kHz 的差分滤波器转角频率。在线路阻抗稳定网络和频谱分析仪的帮助下,我在查看传导 EMI 曲线后,在多次迭代中计算这些值。在最初没有任何线路滤波器的情况下,峰值在 100 kHz(转换器开关频率)下约为 85dBuV。该频谱已经超出了 CISPR 15 B 类标准的限值,直到频率为 1MHz 时才降至限值以内。因此不得不采用 EMI 滤波器。我逐步增加共模线圈值,并观察其对 THD 性能的影响(将电容器增大到一定程度后会降低 PF 性能)。最后,该值达到了 80mH 和 68nF 左右,而截止频率则为 2.15 kHz,衰减超过 30dB,使 100 kHz 下的峰值降至 55.78dBuV。这样,频谱不仅下降了,而且它还使灯光达到了 CISPR 15 标准(符合准峰值和平均限值两种要求)。进行这一改变后,THD 改善至大约 9 ~ 10%。与共模线圈相关的漏电感帮我实现了差分滤波器。

通过进行上述改变,我才得以在 240V 的输入电压下实现 8.5% 的 THD 以及 0.98 的 PF,输出电压为 21.8V。在相同设计中的输出端(18.8V 输出)使用六个 LED,我们在 240V 电压下实现了 9% 的 THD。通过 EE1685 磁芯(匝数 180)实现了 80mH 的 EMI 滤波器。主变压器的初级电感为 2mH,峰值主电流约为 0.5A。

本次测试使用的 LED 驱动器是 TPS92314,这款一次侧控制离线 LED 驱动器主要用于低成本照明应用(少量外部元件)。它具有恒定导通时间架构,无需复杂的补偿技术就可实现自然功率因数校正。此外,谐振谷值开关也可减少 EMI,提高系统效率。其它优异的特性还包括逐周期一次侧电流限制、VCC 过压保护及欠压锁定、输出 LED 过压保护以及控制器关闭等。

责任编辑:haq

-

如何测量总谐波失真以及所使用的功率因数计算2023-02-21 11153

-

如何将总谐波失真 (THD) 保持在 10% 以下?2022-11-23 873

-

如何将总谐波失真降至 10% 以下2022-11-07 838

-

将LED总谐波失真降至10%以下的方法2022-04-13 8120

-

谐波失真的危害,总谐波失真怎么计算?2021-03-11 5340

-

如何把RST保持在高水平?2020-06-19 1205

-

如何将总谐波失真降至10%以下2018-09-20 3319

-

总谐波失真和噪声曲线详解2018-09-12 4007

-

LED照明如何将总谐波失真降至10%以下?详细方法概述2018-07-18 2096

-

使用15W射灯设计来测试总谐波失真2018-03-26 6544

-

如何将总谐波失真(THD)控制着10%以下?2017-04-18 33024

-

理解总谐波失真和噪声曲线2017-04-12 6098

-

影碟机的总谐波失真2010-01-04 1018

-

什么是总谐波失真2009-12-21 1314

全部0条评论

快来发表一下你的评论吧 !