RFID软件产业化仍显薄弱 急需解决

处理器/DSP

描述

RFID软件产业化仍显薄弱 急需解决

0 引 言

TMS320DM642是TI公司推出的一款高性能的数字多媒体处理器,具有二级存储器和高速缓冲器,以及超长指令字结构。其运算速度快、体积小、功耗低的优点使得它在多媒体处理领域得到了广泛的应用。开发基于FLASH引导DM642的应用系统,在系统上电后,系统的自动引导机制将FLASH中的应用程序自动加载到片内RAM中去运行。但是,由于自动引导机制只能将片外FLAH中的1 KB代码加载到RAM中。这就要求必须开发能够将应用程序全部加载的引导程序,即二级引导程序。

1 DM642的引导方式

DM642主要有三种引导方式:

(1)不加载。CPU直接开始执行地址0处存储器中的指令。如果该处存储器是SDRAM,CPU会先挂起,直到SDRAM初始化完成。

(2)ROM加载。位于外部CE1空间的ROM中的1 KB程序首先通过DMA/EDMA被搬入地址0处。尽管加载过程是在芯片从复位信号被释放以后才开始的,但是当芯片仍处于复位时,就开始准备上述传输了。传输完成后,CPU退出复位状态,开始执行地址0处的指令。ROM中的程序存储格式应当与芯片的端点模式一致。

(3)主机加载。核心CPU停留在复位状态,芯片其余部分保持正常。外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。所有初始化工作完成后,向接口控制寄存器的DSPINT写“1”,结束引导。CPU退出复位状态后,从地址0处开始执行指令。

在基于DM642的应用系统中,主要采用ROM加载的引导方式,通过外挂FLASH芯片,将应用程序存储在FLASH中。系统断电后应用程序依然存在,使得系统能够脱机运行。并且,借助于二级引导程序,基于DM642的大规模应用程序的开发也将更加方便、灵活。

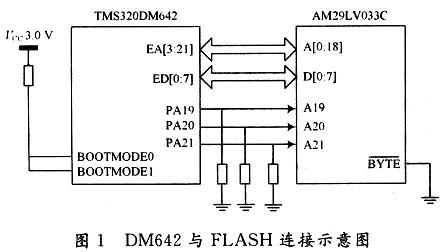

2 DM642与FLASH的连接

在本文中,DM642采用TI公司的TMS320DM642AGDK,FLASH采用AMD公司的AM29LV033C。

TMS320DM642的工作时钟最高可以达到720 MHz,处理性能可达5 760 MIPS,其通过外部存储器接口(EMIF)访问片外存储器。EMIF接口分成四个空间,即CE0~CE3。FLASH映射到CE1空间,上电时采用8位ROM加载方式。AM29LV033C是一款4 M×8 b,3 V单电源供电的非易失存储器。

CE1子空间配置成8位异步静态存储器接口连接FLASH,由于DM642的外部地址总线只有20根,所以CE1的最大寻址范围为1M×8 b。CE1只将前一半寻址空间分配给FLASH,后一半空间分配给了其他资源,即最大可寻址范围是512K×8 b。为了寻址FLASH的所有空间,可对FLASH进行分页管理,将FLASH分成8页,由位于CPLD中的页地址寄存器通过PA19,PA20,PA21控制选页。DM642与FLASH的连接示意图如图1所示。

用分页技术寻址FLASH所有空间,FLASH的每一页均映射到CE1的相同地址空间(0x90000000~0x9007FFFF)。在二级引导程序进行引导的过程中,每当FLASH当前页到达页末时,通过页地址控制寄存器改变PA19,PA20,PA21的输出电平来激活下一页,完成引导过程。在本文中,以基于DM642的视频采集、编码和传输程序为例,详细说明DM642的二级引导程序的设计过程。

3 二级引导程序

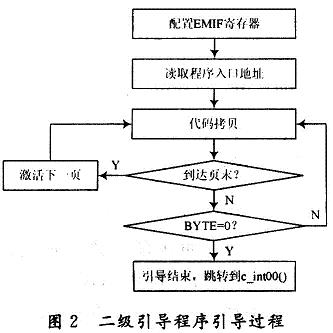

3.1 引导过程

二级引导装载程序被放置在FLASH的起始地址处,一旦DSP上电复位,二级引导程序就会通过DM642的自动加载机制加载到RAM的地址0处,且此时CPU复位,开始执行二级引导程序。二级引导程序的引导过程为:首先对EMIF寄存器进行配置,包括全局控制寄存器、CEx空间控制寄存器、SDRAM控制寄存器、时序控制寄存器以及扩展控制寄存器等。然后,获取程序入口地址,接着按照数据块的格式获取每个块的字节数和目标地址,开始拷贝代码。当获取的字节数为0时,引导结束,CPU跳转到C_int00处,建立C语言运行环境,从main()处开始执行。引导过程如图2所示。

3.2 二级引导程序设计

根据二级引导程序的引导过程编写二级引导程序的实现代码,二级引导程序用汇编语言编写。下面是各部分的具体实现。

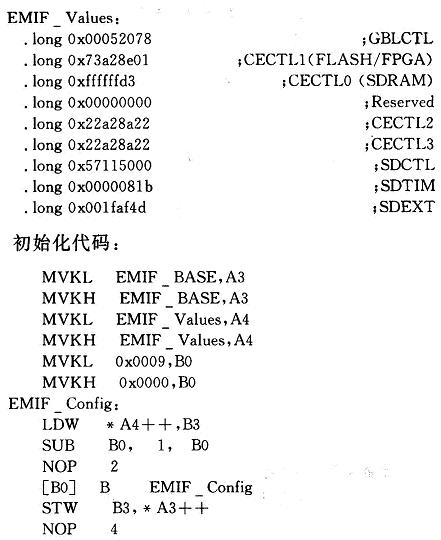

(1)配置EMIF寄存器。定义EMIF寄存器基地址EMIF BASE="0x01800000",定义各个寄存器的配置值为:

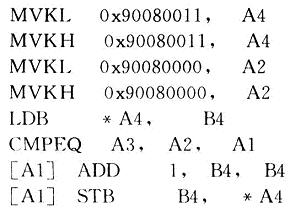

(2)拷贝应用程序代码。定义引导表的地址为COPY_TABLE=0x90000400,实现代码如下:

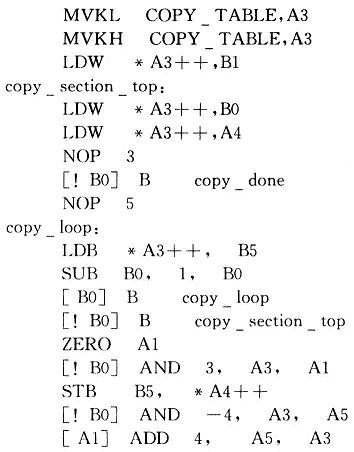

(3)判断是否到达页末的代码。页地址控制寄存器的地址为0x90080011。在代码拷贝的过程中,时刻判断加载指针是否指向下一页的开始,如果是,则返回到0x9000400,如果不是,则继续拷贝。实现代码如下:

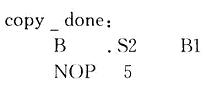

(4)执行跳转。代码拷贝完成后,引导结束,执行跳转指令。代码如下:

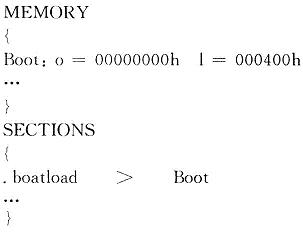

另外,必须编写相应的命令文件以配合引导程序完成引导过程。在本例中,将二级引导程序放在.boat-load段中,并在命令文件中添加如下代码:

4 实验结果

将二级引导程序的汇编文件加入实际工程中,并且在命令文件中为二级引导程序申请相应的内存空间后,编译、连接生成可执行文件(.out)。然后,通过hex6x转换工具将可执行文件转换为CCS可加载的数据文件。

建立CCS仿真环境与DM642开发板的连接,通过CCS仿真平台,将数据文件烧写到FLASH中。烧写完成后,断开开发板与CCS的连接,加电测试程序能够正常运行。

5 结 语

本文介绍了DM642的FLASH分页引导的二级引导程序的设计方法,并给出部分实现代码。实践证明,该方法是可行的。这为基于DM642的实际应用开发提供了一个途径。

- 相关推荐

- 热点推荐

- RFID软件

-

华为徐直军:打造中国软件产业发展的黑土地2018-07-02 6889

-

中国高清传输标准DiiVA的产业化趋势和设计挑战2010-03-25 3379

-

政策驱动RFID产业快速发展2011-12-14 4244

-

氢燃料电池实现产业化还远吗?2017-02-07 4498

-

汽车电子嵌入式软件产业集群2019-07-17 2665

-

数控产业发展的关键之控制软件产业化2021-07-01 2354

-

中国芯片设计公司怎样在显控、工业物联网、边缘计算和新零售等新兴应用中加速产业化进程2022-09-27 1629

-

探讨轮毂电机产业化的发展思路2023-03-01 1303

-

深圳嵌入式软件成软件产业火车头2006-03-13 845

-

PC显卡急需解决的HDCP兼容性问题2009-11-07 4495

-

自动驾驶产业化提速的动力是什么2019-06-27 1030

-

芯片产业链全景梳理:EDA软件最薄弱2020-12-01 10952

-

中国工业软件产业发展存在的十个矛盾2022-12-02 1756

-

世强硬创入选深圳软件产业扶持计划2024-12-02 1107

-

2024 中国(南京)软件产业博览会盛大开幕,共绘软件产业新蓝图2024-12-24 356

全部0条评论

快来发表一下你的评论吧 !