运算放大器测量CDM新方法

描述

输入电容可能会成为高阻抗和高频运算放大器(op amp)应用的一个主要规格。值得注意的是,当光电二极管的结电容较小时,运算放大器的输入电容会成为噪声和带宽问题的主导因素。

运算放大器的输入电容和反馈电阻在放大器的响应中产生一个极点,从而影响稳定性并增加较高频率下的噪声增益。因此,稳定性和相位裕量可能会降低,输出噪声可能会增加。实际上,以前的一些CDM(差模电容)测量技术依据的是高阻抗反相电路、稳定性分析以及噪声分析。这些方法可能会非常繁琐。

在诸如运算放大器之类的反馈放大器中,总有效输入电容由 CDM与负输入共模电容(或对地的CCM–)并联组成。CDM难以测量的原因之一是运算放大器的主要任务是防止两个输入不相关。与测量CDM的难度相比,直接测量对地的正输入共模电容 CCM+相对容易一些。在运算放大器的同相引脚上放置一个较大的串联电阻并施加正弦波或噪声源,就可以使用网络分析仪或频谱分析仪来测量由运算放大器输入电容而产生的-3dB的频率响应。假定CCM+与CCM–相同,特别是对于电压反馈放大器。

但是,这些年来,测量CDM变得日益困难;运算放大器的固有特性会迫使其输入相等,从而自举CDM, 因此所使用的各种不同的技术都无法令人满意。当输入被强制分开并进行电流测量时,输出将试图进行对抗。检测CDM的传统方法是间接测量,该方法依赖于相位裕度的降低,且因并联使用CCM–等其他电容而变得更复杂。

LT1792

经过 100% 全面测试的低电压噪声:6nV/√Hz (最大值)

A 级器件经过 100% 的全面温度测试

电压增益:1,200,000 (最小值)

整个温度范围内的失调电压:800μV (最大值)

增益带宽乘积:5.6MHz (典型值)

提供了采用 ±5V 电源时的保证规格

我们希望待测运算放大器能够像客户平时的用法一样,在闭环条件下正常运行并执行功能。建议的一种可行方法是分离输入并进行输出削波,但是这可能会使内部电路无法工作(取决于运算放大器拓扑),因此实测电容可能无法反映实际工作电容。在这种方法中,不会对输入进行过度分离,以避免输入级的非线性以及过多的输出摆幅或削波。本文将介绍一种简单直接的CDM测量方法。

测量CDM新方法

只使用增益为1的缓冲电路,并使用电流源激励输出和反相输入。输出和反相输入将仅在运算放大器允许的范围内变动。在低频下,输出的变动很小,因此通过CDM的电流会很小。而在过高频率下,测试可能会无效,况且结果也没用。但在中频下,运算放大器的增益带宽会下降,但不至于太低,输出变动仍可提供足够大的电压激励和可测量的通过CDM的电流。

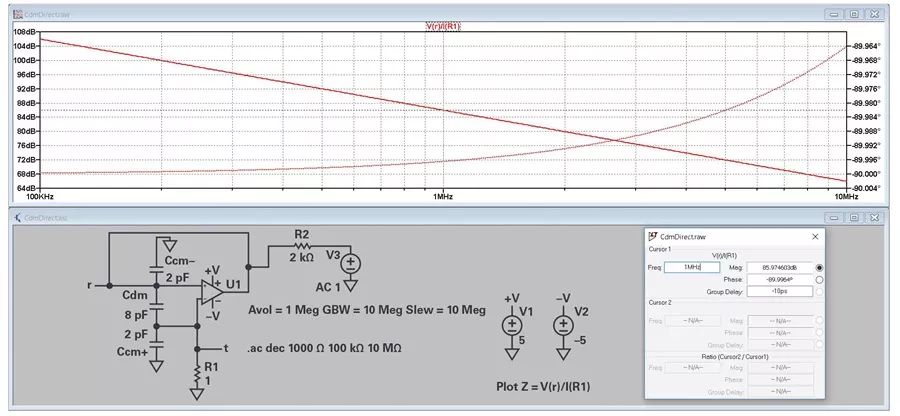

LTspice的本底噪声几乎不受限制,因此可以进行简单的测试仿真,如图1所示。当发现该技术在LTspice中相当准确有效后,接下来的问题就是“我可否在现实世界中获得足够的SNR以进行良好的测量?”

图1. 直接测量LTspice中的 CDM阻抗。绘制V(r)/I(R1)曲线以获得阻抗。在本例中,在1 MHz频率下,-89.996°时Z为19.89437kΩ (10(85.97/20)), 利用公式C = 1/(2π × Z × Freq),Z正好为8 pF。

T该相位角几乎等于-90°,这表明阻抗是容性的。2pF共模电容不会破坏测量,因为CCM–不在路径中,且1/(2×π×Freq×CCM+)》》1Ω。

挑战:找到合适的设备和实际测试设置

如图1所示,将2kΩ电阻串联在运算放大器的输出端,以将激励从电压源转换为电流源。这将允许节点“r”中存在小电压(它不会与在运算放大器的同相引脚中所看到的电压相差太远),并将导致小电流流入待测CDM的输入端之间。当然,现在的输出电压很小(由待测器件(DUT)进行缓冲),而且CDM中的电流也很小(在本仿真中为57nA),因此在工作台上使用1Ω电阻进行测量将很困难。LTspice.ac和LTspice.tran仿真没有电阻噪声,但现实世界中的1Ω电阻具有130pA/√Hz的噪声,从我们预期的57nA 电容电流中只能产生57nV信号。进一步的仿真表明,用50Ω或1kΩ代替R1不会导致在目标带宽范围内的频率下流入CCM+的损耗电流过大。为了获得比简单电阻更好的电流测量技术,可使用跨阻放大器(TIA)代替R1。TIA输入会连接到运算放大器的同相引脚,在该引脚上需要电流,同时电压固定为虚地以消除CCM–中的电流。事实上,这正是Keysight/Agilent HP4192A等四端口阻抗分析仪的实现方式。HP4192A可以在5Hz至13MHz的频率范围内进行阻抗测量。市场上采用相同阻抗测量技术的一些新设备包括具有10Hz至120MHz范围的E4990A阻抗分析仪和具有20Hz至2MHz范围的精密LCR表(如Keysight E4980A)。

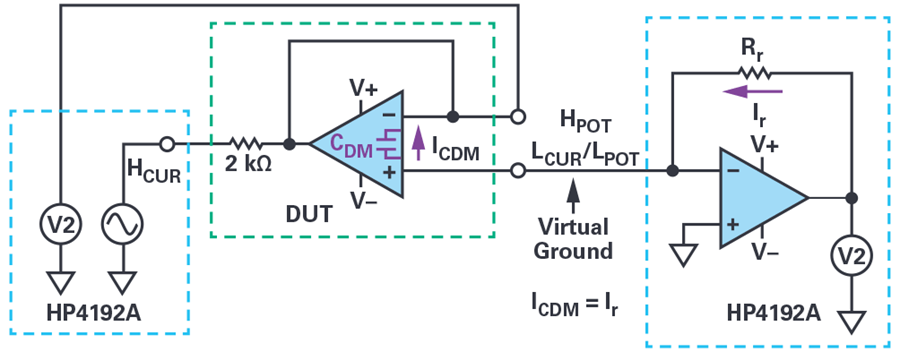

如下面图2测试电路所示,由于阻抗分析仪内部的TIA,运算放大器的同相引脚保持虚地状态。正因如此, CCM+的两个端子都被视为处于地电位,因此不会影响测量。DUT的CDM两端产生的小电流将流经TIA的反馈电阻Rr然后由内部电压表进行测量。

图2 CDM测试电路。

任何使用自动平衡电桥阻抗测量方法的四端口设备都是测量CDM的合适选择。它们设计为从内部振荡器产生正弦波,该内部振荡器以零为中心点,具有正负摆幅,可用于双电源供电。如果运算放大器DUT由单电源供电,则应调整偏置功能,以使信号不会发生对地削波。图3中使用了HP4192A,并显示了与DUT的详细连接。

图4显示了确切的测试设置,以使电路板和连线对CDM的寄生电容贡献极小。任何通用电路板均可用于低速运算放大器,而高速运算放大器则需要更严格的PCB板布局。垂直接地的铜分隔板能确保输入端和输出端看不到与 DUT CDM平行的其他场路径。

结果与讨论

首先,在测量电路板的板电容时没有使用DUT。图4所示电路板的测量条件是16fF电容且没有DUT。这是一个相当小的电容,可以忽略不计,因为通常CDM的预期值为几百至几千fF。

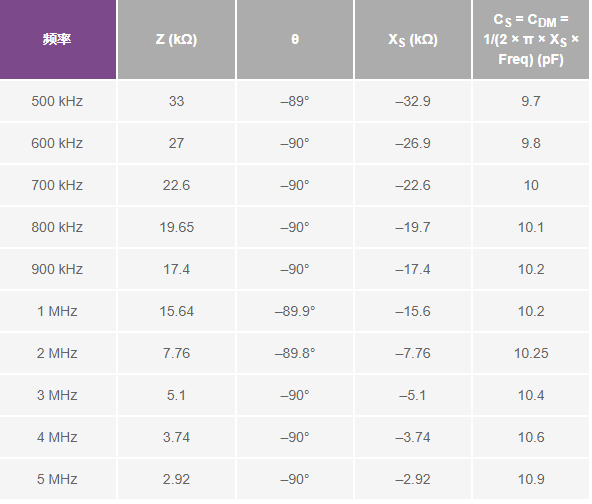

使用这种新的CDM测量技术,可以测量大多数JFET和CMOS输入型运算放大器。为了说明该方法,以测量低噪声精度JFET运算放大器LT1792为例。下表列出了在一定频率范围内的阻抗(Z)、相位角(θ)、电抗XS和 CDM的计算值。当相位角为-90°时,阻抗表现为纯容性。

表1. 电源为±15 V时,LT1792在不同频率下的阻抗测量

上述表1给出了在500kHz至5MHz频率范围内的测量结果。在该频率范围内的相位接近于纯容性(相位角为-89°至-90°)。同时,电抗XS决定了总输入阻抗,即Z≈XS。CDM的计算平均值约为10.2pF。最高测量频率为5MHz,因为该器件带宽仅可达5.6MHz。更低频率下 的结果变得非相干。推测这是由于运算放大器的行为使输出电压降低,CDM电流迅速消减,同时XS阻抗在低频时变大。

还应在每个阶跃频率处检查运算放大器的输出,以确保它不会被阻抗分析仪产生的信号过驱。来自HP4192A的该信号的幅度可在0.1V至1.1V范围内调节,这刚好足以在运算放大器的输出中产生摆动,并使反相输入引脚中的电压电平略微发生变动。图5显示了频率为800kHz时,运算放大器输出端的峰峰值无失真信号(绿色信号)为28mV。2.76V峰峰值幅度(1Vrms)的黄色信号是直接从分析仪的振荡输出端口探测得的。公平起见,可以任意决定不允许输出失真,不论是对DUT还是对HP4192A检波器。尽管该设置相对来说并不受探头效应的影响,但在获取阻抗和相位的实际数据时已经将探头移除。

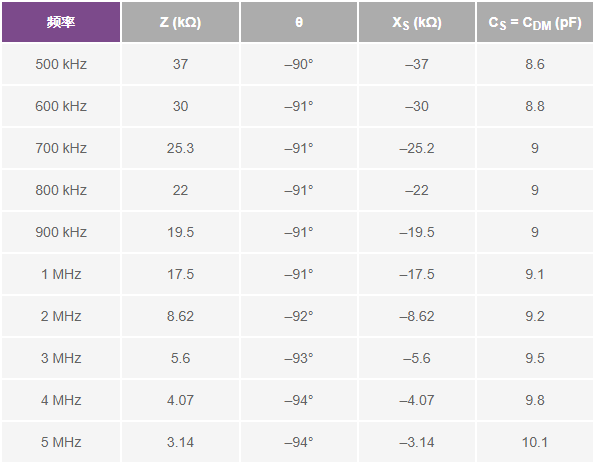

我们进行了在不同电源电压下测量CDM的测试。CDM对电源和共模电压的依赖性会随运算放大器的不同而有所不同;不同的拓扑和晶体管类型预计会导致高压电源和低压电源不同的结寄生效应。表2给出了电源稳定在±5V范围内LT1792的结果。CDM的测量平均值为9.2pF,与采用±15V电源时的结果10pF相当接近。因此,可以得出结论,LT1792的CDM不会随电源电压的改变而发生显著变化。这与其CCM形成了鲜明的对比,后者会随电源电压发生显著变化。

表2. 电源为±5 V时,LT1792在不同频率下的阻抗测量

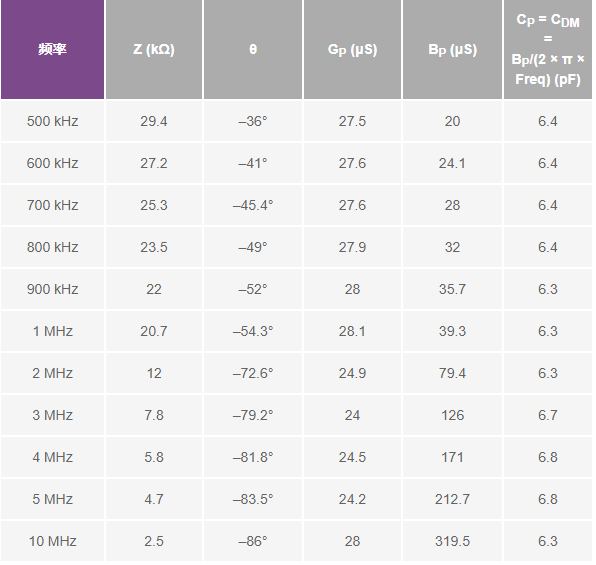

同时,双极性输入运算放大器几乎与其FET同类产品一样简单。但是,由于它们与CDM电流并联,因此它们的高输入偏置电流和电流噪声较为明显。此外,双极性差分对输入内在的固有差分电阻RDM也与CDM并联。表3以低噪声精密放大器ADA4004为例,显示了其阻抗测量。显然,相位并不表示纯容性行为,因为它远离-90°。尽管4MHz、5MHz和10MHz频率非常接近,但并联等效阻抗RC模型将适合本例,以便能够从其他电阻中提取出CDM。因此,表3中显示了在一定频率范围内的并联电导GP, 电纳BP和CDM的计算值,其中假定CPP等于CDM。

表3. 电源为±15 V时,ADA4004在整个频率范围内的阻抗测量

根据表3中的结果,可以估算出ADA4004的CDM约为6.4pF。结果还表明,在表3所示的整个频率范围内,CDM具有相当大的并联电导GP,并非纯容性CDM。测量显示该双极性运算放大器的实际输入差分电阻约为40kΩ(1/25μS)。

附注:我们尝试了对其他类型运算放大器进行测量,例如零漂移运算放大器(LTC2050)和高速双极性运算放大器(LT6200)。结果非相干,推测原因是零漂移运算放大器中的开关伪现像以及高速双极性运算放大器中的过大电流噪声。

参考结论

测量CDM并不困难。需要注意的一点是,HP4192A以幅度和角度报告阻抗。电容读数假定为简单的串联RC或并联RC,而运算放大器的输入阻抗可能要复杂得多。电容读数不应仅使用表面标称值。每个运算放大器均具有各自的独特情况。输入阻抗由容性电抗主导的频率范围可能因设计而异。输入级设计、所用器件和工艺、米勒效应以及封装都可能对差分输入阻抗及其测量产生很大的整体贡献。我们对JFET输入运算放大器和双极性输入运算放大器进行了测量,展示CDM结果以及双极性输入运算放大器的RDM结果。

责任编辑:haq

-

从零开始学运算放大器笔记一 | 认识运算放大器2025-03-24 5110

-

AN10-运算放大器建立时间的测量方法2021-04-27 881

-

硬件高手提升技能,解决运算放大器CDM难以测量问题2020-04-24 4013

-

运算放大器的测量方式简单介绍2019-07-22 2960

-

简简单单测量运算放大器2018-10-30 2216

-

运算放大器测试基础之电路测试主要运算放大器参数2018-09-07 3728

-

【转帖】运算放大器的简易测量2018-05-04 4230

-

运算放大器的使用方法及技巧2017-09-18 1120

-

实验七 集成运算放大器运用的测量2017-03-28 1175

-

运算放大器2014-04-23 5065

-

精确测量运算放大器性能的简易方法2012-03-09 1228

-

运算放大器的简易测量2011-10-23 4778

-

运算放大器,运算放大器是什么意思2010-03-09 4139

-

集成运算放大器的应用2008-08-04 1370

全部0条评论

快来发表一下你的评论吧 !