package里面有Cl元素,除了对hast有影响还有啥风险

描述

Q1

package里面有Cl元素,除了对hast有影响,还有啥风险?

A

如果是金线,HTST会失效,会快速加剧kirkendall void效应(卤素会跟kirkendall效应产生的某个金铝合金发生反应),之前有遇到case,GREEN的mold compound,供应商清线不干净,直接在含卤的线上做的,导致不管怎样,可靠性都过不了,后来分析成分和生产记录,发现异常。更换其他批次材料才解决。铜线或者合金线没有经历过,感觉也可能会有。

通常EMC里不允许超过20ppm的Cl,但是这个值是个燃烧法出来的平均值,如果正好有颗含cl的颗粒在铜球边上,这就会造成铜球IMC产生变化形成crack。产线上的Cl基本都是人体带来的,还有PVC。除此之外,有些Fab厂会用HCL来做线路刻蚀,如果清洁不干净就会有Cl的残留。

Q2

请问有没有人知道考虑SOC里面SRAM软失效时是按照SRAM加起来的容量考虑还是按照分开的容量?比如通常1Mb以上的SRAM要加ECC,那么如果是两块512Kb的SRAM要加ECC吗?可以认为是制程越先进,SER失效率越低吗?比如90nm比65nm的SRAM尺寸大一倍,所以同样容量的SRAM,65nm的FIT是90nm的一半SER FIT?

A

软失效率FIT在外部辐射的通量和能量固定的情况下,与SRAM的面积是成比例的,因此两块SRAM也要加。加或者不加应该取决于对芯片的稳定性要求。

在特定制程下,考虑到制程越先进,密度越高这个因素,还有辐射引起的电离特性,肯定不能拿不同制程的面积来算对应比例的FIT。现在季丰SER团队正在帮晶圆厂做28nm,14nm,7nm的SER对比实验。等做完实验,找一下对应关系。当前的判断是在不同制程下,肯定不会和面积成线性关系。

Q3

bonding如果不在无尘环境下,有什么风险?

A

灰尘引入,焊接困难,小停机多,影响焊接品质和OEE。万级问题不大。后面可以清洗。万级与十万级没有特别大差别。实际上国内的封装厂几年前没有一家在千级无尘室做WB的。千级无尘室没有地面架空做不到的。

Q4

芯片倒着切,有谁知道这个工艺吗?不是超薄片,目前担心水压造成芯片表面损伤,有人提出有反向切割,就是圆片在上面,刀具在下面的一种方式,所以在群里问问,是否有人做过这个。

A

对于芯片表面不能进水的芯片选择方法1)激光隐形切割2)图形芯片置于地面,SI面正面,刀片水切割;但是问题来了设备怎么识别切割道-一种切割设备影像识别部分升级或者SI面mark切割识别印记。以上二种方法能解决您的需求,因为没有规模化量产需求,实现成本都很高。

Q5

关于ESD HBM标准,JS-001 和 IEC61000-4-2,输出波形一样的吗?有啥区别?看标准,好像都是模拟人体静电放电的 HBM?

A

波形不一样,JS001是芯片级ESD,61000-4-2是系统级ESD。两者等效电路不同,波形参数上均不同。

都属于HBM,但芯片级是模拟人体直接接触芯片,系统级模拟的是终端产品抗静电能力,系统级更严苛。

Q6

陶瓷08b/08j的在季丰电子可以封装?金丝要求30微米以上的。

A

季丰可以做的。

Q7

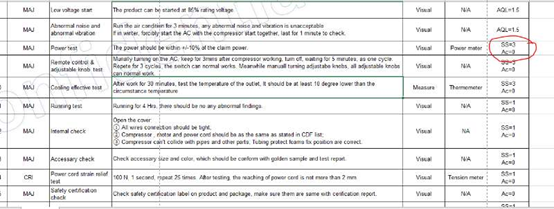

有谁知道这个SS=3 啥意思吗?

A

Sample Size。

Q8

这个是disco的部件,有知道是什么的吗?

A

Dressingtable,修整磨轮用的。

Q9

在FC封装时候,把die倾斜45度,这样做的技术成熟吗?不是Z方向,中间紫色的是FC DIE。图片如下所示:

A

这种没问题的。正封的时候,有45°封装的。倒装FC平面旋转45度也是可以做的。

Q10

请教下WLCSP 封测厂切换有什么可靠性影响吗?

A

需要重新做qual实验,facility change相当于重新走一遍流程。可以查看下图assembly site 对应的测试项目。

Q11

电源类产品一定要做HTRB吗?

A

HTRB是功率器件要的,比如MOST IGBT。IC不需要HTRB,是HAST,HTOL,TC等。

Q12

做过RDL的wafer,再做低温-40度会有风险吗?

A

RDL很常规,不影响可靠性。

Q13

你们做的RDL是在谁家做的?现在哪些封装厂提供RDL?6um的Cu线宽线距能做到20um以内吗?Cu下面垫的金属有要求吗?比如要求有多少层Al?或者Al的厚度?如果顶层Cu的话,是不是表面还要加一层polyimide?这样可靠性比较好?否则Cu是否有氧化问题?

A

长电、华天、通富、智芯集成。RDL很多Bumping house都可以做,关键是看RDL的尺寸要求,如线宽,间距,厚度。wafer fab做RDL用表面的铝层做,Bump house用Cu做。

可以的。现在10/10(线宽/间距)非常普通。最先进的是2/2。RDL下面垫有PI层,RDL是被PI层立体包围的,不会有氧化之风险。

Cu RDL下面有PI,有钝化层,一般对于金属即Top metal没有特殊需求。

Q14

请教一下,这个RDL是指顶层加厚铜还是厚铝?

A

通常是Cu RDL。

Q15

bump表面出现较多黑丝状物可能的原因是什么,会不会是出现了腐蚀现象?光刻胶的残留有没有常发生的位置呢?

A

边缘位置的最好在电镜下看一下,表面有异常元素,导致反应。有可能是F或Cl,金属颗粒大、光刻胶残留的可能性比较大,但不排除corrosion的可能,要确认是什么东西,只能SEM或光学显微镜下去看。

一般没有,要看 Ashing 前后的工序对不对 notch了。另外,也不一定是光刻胶残留,也可能是钝化层或刻蚀中间反应物的残留,要结合前后工序看。

Q16

CS测试是什么测试?

A

CS测试方法:https://re.sru.baidu.com/r/vUCkjRagSc?f=wf&u=7577c3cbc4a367a1。

编辑:jq

-

请问Systemverilog中如何使用VHDL的package?2024-03-12 1170

-

双851000h(THB)和HAST96h实验,谁的实验理论寿命更长?2025-04-01 959

-

请问OSA里面有sem pipe mutex是什么?OSA是什么?2018-05-25 2515

-

请问瑞萨芯片里面有DMA 吗?2018-07-23 2987

-

请问STM32的中断里面有的标志都有什么用?2019-07-17 2409

-

请问proteus里面有现成的光电开关么?2020-04-28 4306

-

THB与HAST如何选择?2022-09-13 13876

-

小垫圈,里面还有这么多名堂……2019-07-02 3870

-

Taycan里面有个48V系统电压的原因2020-10-10 4863

-

Hast老化试验测试2024-03-13 650

-

数据分析除了spss还有什么2024-07-05 1990

-

什么是芯片的HAST测试?2024-12-16 2593

-

可靠性测试:HAST与PCT的区别2024-12-27 2095

-

洗衣机变频电机和伺服电机哪个里面有磁铁?2026-01-09 734

全部0条评论

快来发表一下你的评论吧 !