FPGA设计的高速FIFO电路技术

FPGA/ASIC技术

描述

FPGA设计的高速FIFO电路技术

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量高速采集系统项目的开发过程中,FPGA作为可编程逻辑器件,设计灵活、可操作性强,是高速数字电路设计的核心器件。由于FPGA内嵌存储器的容量有限,通常不能够满足实际设计电路的需求,需要外接SRAM、SDRAM、磁盘阵列等大容量存储设备。

A/D输出的数据流速度快,经过FPGA降速后,位数宽,速度仍然很高,不能直接存储到外部存储器。在设计时,要经过FIFO缓存,然后才能存储到外部存储器。本设计的FIFO容量小、功能强,充分利用了FPGA内部FIFO电路的特点,结合实际电路,优化了整个电路模型的设计。

异步FIFO生成

FIFO占用的内存资源为FPGA内嵌的block RAM,由Xilinx公司提供的ISE开发平台自动生成。读写时钟有通用时钟和独立时钟可选,我们采用独立时钟,rd_clk和wr_clk独立,为了保证在高速采集时数据不丢失,rd_clk频率不低于wr_clk。FIFO读模式采用标准FIFO,每次启动采集时都要对FIFO进行复位,为异步复位,初始化内部指针和输出寄存器。在FIFO生成过程中,我们启用almost_full 和almost_empty选项,以及prog_full 和prog_empty选项,prog_full和prog_empty要进行参数设置,具体设置参数如图2所示。

FIFO接口信号定义

根据FIFO的生成过程,在图3中给出了读写时钟域的信号定义,所有的在写时钟域的输入信号都必须经过写时钟同步,所有的在读时钟域的输入信号都要经过读时钟同步。信号经过时钟同步后,可以确保在读写过程中不会出现亚稳态,导致读写操作出现错误。

下面对读写时钟域定义信号给予说明:

rst:复位信号,高有效,异步复位,每次启动采集都要首先对FIFO进行复位;

wr_clk:写时钟;

wr_en:与写时钟同步;

din:输入数据总线;

rd_clk:读时钟;

dout:输出数据总线;

full:FIFO全满标志;

empty:FIFO全空标志;

almost_full:高有效,如果为高电平,在写一个数据FIFO将全满;

almost_empty:高有效,如果为高电平,在读一个数据FIFO将全空;

prog_full:可编程满标志,根据需要,可以设定FIFO内部有多少数据,该标志信号有效;

prog_empty:可编程空标志,根据需要,可以设定FIFO内部有多少数据,该标志信号有效;

wr_data_count:说明FIFO内部已经写了多少数据;

rd_data_count:说明FIFO内部有多少数据可以读。

FIFO控制电路设计

实际电路设计不考虑读写时钟的频率和相位的异同,读写时钟域的电路基于同步电路设计的理念来进行设计,在设计过程中,满足读时钟频率不低于写时钟频率即可。在图4中给出了FIFO控制电路的流程图,下面将对低速传输和高速传输进行详细介绍。

低速采集数据传输过程

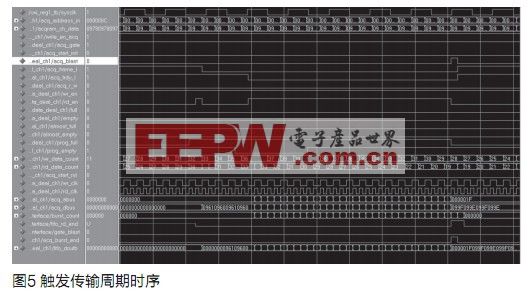

在图5给出了低速采集时传输周期时序仿真时序图,在低速采集时,写时钟频率小于读时钟,每次触发长度为FIFO长度的一半。采集结束即剩余数据传输的长度不到FIFO的一半。根据prog_full的设置,在prog_full有效,同时采集门控信号有效时启动触发请求,由于prog_full为写时钟域信号,必须要经过rd_clk同步,源代码如下:

process(rd_clk,acq_start_rst)

begin

if acq_start_rst=’1’then

prog_full_dly<=’0’;

prog_full_dly1<=’0’;

elsif rd_clk’event and rd_clk=’1’

then

if acq_gate= ’1’ then

prog_full_dly<=prog_full;

prog_full_dly1<=prog_

full_dly;

else

prog_full_dly<=’0’;

prog_full_dly1<=’0’;

end if;

end if;

end process;

当FIFO半满时触发读请求有效,acq_frame_l为低电平,启动采集数据传输请求,地址和数据同时有效,sdram控制器给出应答信号acq_trdy_l,长度由FIFO读写控制电路决定,触发一次的长度为32,即FIFO半满的长度,传输完毕,给出传输结束标志信号acq_blast,一次传输周期结束。采集门控信号结束后,FIFO剩余数据长度不足32,这时候启动门控结束传递进程,触发结束标志由almost_empty决定,当alomost_empty有效时,停止触发。

高速采集数据传输过程

在高速采集时,读时钟频率等于写时钟频率,当启动触发传输时,触发传输长度为门控信号长度,直到将FIFO内部数据传输完毕,触发结束标志由almost_empty决定,当alomost_empty有效时,停止触发传输,触发传输过程如图6所示。

结语

采用高速异步FIFO作为数据采集缓存,应用范围十分广泛。特别是在高速数据采集系统中,在外接存储器时,采集数据首先要经过缓存才能存入外部存储器,采用FPGA自生成FIFO就能够满足要求。本方案充分利用FIFO的特点,通过控制电路优化设计,解决了读写时钟的异同问题,提高了电路的工作效率。

参考文献:

[1] John F W. 数字设计原理与实践[M]. 北京:机械工业出版社, 2003

[2] 候伯亨, 顾新. VHDL硬件描述语言与电路设计[M]. 西安:西安电子科技大学出版社, 1997

[3] Virtex-5 FPGA User Guide, Xilinx

[4] 雷海卫, 刘俊. FPGA中软FIFO的设计与实现[J]. 微计算机信息, 2008,24(2):207-209

[5] 于海, 樊晓桠. 基于FPGA异步FIFO的研究与实现[J]. 微电子学与计算机, 2007,24(3):210-216

-

FPGA学习-基于FIFO的行缓存结构2022-05-10 4995

-

如何在Altera FPGA中使用FIFO实现功能设计?2021-03-12 4283

-

FPGA电路FIFO设计的源代码2020-07-08 1058

-

基于FPGA的异步FIFO设计方法详解2018-07-17 8980

-

基于FPGA片上集成的高速FIFO实现缓存以及同步数据传输的应用2018-07-12 6171

-

异步FIFO在FPGA与DSP通信中的应用解析2017-10-30 1777

-

基于FIFO的高速A_D和DSP接口设计2017-10-19 804

-

FPGA与DSPs高速互联的方案2017-02-11 3006

-

异步FIFO在FPGA与DSP通信中的运用2011-12-12 952

-

LabVIEW FPGA模块实现FIFO深度设定2011-09-26 8158

-

高速异步FIFO的设计与实现2010-01-13 677

-

基于FPGA的FIFO设计和应用2009-11-20 2439

-

异步FIFO结构及FPGA设计2009-04-16 791

全部0条评论

快来发表一下你的评论吧 !